Local medium thickening method for improving silicon integrated inductance quality factor

A technology integrating inductance and quality factor, which is applied in the direction of circuits, electrical components, fixed transformers or mutual inductance, and can solve problems such as complex processes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The present invention is a local medium thickening method for improving the quality factor of silicon integrated inductance, comprising the following steps:

[0017] Step 1: Deposit silicon dioxide / silicon nitride / silicon dioxide three-layer composite dielectric; this step 1 uses the deposition method to grow silicon dioxide / silicon nitride / silicon dioxide three-layer composite dielectric, and the three-layer dielectric The thickness ranges are 15-30nm, 50-100nm, 500-3000nm in turn.

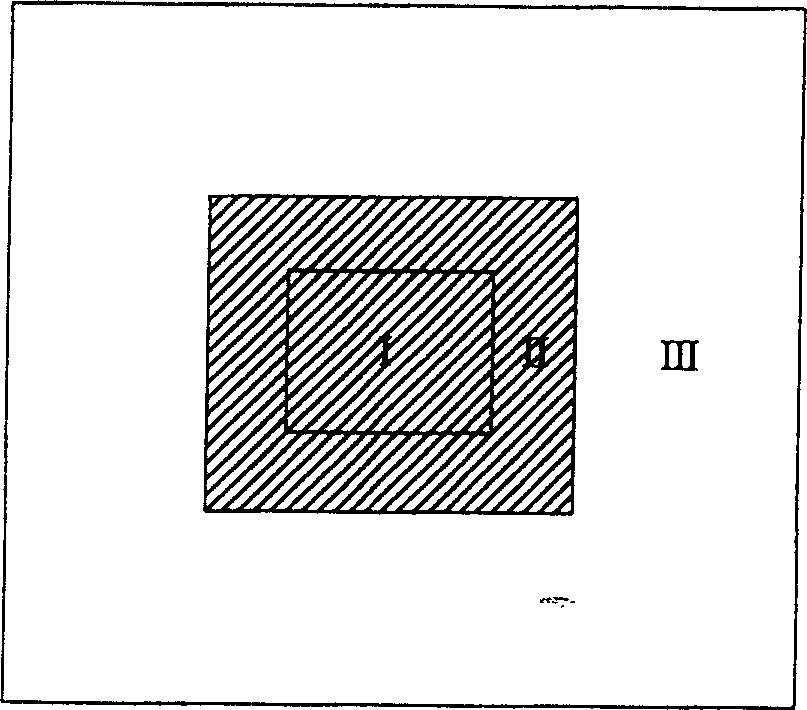

[0018] Step 2: The photoresist protects the area of the spiral inductor and exposes the area outside the plane of the spiral inductor; this step 2 uses the photoresist to protect the planar spiral inductor and the area within 5 microns around it; as figure 1 As shown, area I (the rectangle with the smallest area in the center of the figure) is the planar area of the spiral inductor, area II (the shaded area, including area I) is the photoresist protection area, and area III (the area o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com