Tightly coupled and scalable memory and execution unit architecture

a memory and execution unit technology, applied in the field of tightly coupled and scalable memory and execution unit architecture, can solve the problem that data transfer at the memory interface remains a relative bottleneck, and achieve the effect of improving the efficiency of operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

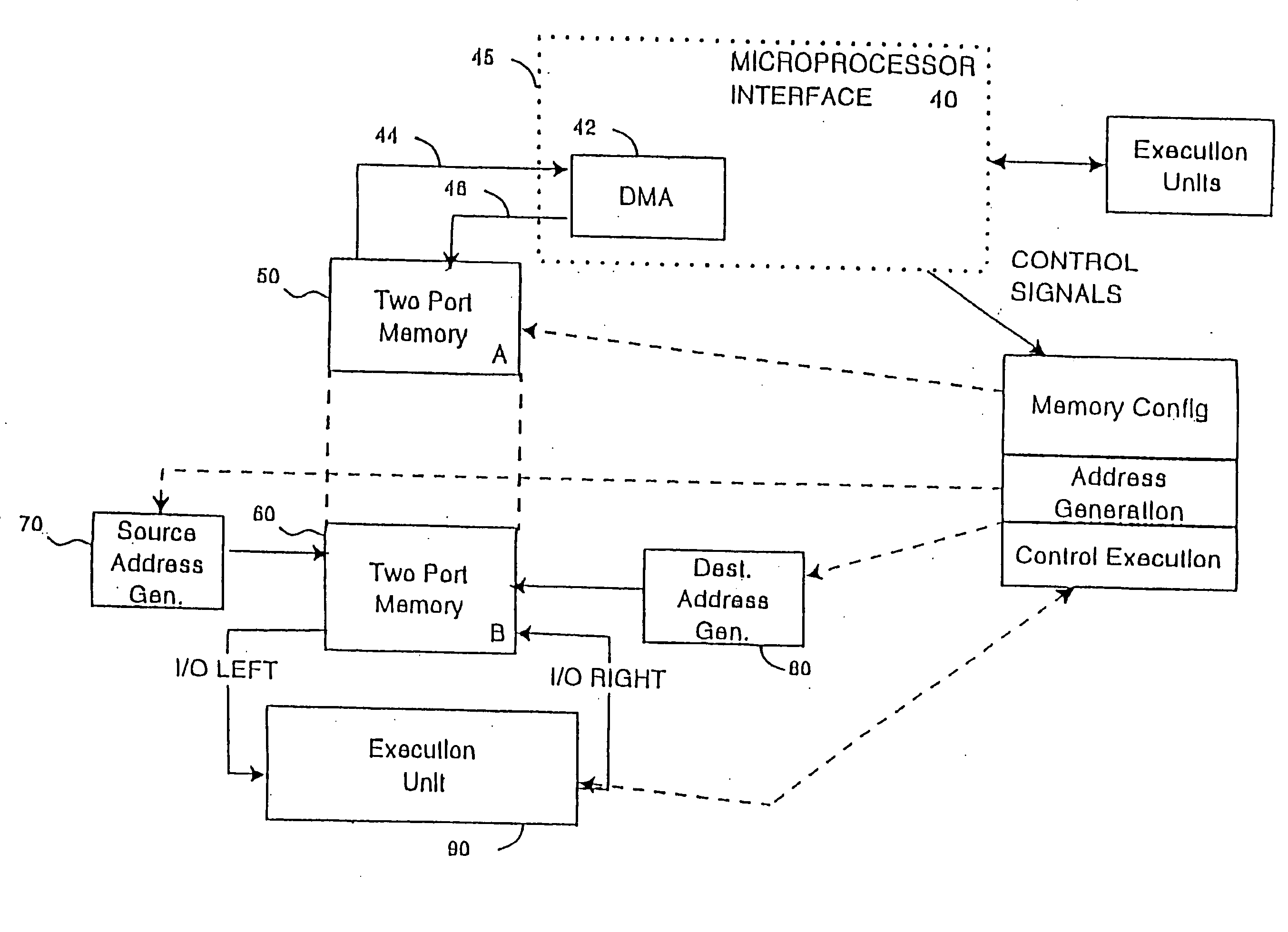

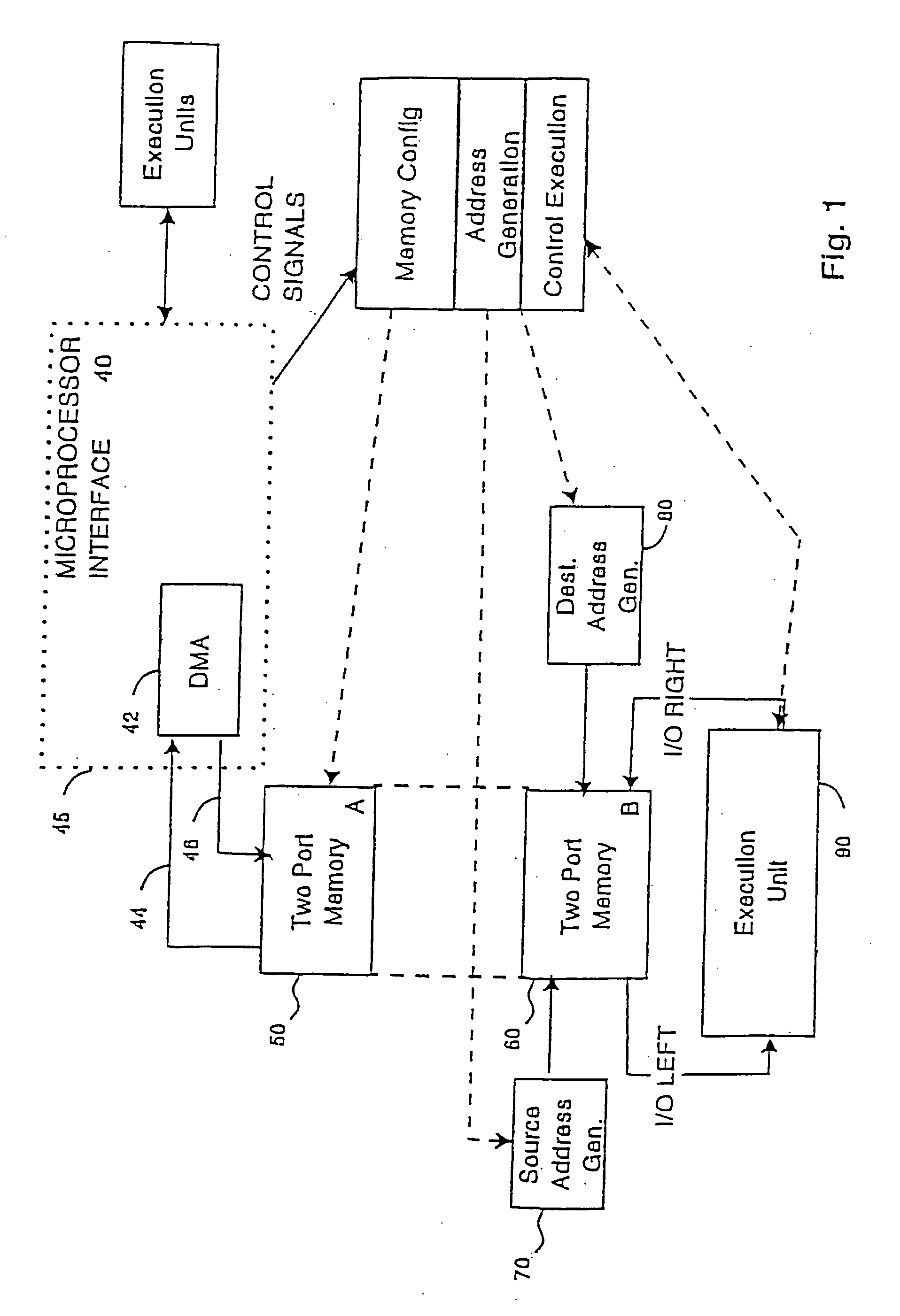

FIG. 1

[0073]FIG. 1 is a system-level block diagram of an architecture for memory and computing-intensive applications such as digital signal processing. In FIG. 1, a microprocessor interface 40 includes a DMA port 42 for moving data into a memory via path 46 and reading data from the memory via path 44. Alternatively, a single, bi-directional port could be used. The microprocessor interface 40 generically represents an interface to any type of controller or microprocessor. The interface partition indicated by the dashed line 45 in FIG. 1 may be a physical partition, where the microprocessor is in a separate integrated circuit, or it can merely indicate a functional partition in an implementation in which all of the memory and circuitry represented in the diagram of FIG. 1 is implemented on board a single integrated circuit. Other types of partitioning, use of hybrid circuits, etc., can be used. The microprocessor interface (DMA 42) also includes control signals indicated at 52. The ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More