MIM capacitor integrated into the damascene structure and method of making thereof

a technology of damascene and capacitors, which is applied in the direction of capacitors, semiconductor devices, semiconductor/solid-state device details, etc., can solve the problems of unacceptably high leakage current in integrated circuits, increased die size, chip and assembly cost, and relatively small parasitic resistance of conventional mim capacitors, etc., to achieve the effect of reducing fabrication costs and sacrificing capacitor density or performan

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The making and using of the presently preferred embodiments are discussed in detail below. It should be appreciated, however, that the present invention provides many applicable inventive concepts that can be embodied in a wide variety of specific contexts. The specific embodiments discussed are merely illustrative of specific ways to make and use the invention, and do not limit the scope of the invention. The present invention will be described with respect to preferred embodiments in a specific context, namely a copper damascene interconnect process.

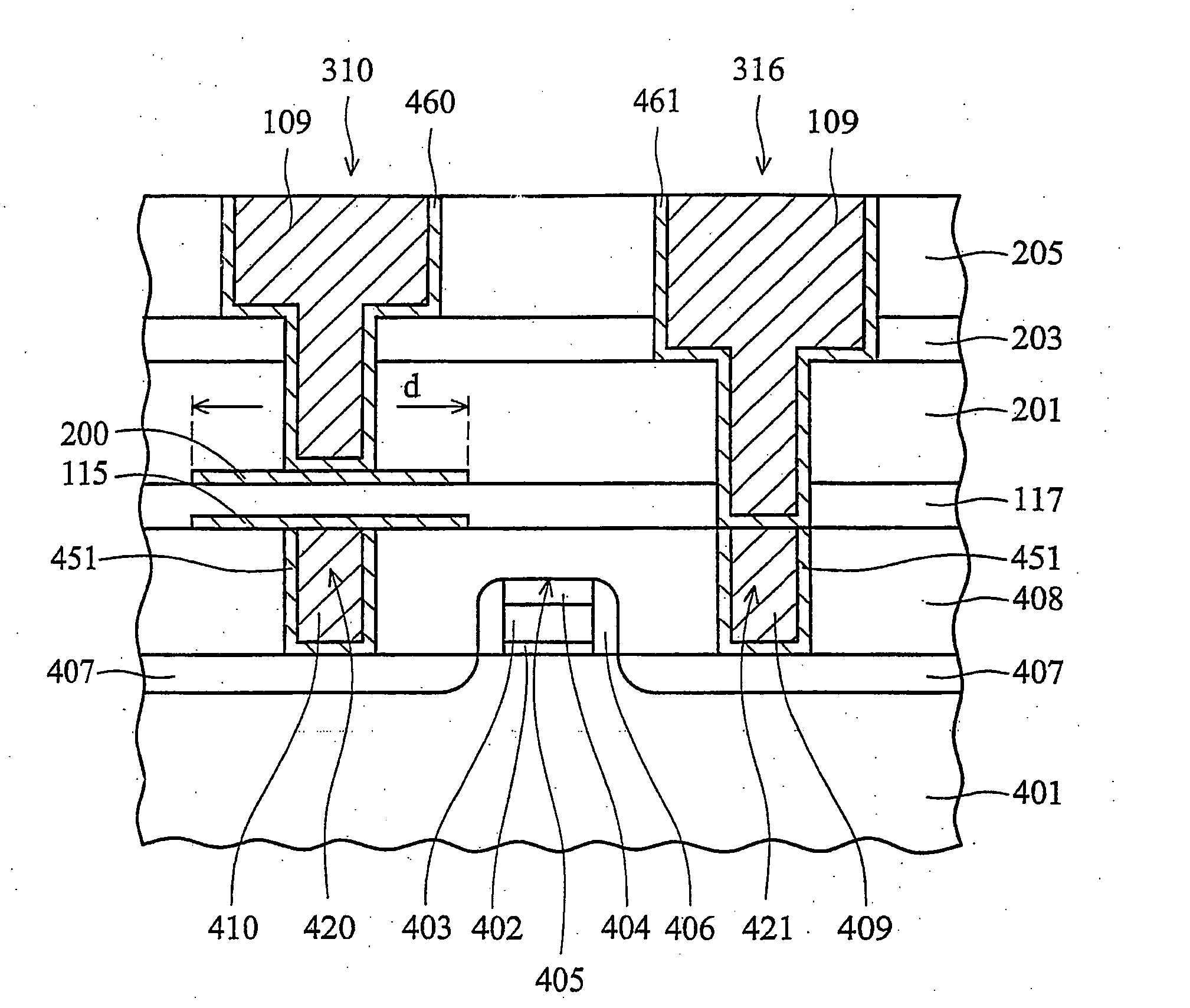

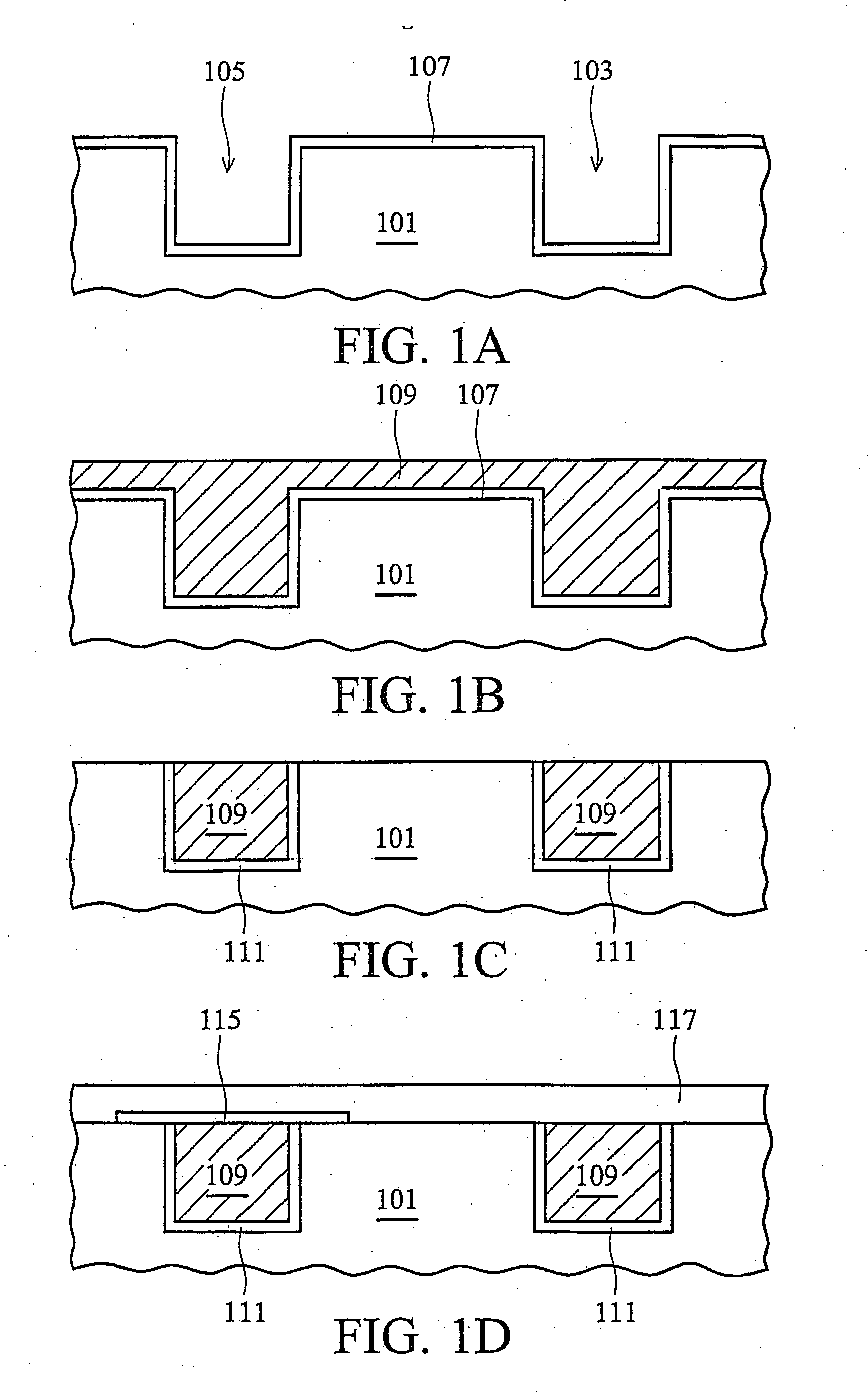

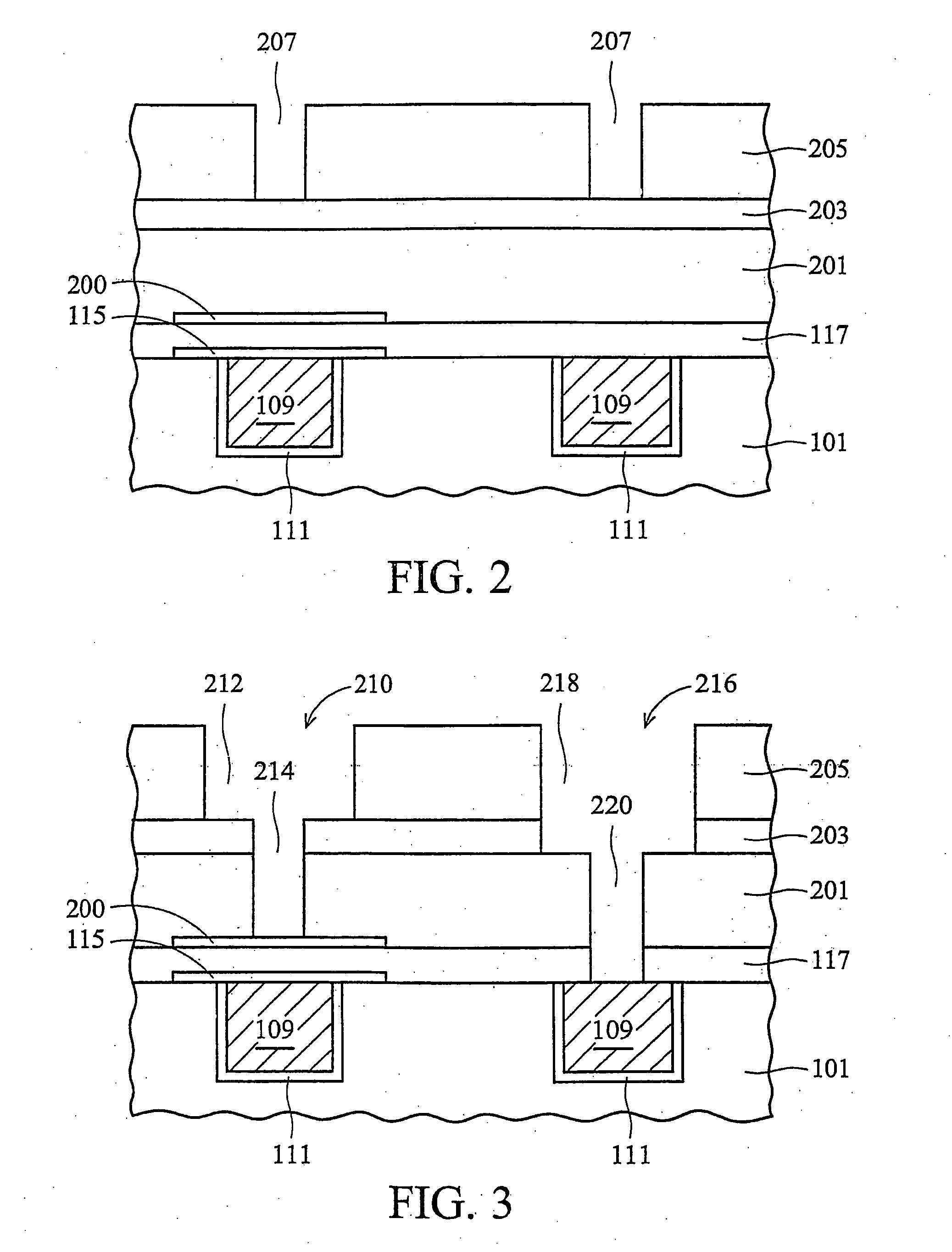

[0023] Turning now to FIGS. 1A through 1D, these figures are cross-sectional views of an embodiment of the present invention illustrating an intermediate semiconductor device and the formation of the first or bottom capacitor electrode as described below. FIG. 1A depicts a cross sectional view of an integrated circuit at an intermediate fabrication stage. Shown in FIG. 1A is a conventional substrate 101, which comprises as a si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More