Integrated parallel plate capacitors

a parallel plate capacitor and integrated technology, applied in capacitors, semiconductor devices, semiconductor/solid-state device details, etc., can solve the problems of limited performance of vpp capacitors, extra wafer processing costs of about $25/wafer, etc., to reduce/eliminate additional wiring area, increase capacitance coupling, and improve capacitance density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

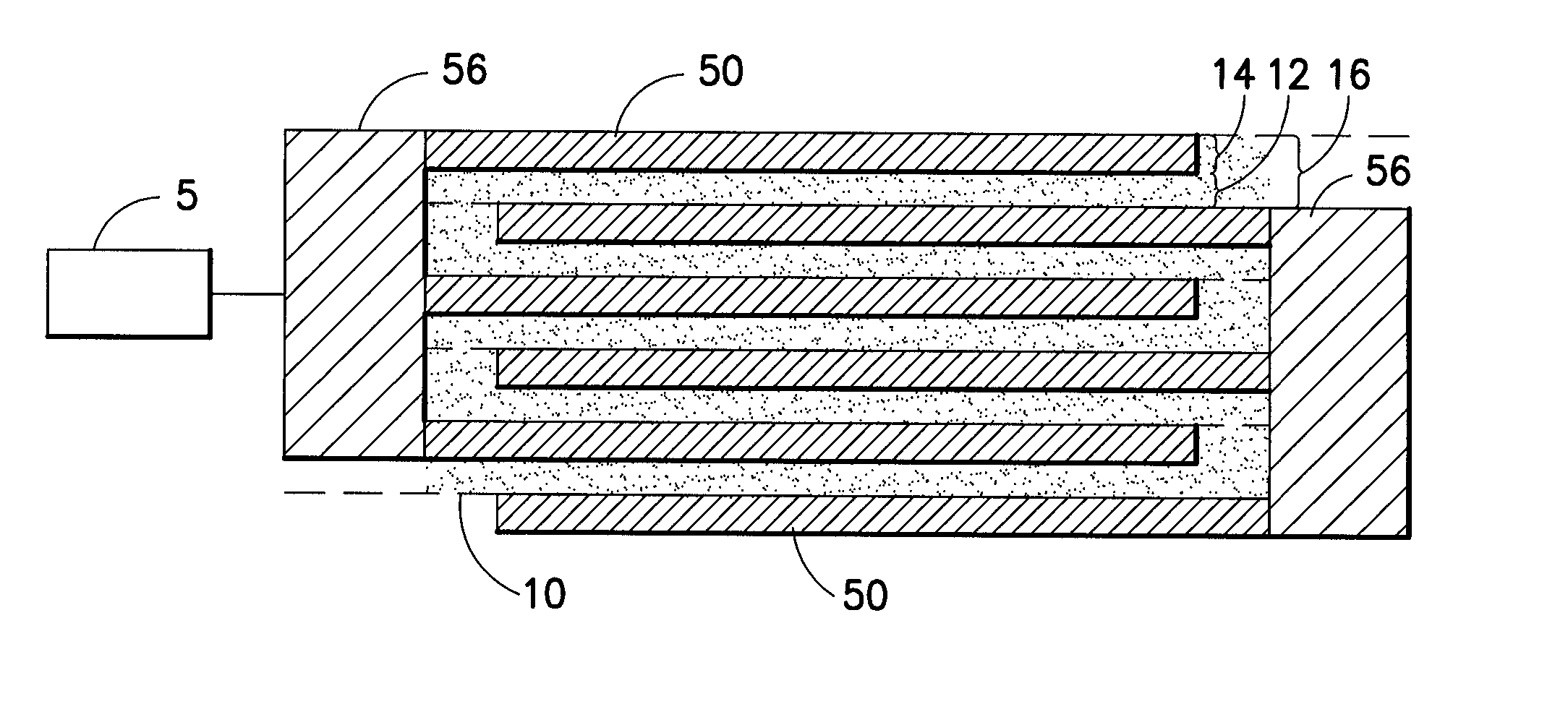

[0016]FIG. 1 shows a set of solid plates 50 connected alternately by vertical connection bars 56. An important feature of this structure compared with prior MIM capacitors is that the thickness 12 of the dielectric between the plates is greater than before because the thickness 12 is the thickness 16 of the back end levels minus the thickness 14 of the interconnects on that back end level; e.g. if the total thickness of the level is 0.5 microns and the thickness of the interconnect on that level is 0.25 microns, then the thickness 12 of the dielectric is also 0.25 microns. Dashed line 10 indicates the top surface of a layer in the back end. A level in the back end containing a capacitor plate will be referred to as a capacitor level. The foregoing means that the capacitance per unit area (capacitance density) is reduced, but that is more than compensated for by the improved reliability provided by the invention. Box 5 represents schematically interconnections on the levels of the BE...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More