Thin film transistor of multi-grid structure and manufacturing method thereof

A technology of thin-film transistors and manufacturing methods, which is applied in the field of thin-film transistor array substrates, and can solve problems such as LDD region position offset, difficult control, and electrical asymmetry of transistors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

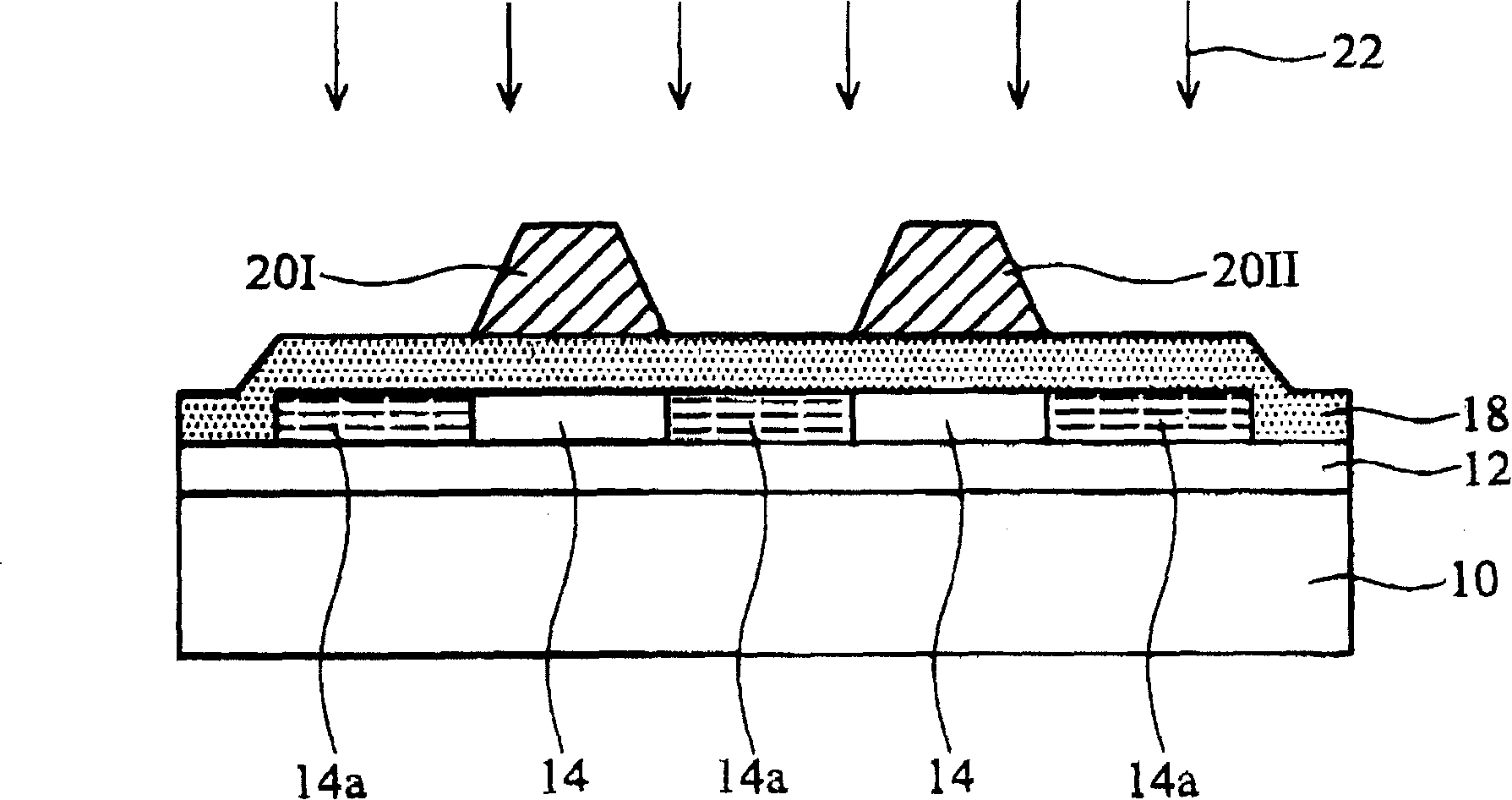

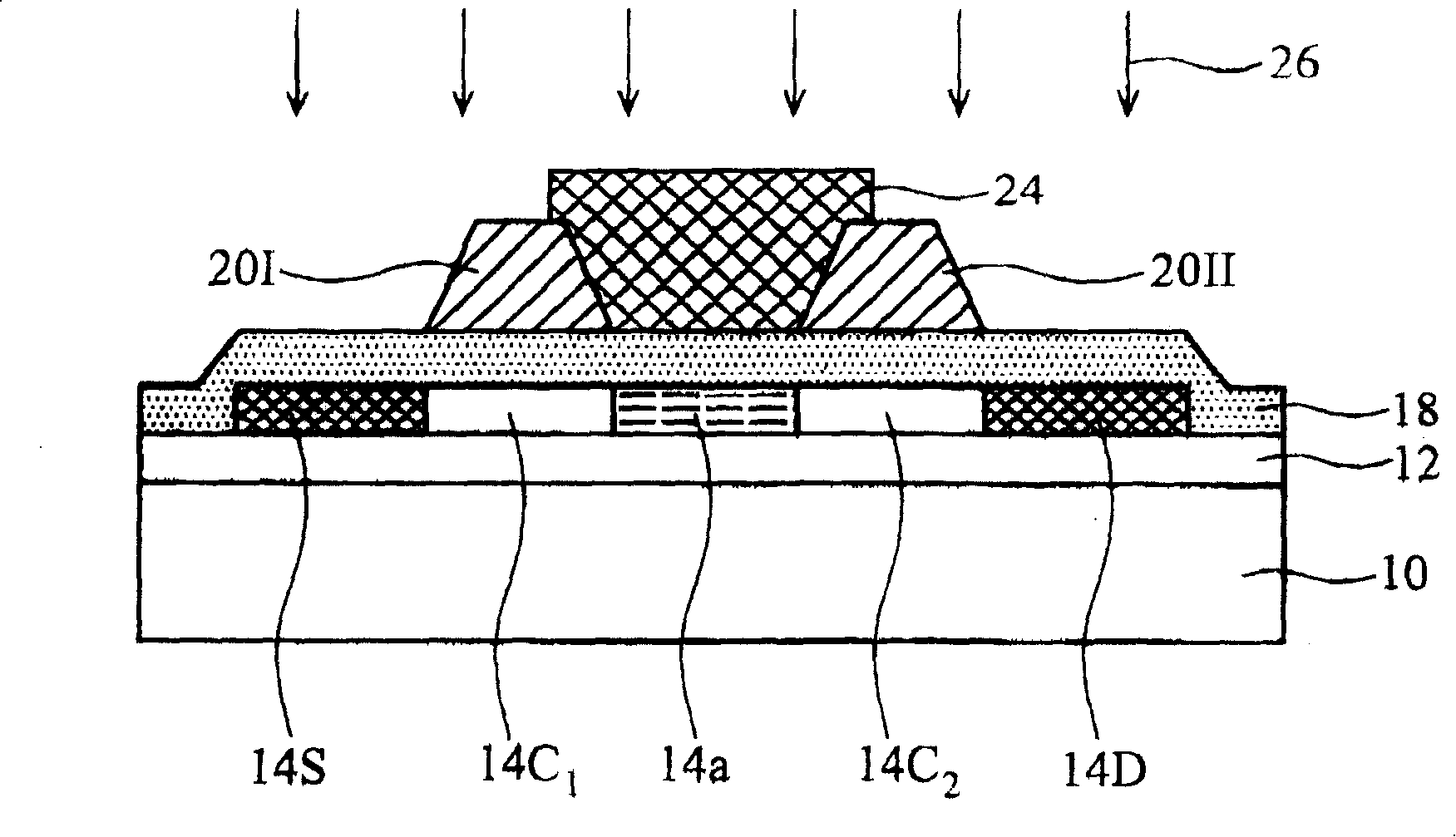

[0053] see Figure 2A to Figure 2E , which shows a schematic cross-sectional view of a method for fabricating a polysilicon TFT with a double-gate structure according to the first embodiment of the present invention.

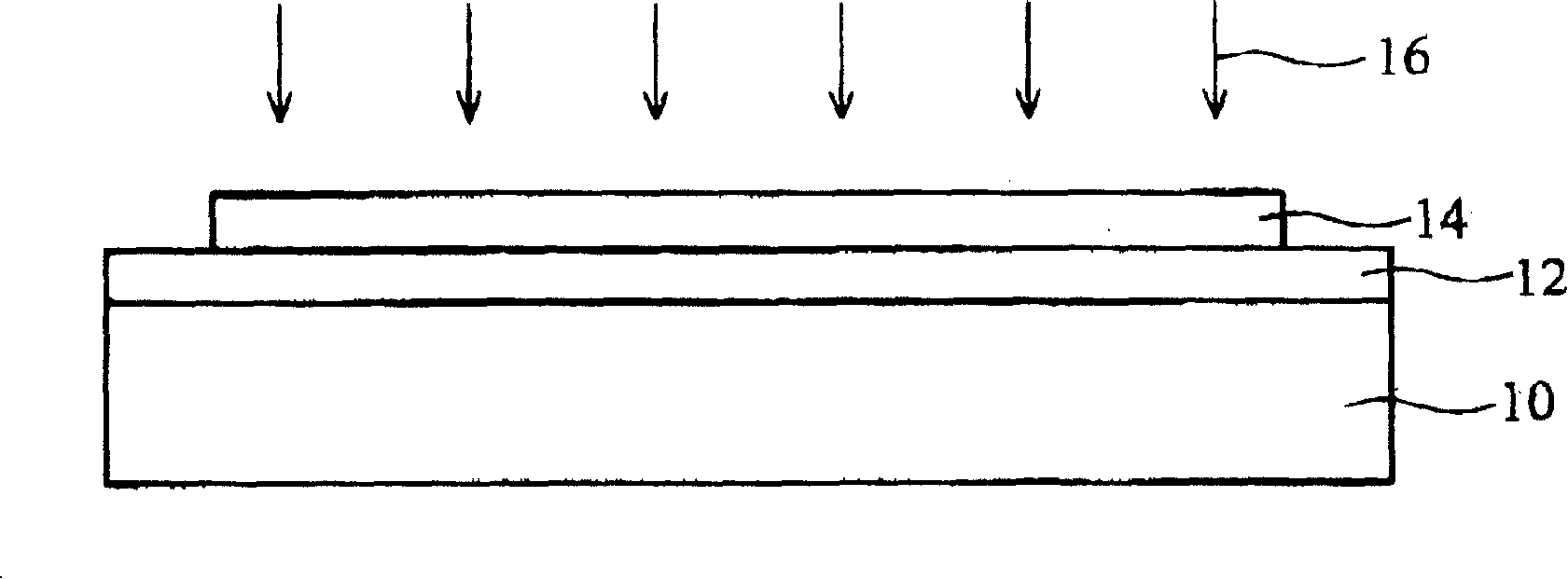

[0054] First, if Figure 2A As shown, a substrate 30 is provided, and a buffer layer 32 and an effective layer 34 are sequentially fabricated on the substrate 30 . The substrate 30 is preferably a transparent insulating substrate, such as a glass substrate. The buffer layer 32 is preferably a dielectric material layer, such as a silicon oxide layer, and its purpose is to help the effective layer 34 to be formed on the substrate 30 . The effective layer 34 is preferably a semiconductor silicon layer, such as a polysilicon layer. In order to adjust the threshold voltage of the transistor, a boron or phosphorus ion implantation (B + or P + ion implantation) process.

[0055] Then, if Figure 2B As shown, an insulating layer 36 and a conductive layer 38 are s...

no. 2 example

[0070] see image 3 , which shows a schematic cross-sectional view of a polysilicon TFT with a double gate structure according to the second embodiment of the present invention. The structural features of the thin film transistor in the second embodiment are substantially the same as those described in the first embodiment, and the similarities will not be described again. The difference is that the first gate insulating layer 40 additionally includes an extension region 40c, which is the first shielding region 40b 1 and extend to cover the seventh region 347 of the effective layer 34 . It is characterized in that the thickness of the extension region 40c is much smaller than that of the first shielding region 40b 1 The thickness will not affect the fabrication of the LDD region and the source / drain region. Similarly, the second gate insulating layer 42 additionally includes an extension region 42c, which is a second shielding region 42b 2 and extend to cover the eighth re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More