Metal oxide semiconductor device grid preparation method

A technology of oxide semiconductor and manufacturing method, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as thinning, polysilicon layer damage thickness, etc., to improve reliability, reduce thermal budget, reduce damage effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

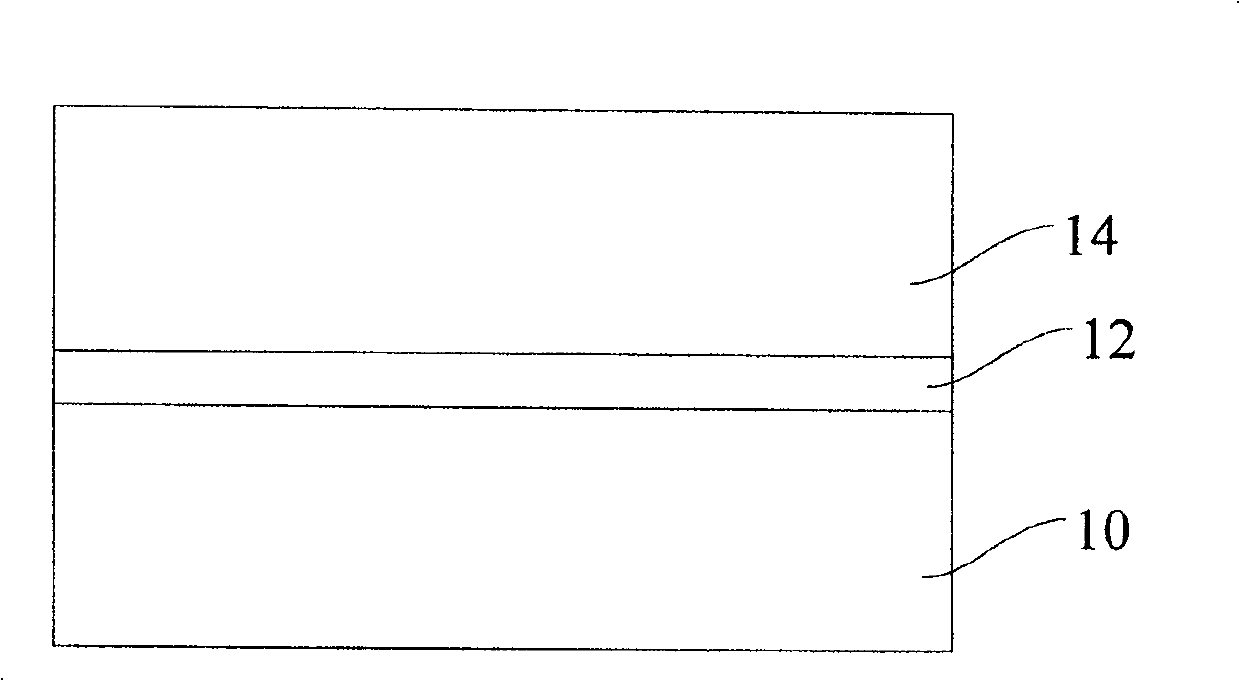

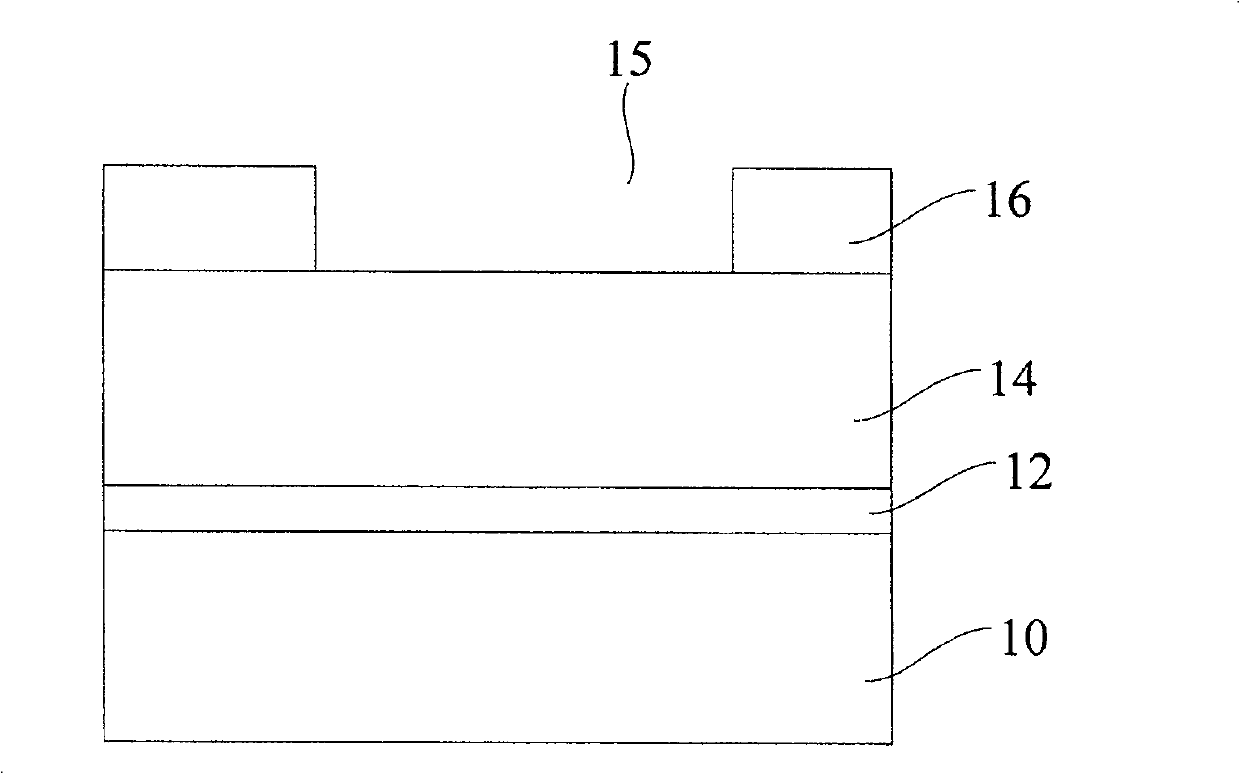

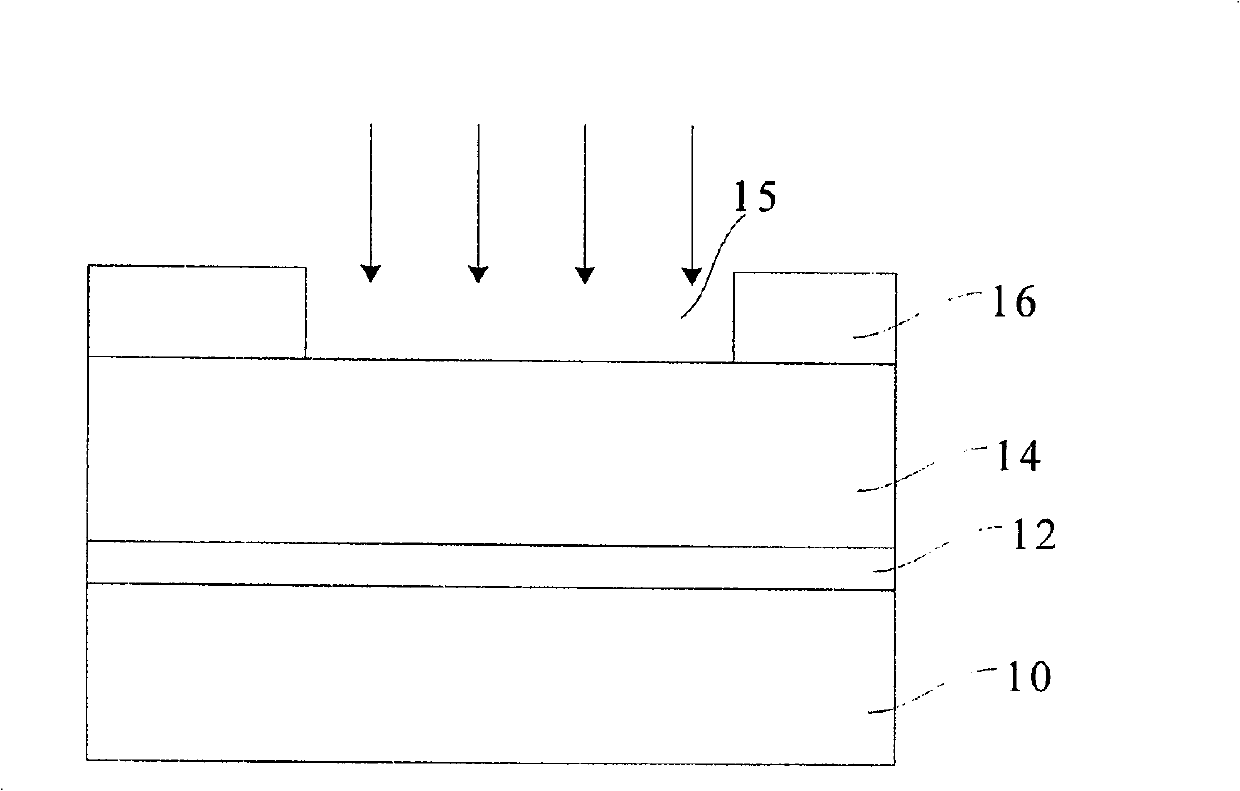

[0030] Figure 6 It is a flowchart of an embodiment of a method for manufacturing a metal oxide semiconductor device gate according to the present invention. Such as Figure 6 As shown, firstly, a semiconductor substrate is provided, and the semiconductor substrate is one of polycrystalline silicon, single crystal silicon, amorphous silicon, silicon-on-insulator, silicon-germanium composition, and gallium arsenide. Doping N-type impurities or P-type impurities into the semiconductor substrate to form a conductive channel of the device. The surface of the semiconductor substrate has a thin oxide layer, the thickness of the oxide layer is 1 to 100 nm, and the formation method of the oxide layer is high temperature thermal oxidation or ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More