Semiconductor device and its making method

A manufacturing method, semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, transistors, etc., which can solve the problems of recession, silicide and oxide loss, hot carrier lifetime and negative bias temperature instability, etc. Achieve the effects of adjustable stress size, low dielectric constant, and simplified contact hole etching process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

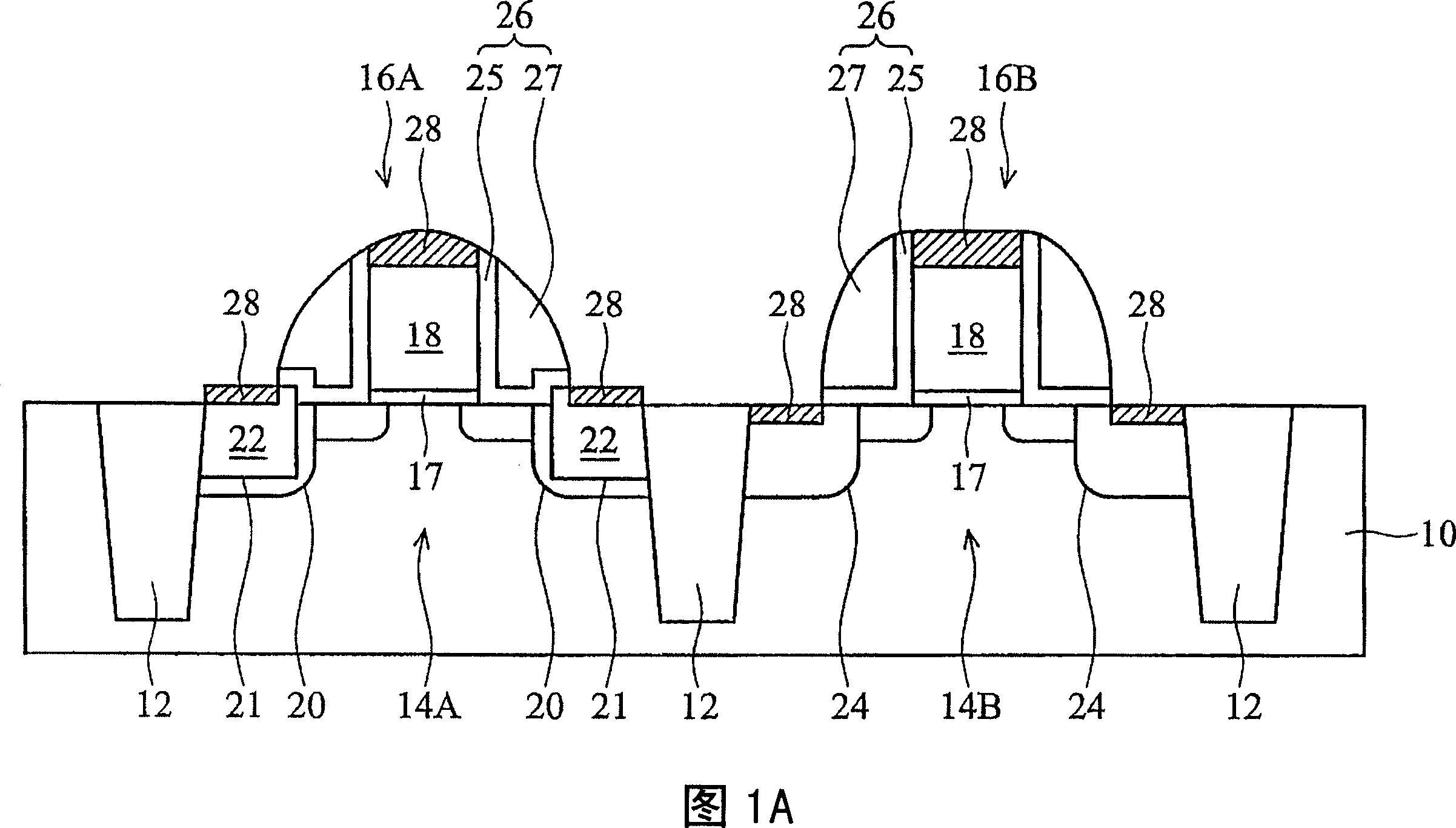

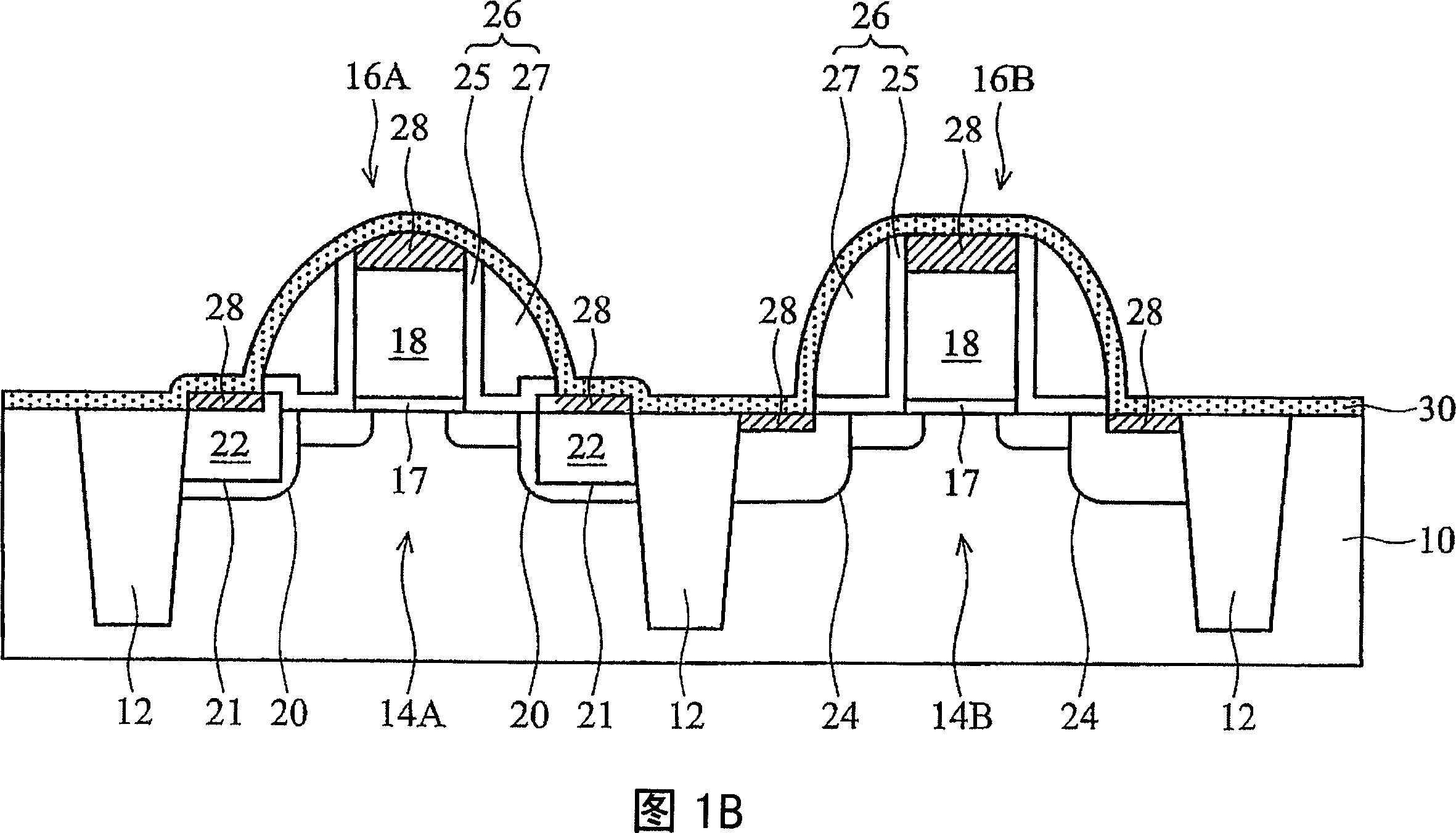

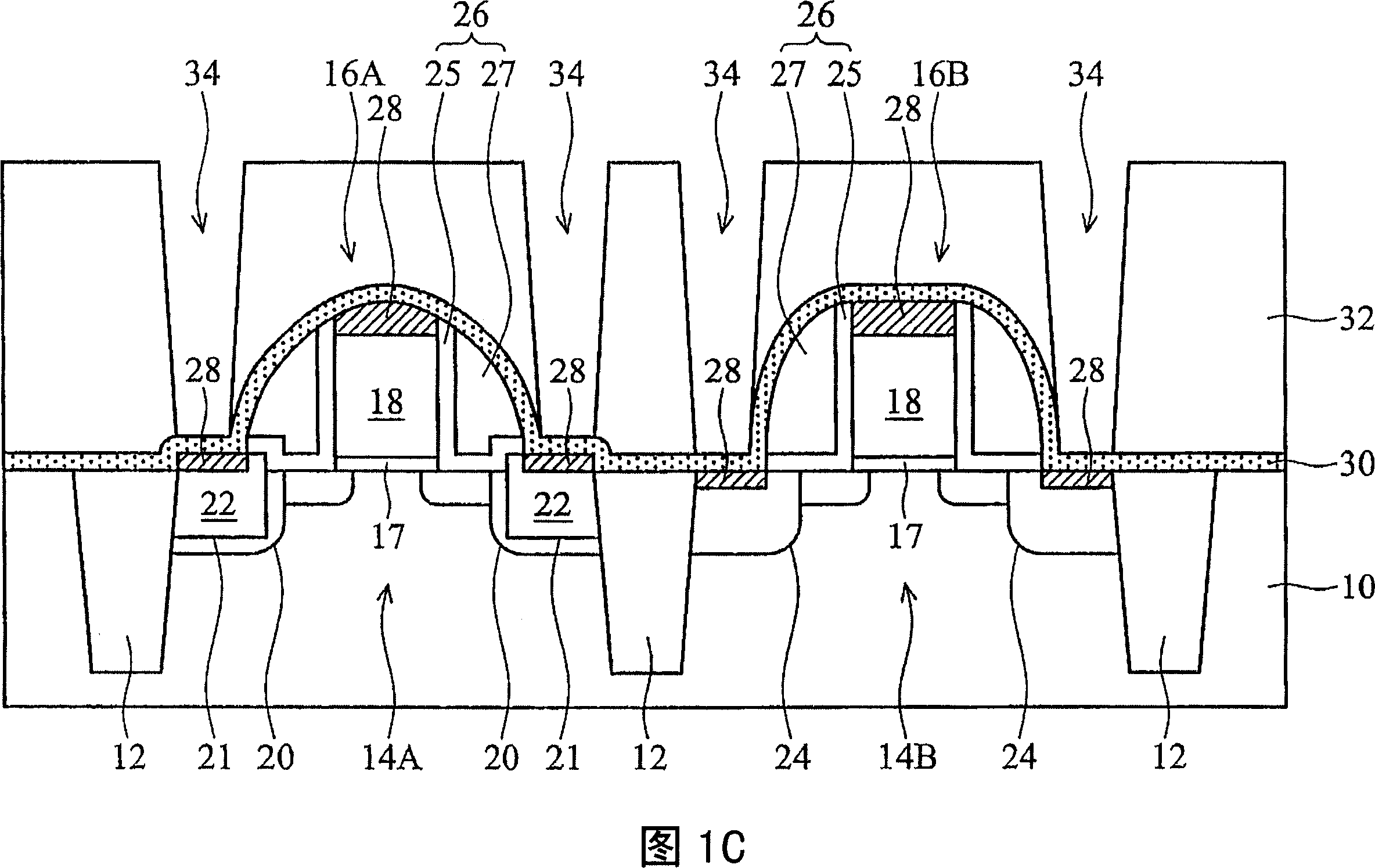

[0043] Embodiments of the present invention provide a strain-enhanced CMOS device and a manufacturing method thereof, in order to use an amorphous carbon film as a stress covering film to solve the problem of using Si in the known technology. 3 N 4 Problems caused by cover film. Amorphous carbon films, such as fluorine-doped amorphous carbon films, are materials formed using low-temperature deposition processes, such as chemical vapor deposition or physical vapor deposition. Amorphous carbon has a rather low dielectric constant. Taking fluorine-doped amorphous carbon as an example, its dielectric constant is lower than about 2.8. The amorphous carbon film can be formed into a tensile stress film or a compressive stress film by different deposition parameters (such as energy, temperature, etc.), as a stress covering film, which can be selectively formed in the PMOS device area or the NMOS device area. Since the amorphous carbon film has a high etch selectivity relative to ox...

PUM

| Property | Measurement | Unit |

|---|---|---|

| tensile stress | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| compressive stress | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More