High-pressure resistant silicon carbide light guide switch

A high withstand voltage silicon carbide and photoconductive switch technology, which is applied in semiconductor devices, electrical components, circuits, etc., to achieve the effects of high withstand voltage structure, simple structure design, and improved compressive strength

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

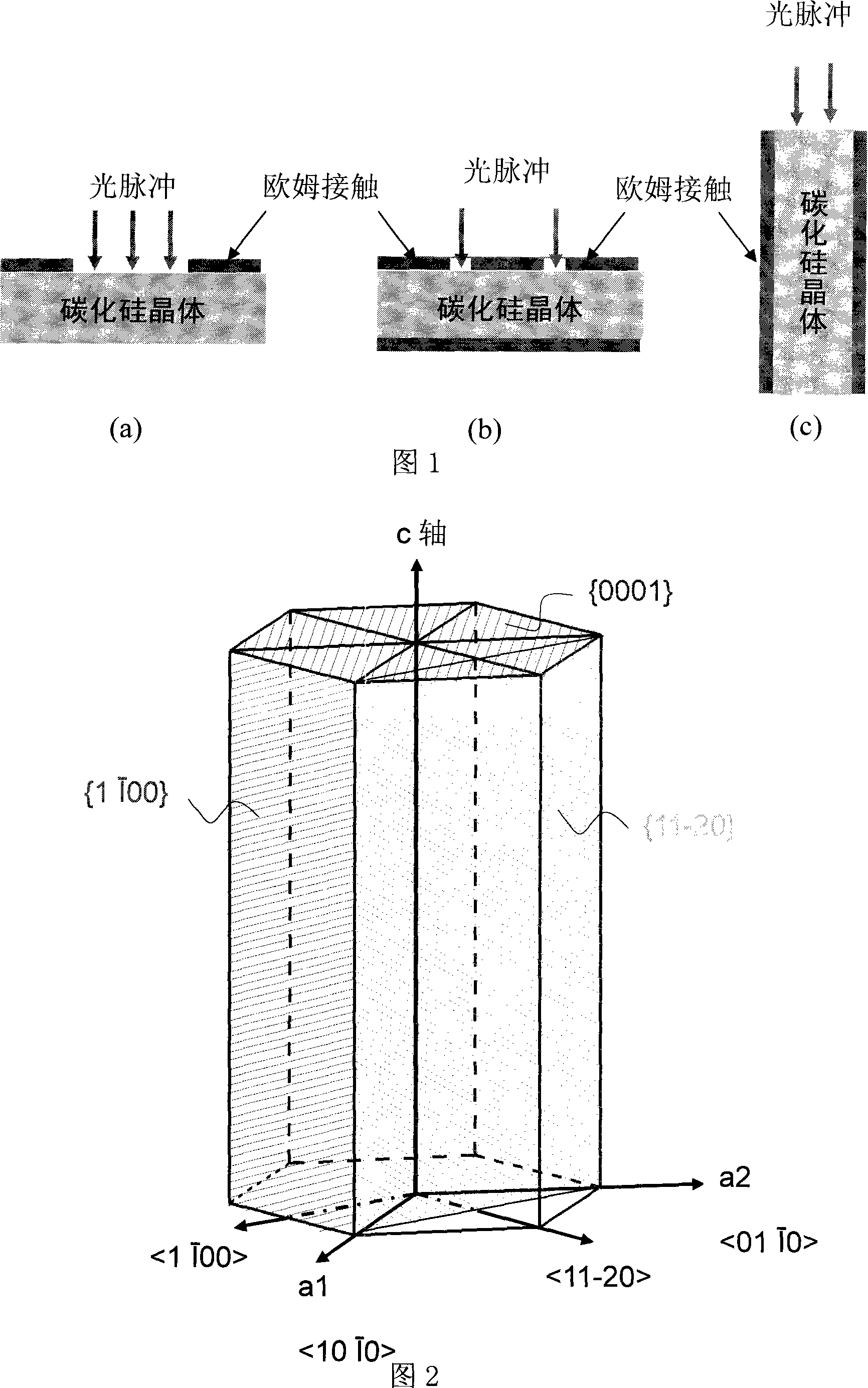

[0030] Opposite-plane photoconductive switch obtained by using (0001) plane semi-insulating SiC crystal.

[0031] The wafer used in the SiC photoconductive switch is a semi-insulating 6H-SiC crystal obtained by doping vanadium. The wafer sample is cut along the direction perpendicular to the c-axis of the crystal. The crystal plane is (0001). mm×10.0mm, the surface roughness Ra of the crystal detected by AFM is less than 0.5nm. In order to remove the surface oxide layer and the sub-damaged layer formed during processing, and passivate the wafer surface, the SiC wafer was annealed at 1000°C for 15 hours, then immersed in 200°C molten KOH solution for 3min etching, and finally Soak it in dilute HF for 12 hours, and then clean it according to the RCA process, so as to prepare for the production of device electrodes.

[0032] The device fabricated in the experiment adopts the opposite surface electrode structure, the electrode is square, the side length is 3.5mm, and the vertical...

Embodiment 2

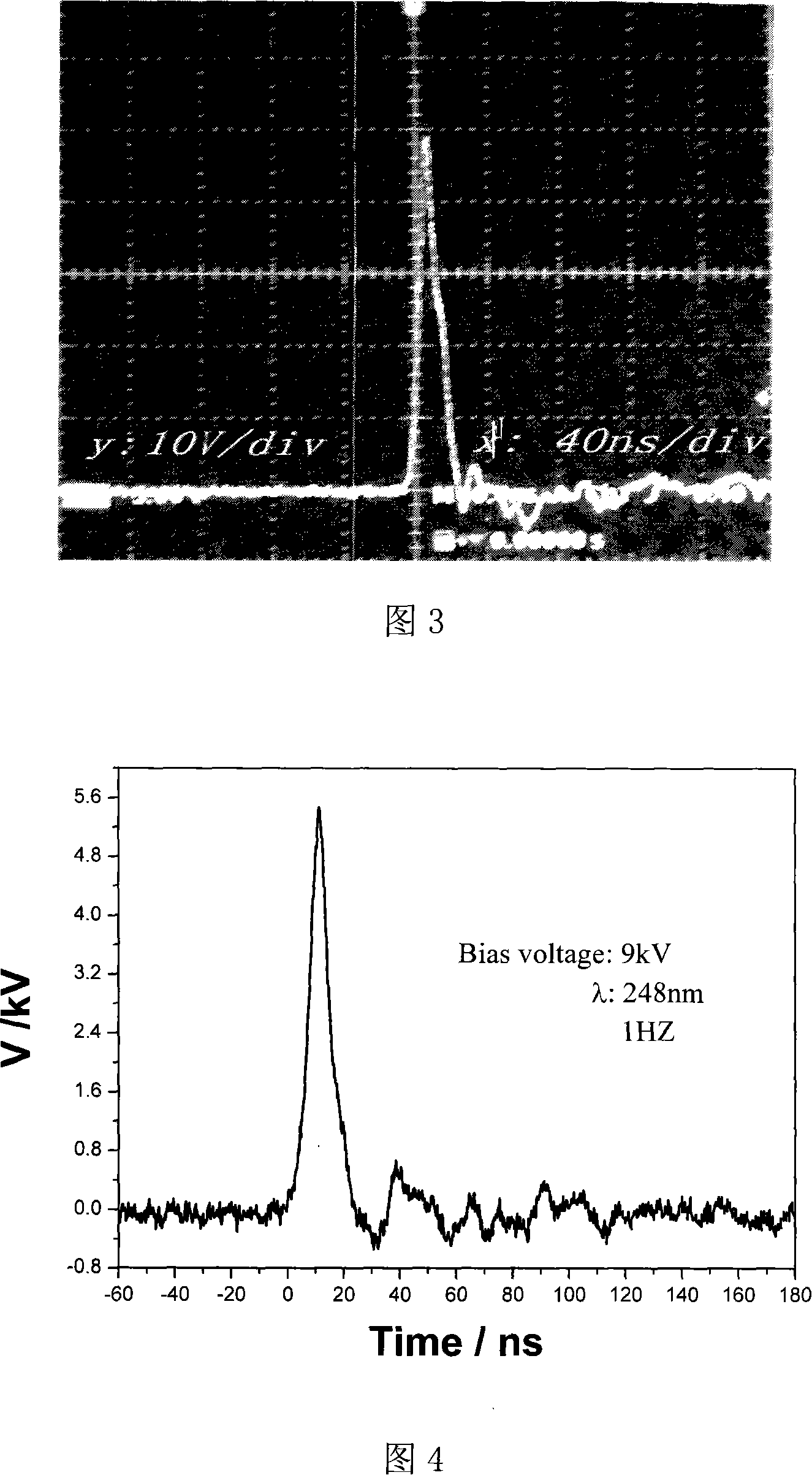

[0035] Opposite-plane photoconductive switches obtained using (11-20) plane semi-insulating SiC crystals.

[0036] The wafer used in the SiC photoconductive switch is a semi-insulating 6H-SiC crystal obtained by doping vanadium. The wafer sample is cut along the direction parallel to the c-axis of the crystal. The crystal plane is (11-20), and the thickness after double-sided polishing is 0.5mm. It is 10.0mm×10.0mm, and the surface roughness Ra of the crystal detected by AFM is less than 0.5nm. In order to remove the surface oxide layer and the sub-damage layer formed during processing, and passivate the wafer surface, the SiC wafer was annealed at 1000°C for 15 hours, then immersed in 200°C molten KOH solution for 3min etching, and finally Soak it in dilute HF for 12 hours, and then clean it according to the RCA process, so as to prepare for the production of device electrodes.

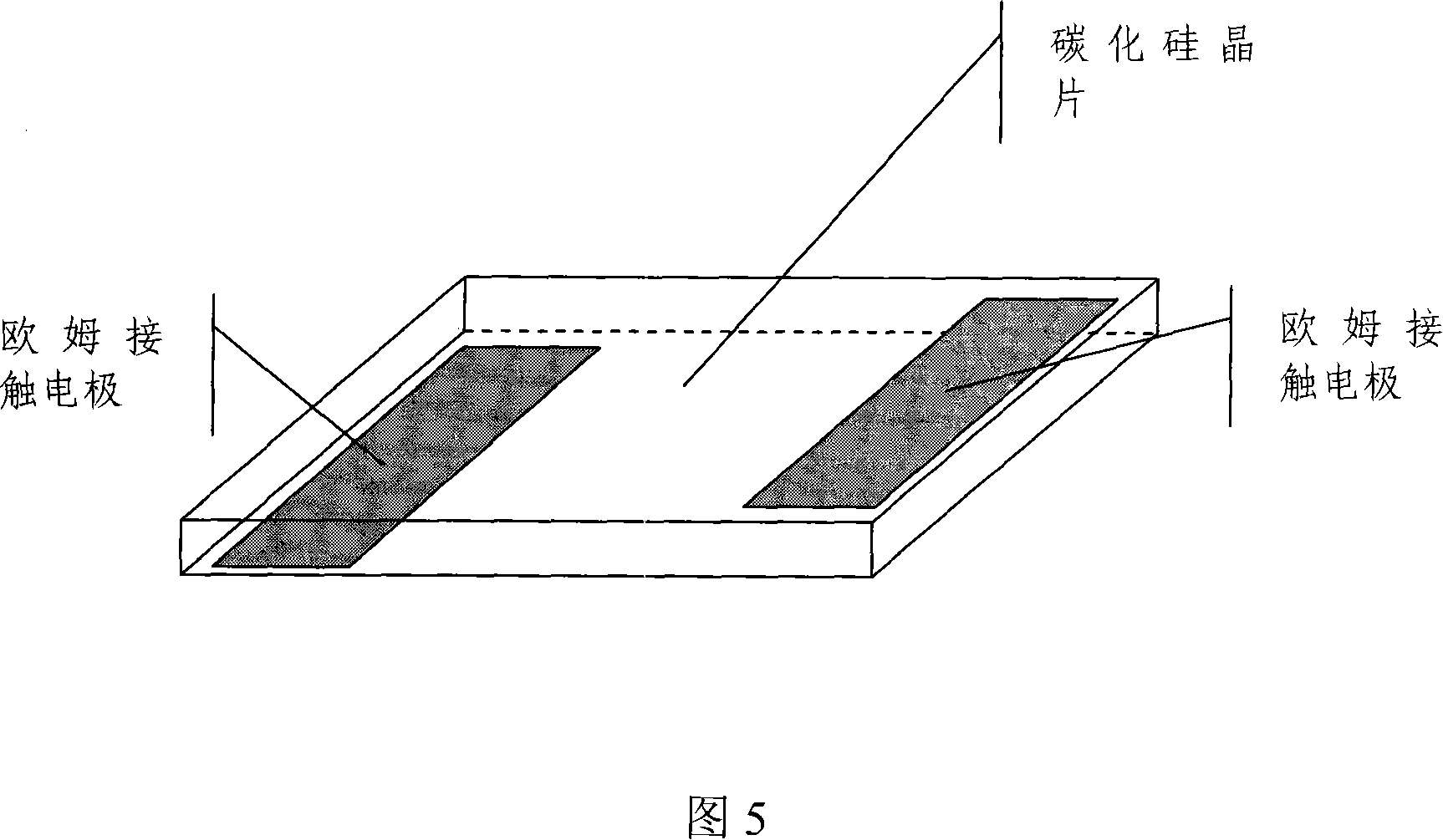

[0037]The device fabricated in the experiment adopts the opposite surface electrode structure, a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More