Polycrystal collecting area invert structure SiGe hetero-junction transistor

A heterojunction transistor and inverted structure technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of not being able to manufacture high-quality transistors, affecting the high-frequency performance and microwave performance of SiGeHBT, and achieve excellent High frequency performance, effect of reducing process complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

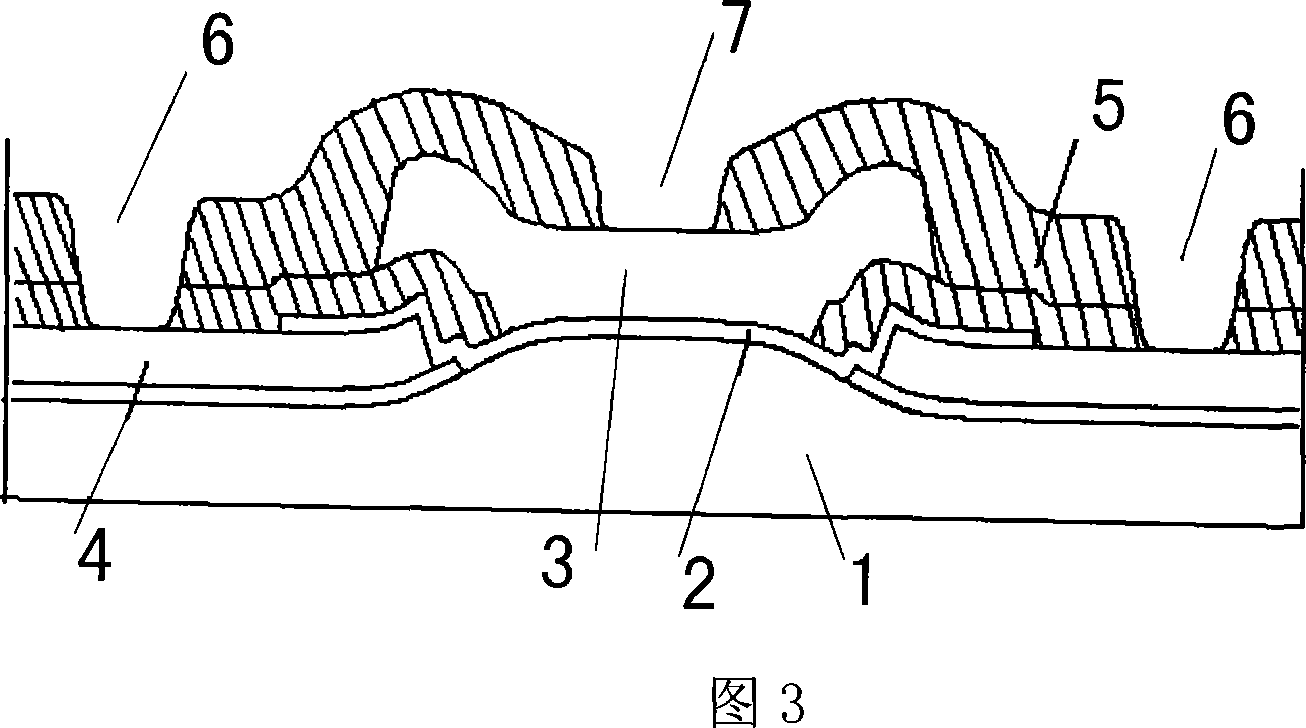

[0040] The invention provides a SiGe heterojunction transistor with an inverted structure in a polysilicon collection area. Its main structure is shown in Figure 3 as the cross-sectional structure of the device.

[0041] The specific production process is illustrated as follows:

[0042] 1) On the substrate silicon wafer, the substrate silicon wafer can be a double-layer structure of P-type plus N+-type Si, or it can be all N+-type. The field oxide layer is grown, typically 1 μm, and then all oxide layers are removed. After this After one-step treatment, the surface presents a slow ups and downs;

[0043] 2) Growth of a thin oxide layer (SiO 2Layer) 5, typically 30nm to 50nm; using LPCVD to deposit polycrystalline Si for base extraction, typically 200nm, and perform P-type doping on the polycrystalline Si;

[0044] 3) RIE plasma dry etching is used to etch away part of the polysilicon, leaving only the part used as the base lead 4; and then wet etching the thin oxide layer ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More