Semiconductor memory and forming method thereof

A semiconductor and memory technology, applied in the field of non-volatile semiconductor memory and its formation, can solve the problems of poor data retention, increase the leakage current of the inter-gate insulating layer, etc., and achieve the effect of strengthening the erasing and writing operations and strengthening the electron tunneling.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

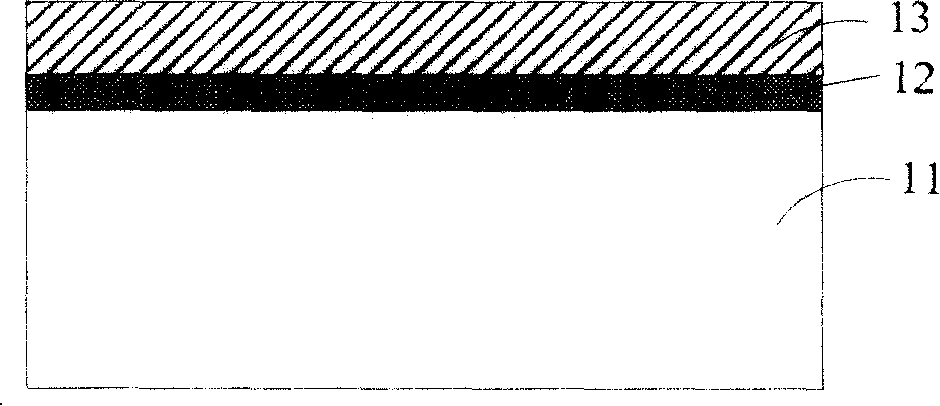

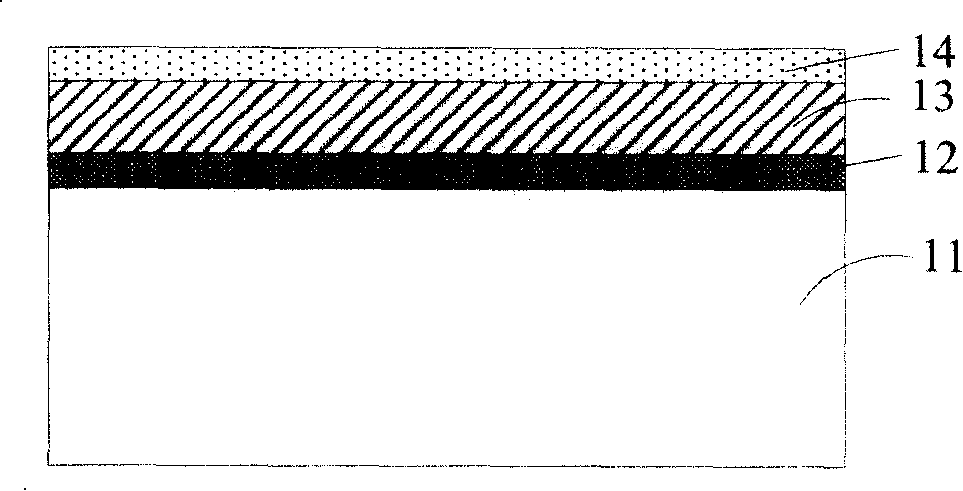

[0038] The present invention firstly provides a method for forming a gate structure, including: sequentially forming a tunnel insulating layer and a first polysilicon layer on a semiconductor substrate; forming a gate structure made of silicon nitride on the first polysilicon layer A first interlayer insulating layer; forming a second interlayer insulating layer made of high-k dielectric on the first interlayer insulating layer; forming a second polysilicon layer on the second interlayer insulating layer.

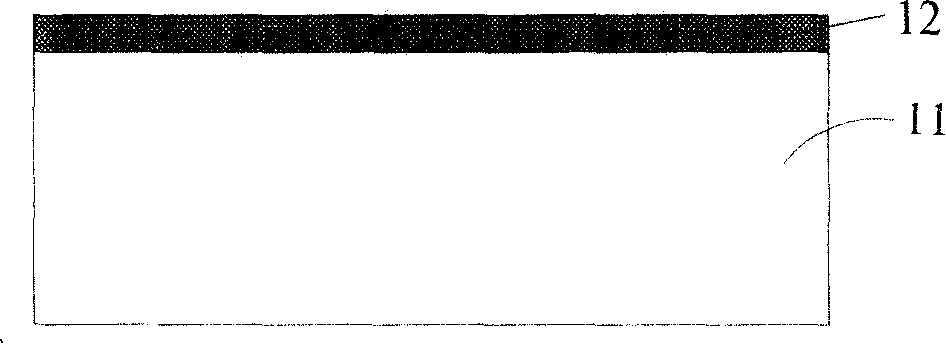

[0039] refer to figure 1 As shown, it is a schematic structural diagram of forming a tunnel insulating layer 12 on a semiconductor substrate 11 . figure 1 The semiconductor substrate 11 shown in is silicon, and silicon-on-insulator (SOI) can also be used as the semiconductor substrate 11 . The tunnel insulating layer 12 shown in the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More