Method for manufacturing IGBT silicon epitaxial wafer

A kind of manufacturing method, technology of silicon epitaxial wafer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The specific embodiment of the present invention is described in detail below:

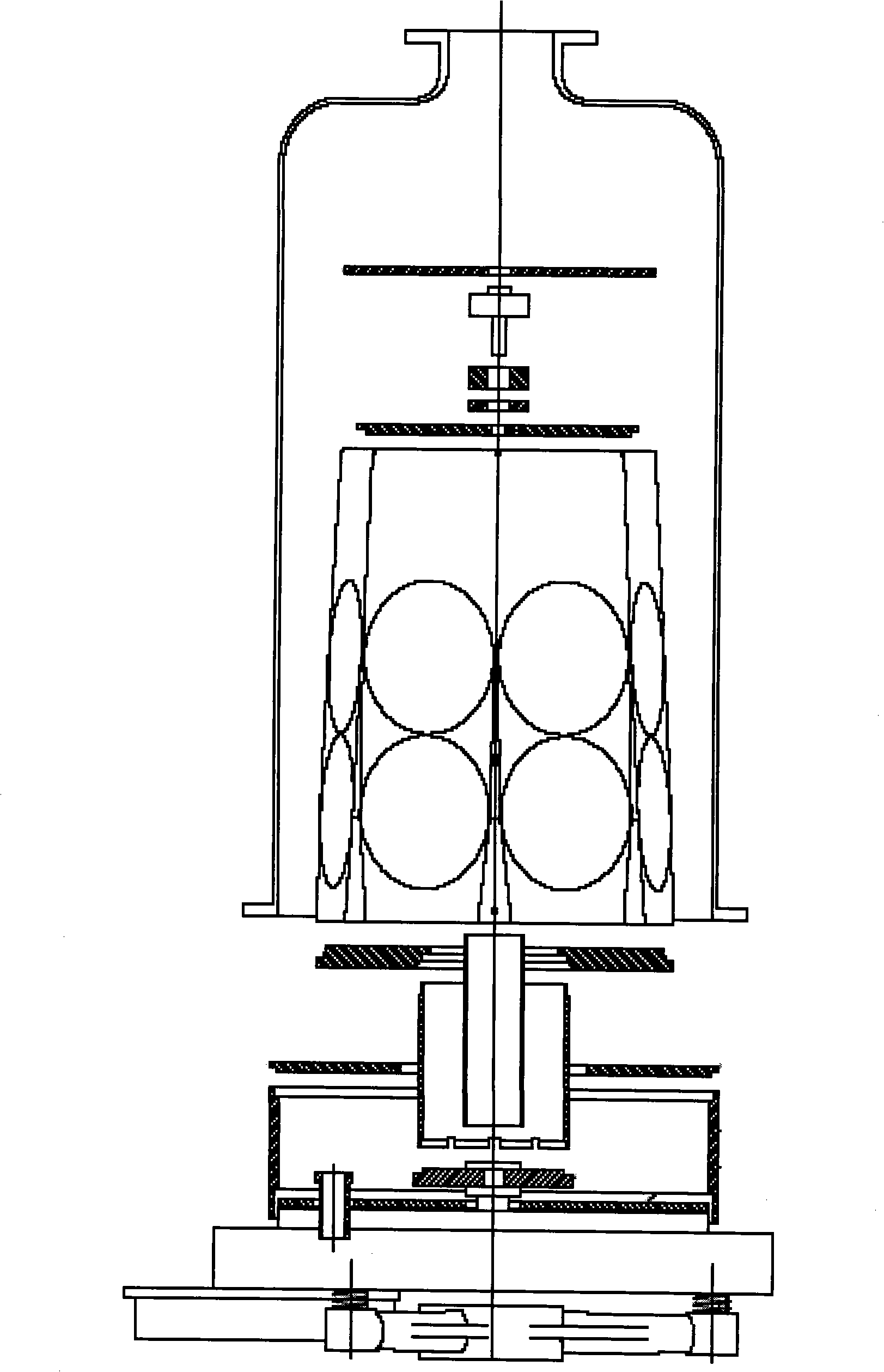

[0018] The equipment used in the present invention is Italy PE-2061S normal pressure silicon epitaxial growth system, see figure 1 , the high-purity graphite base is used as a high-frequency induction heating body, and the main carrier gas is H 2 The purity is above 99.9999%.

[0019] Reactor cleaning: The quartz bell jar and the quartz parts used in the reaction chamber must be carefully cleaned before epitaxy, and the deposition residue on the inner wall of the quartz bell jar and the quartz parts must be thoroughly removed.

[0020] High-temperature treatment in the reaction chamber: Before epitaxial growth, the graphite base must be subjected to HCl high-temperature treatment to remove residual reactants on the base and deposit a layer of intrinsic polysilicon.

[0021] Vapor phase polishing: before epitaxial growth, perform HCl polishing and corrosion on the substrate to remove mecha...

PUM

| Property | Measurement | Unit |

|---|---|---|

| purity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More