Self-alignment elevated external base area or heterojunction bipolar transistor and manufacturing method thereof

A heterojunction bipolar, extrinsic base technology, applied in transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve problems such as process implementation plan to be improved, process quality control, connection base area voids, etc., to reduce Dependency and Sensitivity, Simplified Process Control, Guaranteed Symmetric Effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] As an example of an embodiment, the specific preparation process steps of the selective epitaxial self-aligned raised extrinsic base bipolar transistor or heterojunction bipolar transistor proposed by the present invention are as follows:

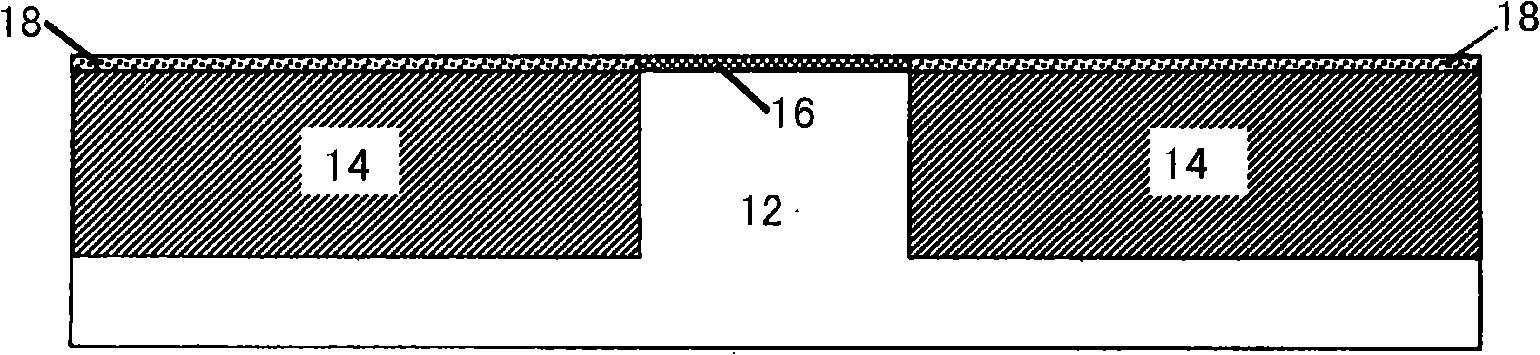

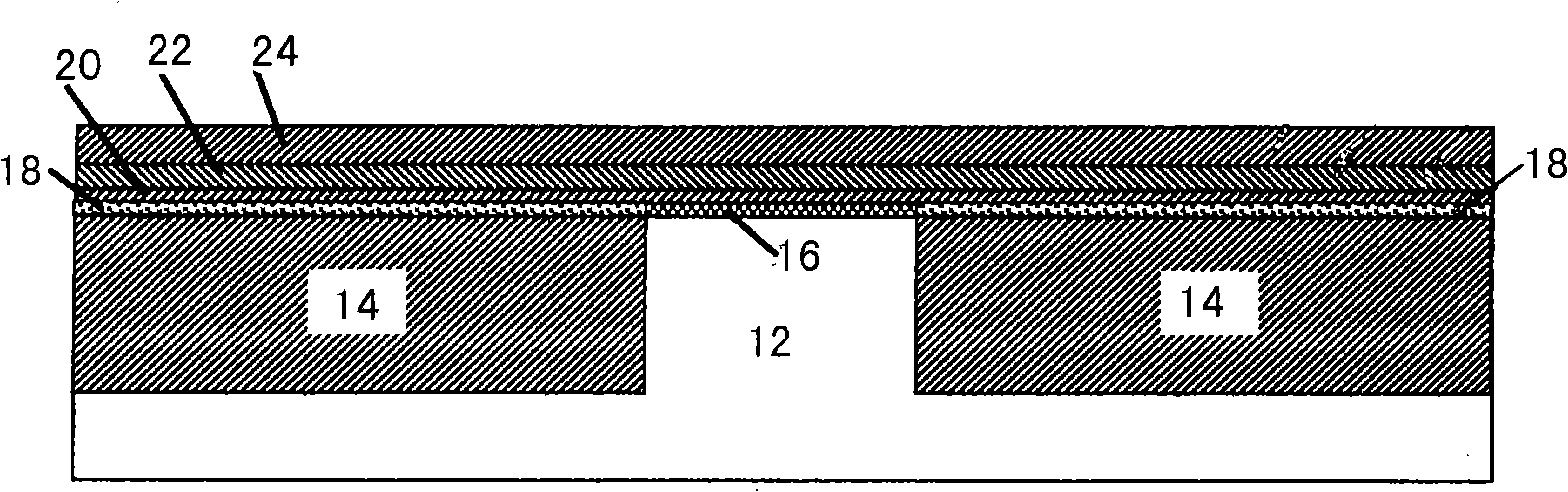

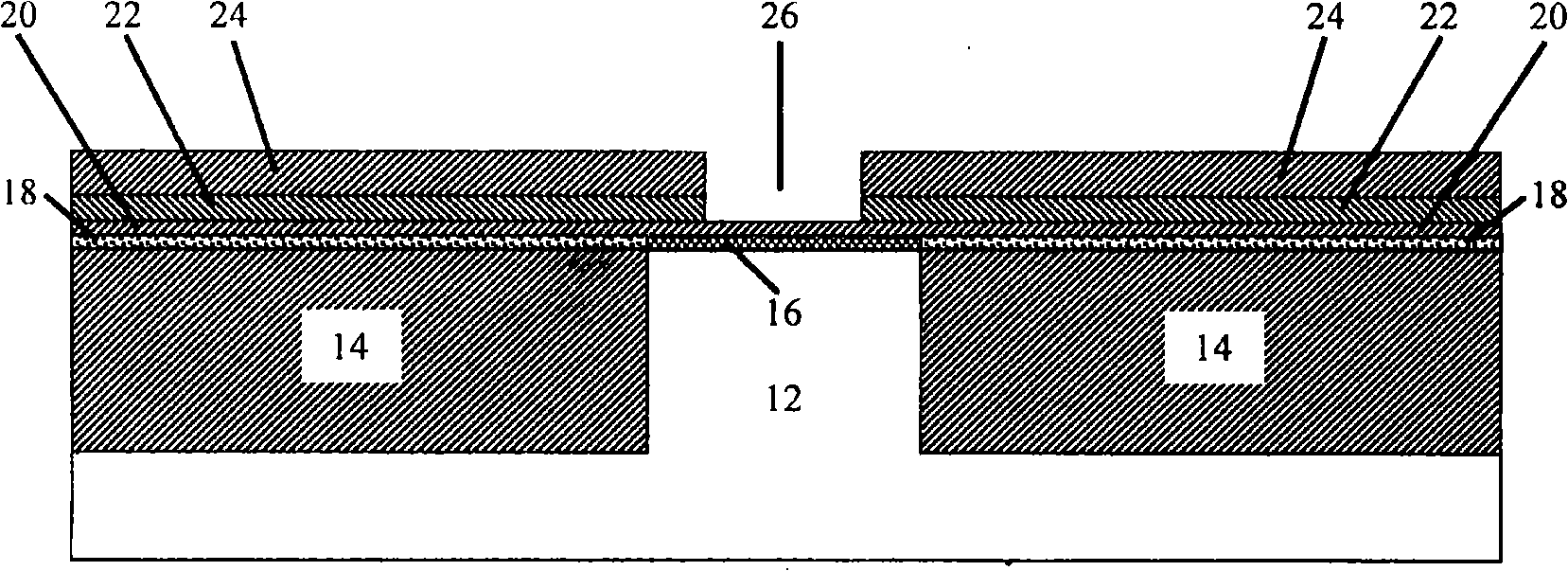

[0021] 1. The Si collector region 12 of the first conductivity type formed by the semiconductor substrate or located on the surface of the semiconductor substrate (such as figure 1 shown). In order to reduce the capacitance C between the base region and the collector region BC The partial dielectric region 14 can be formed on the surface of the collector region by digging shallow grooves and then filling with dielectric material or by local oxidation. The local dielectric region 14 is generally silicon oxide, but not limited thereto.

[0022] 2. Form the Si or SiGe base region of the opposite second conductivity type by means of epitaxial growth and in-situ doping, that is, obtain the Si or SiGe base region 16 of the second conduc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More