Novel CMOS integrated circuit resisting total dose radiation

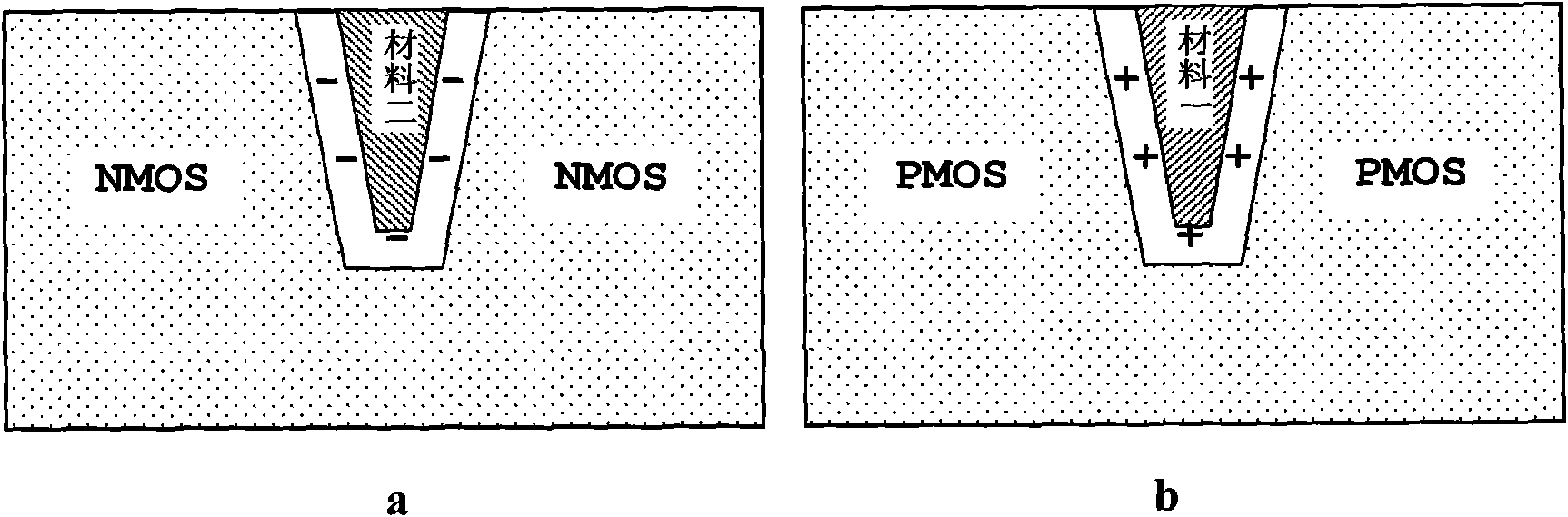

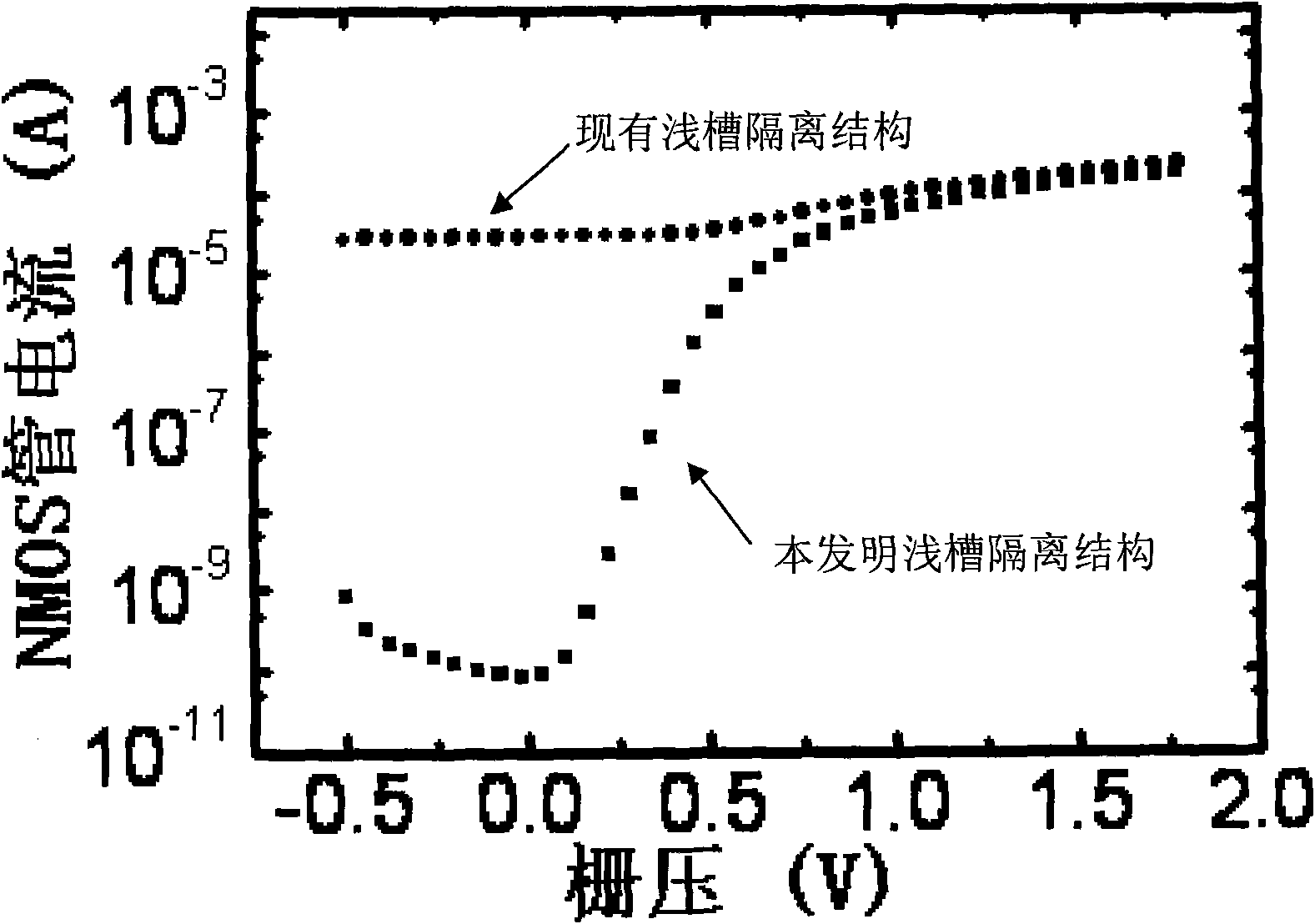

A total dose irradiation, integrated circuit technology, applied in the field of electronics, can solve problems such as increasing integrated circuit power consumption, large off-state leakage current, etc., to eliminate parasitic leakage, wide application prospects, and enhance resistance to total dose irradiation Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention will be further described below through a specific preparation example in conjunction with the accompanying drawings.

[0020] This embodiment prepares the CMOS integrated circuit of the novel anti-NMOS device total dose irradiation of the present invention, mainly comprises the following steps:

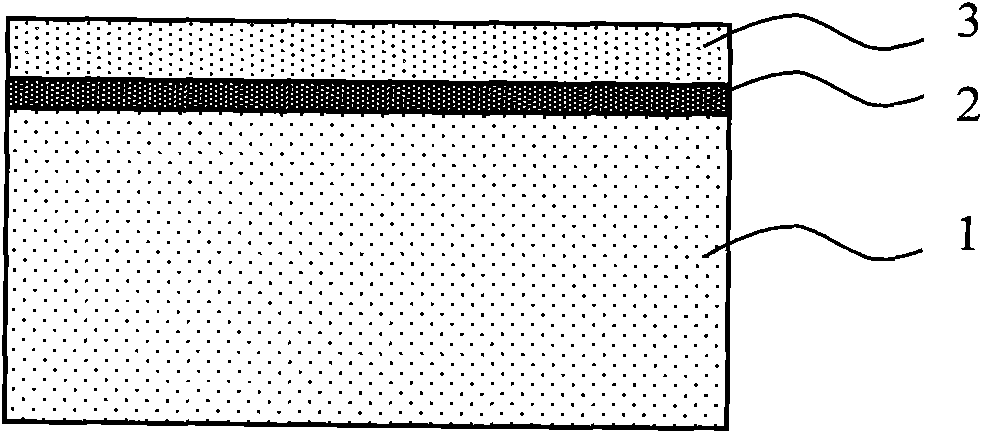

[0021] 1) Formation of silicon dioxide and silicon nitride. Such as image 3 shown. Thermally oxidize and grow a layer of silicon dioxide with a thickness of about 100 angstroms to 200 angstroms on the bulk silicon substrate 1 as a stress buffer layer 2 between silicon nitride and the silicon substrate, and then use low-pressure chemical vapor deposition (LPCVD) method to deposit a layer of 1000 angstrom to 1500 angstrom silicon nitride as the barrier layer 3 .

[0022] 2) First trench lithography and etching. Such as Figure 4 shown. After defining the shown pattern with the first photolithography plate lithography, the trapezoidal trench 4 is etch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More