Method for introducing dislocation on silicon chip

A dislocation and silicon wafer technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of harsh thermal care conditions, expensive equipment, and reduced material purity, and is conducive to large-scale industrial production. , The effect of high energy utilization and strong controllability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

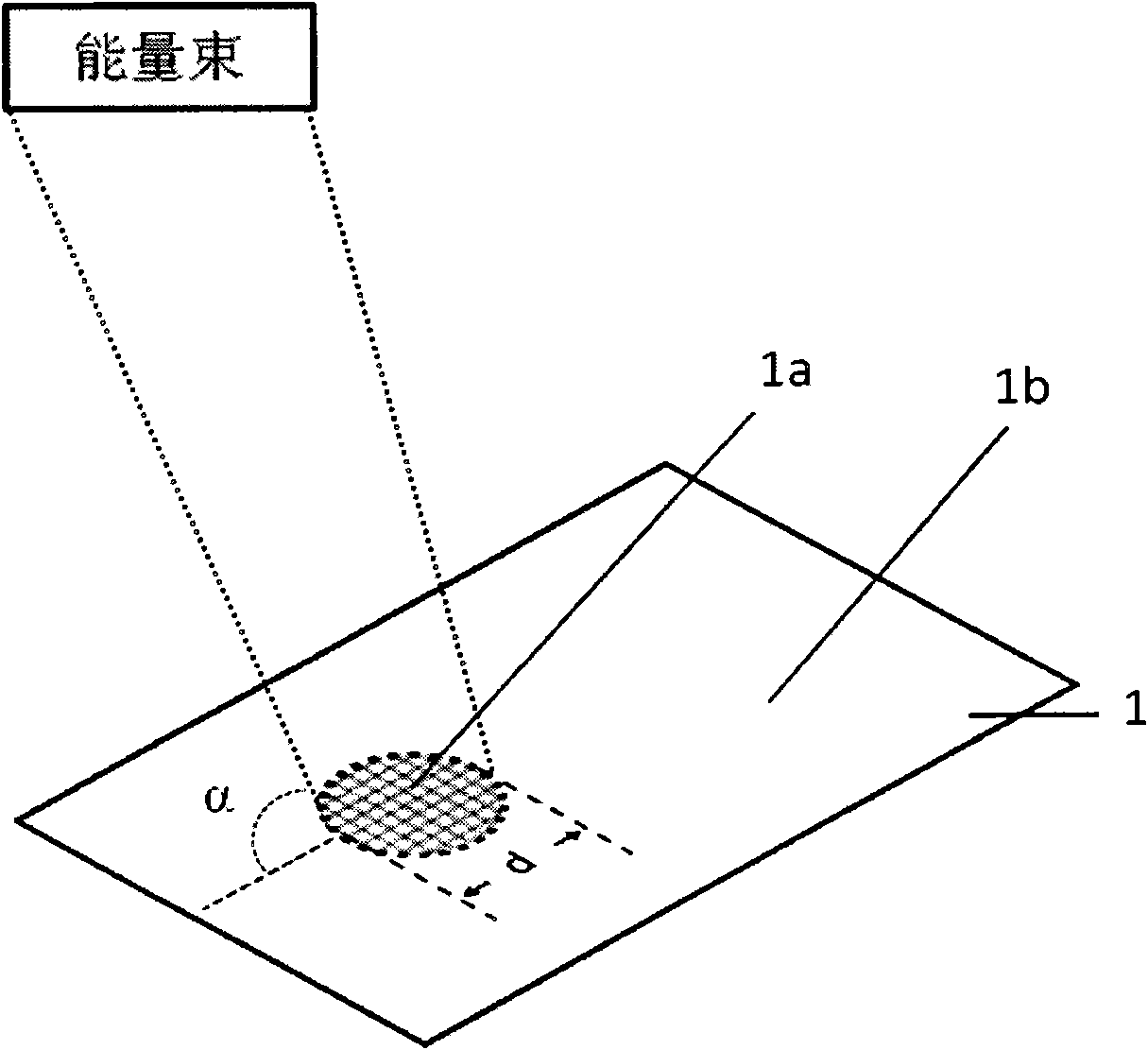

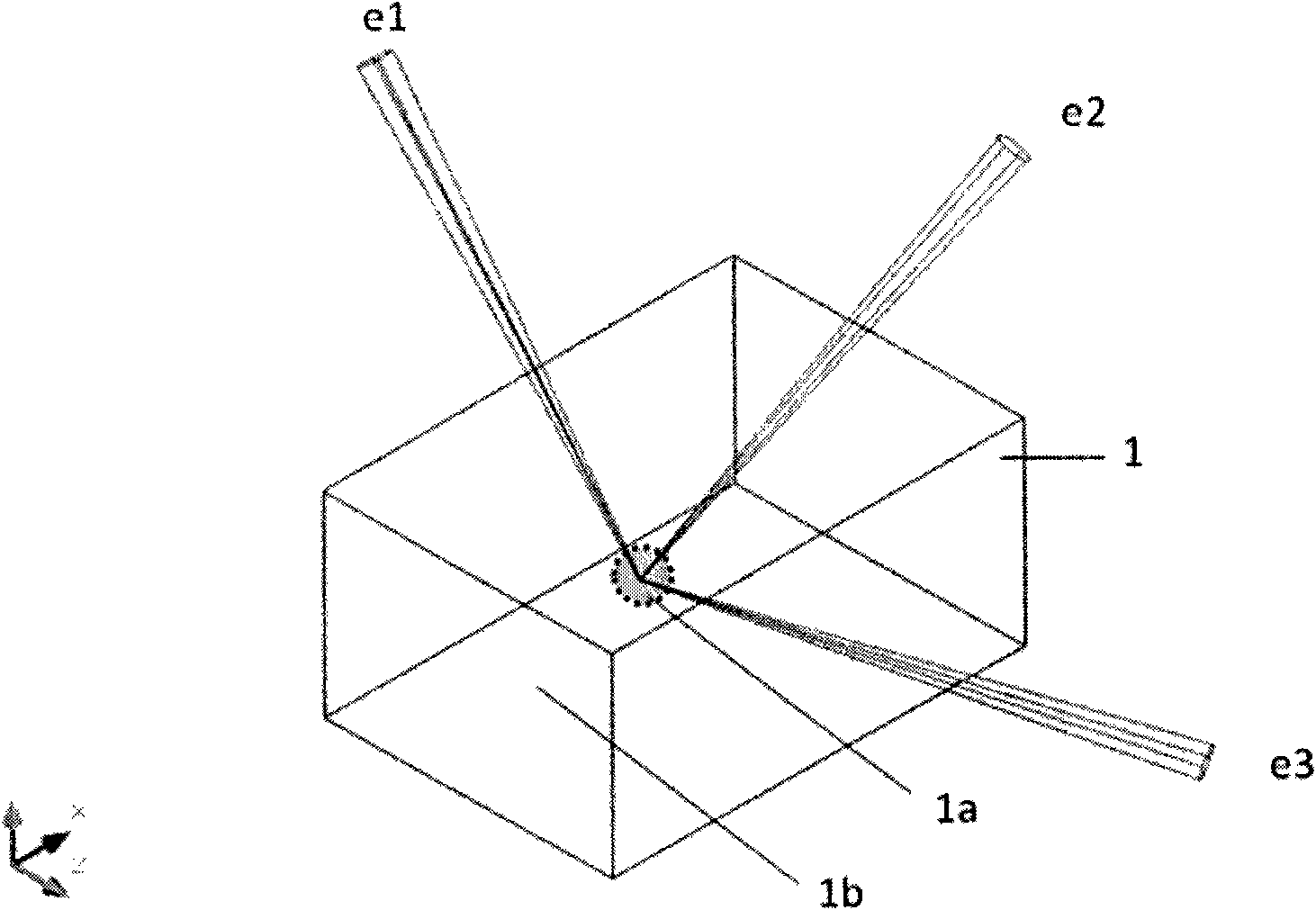

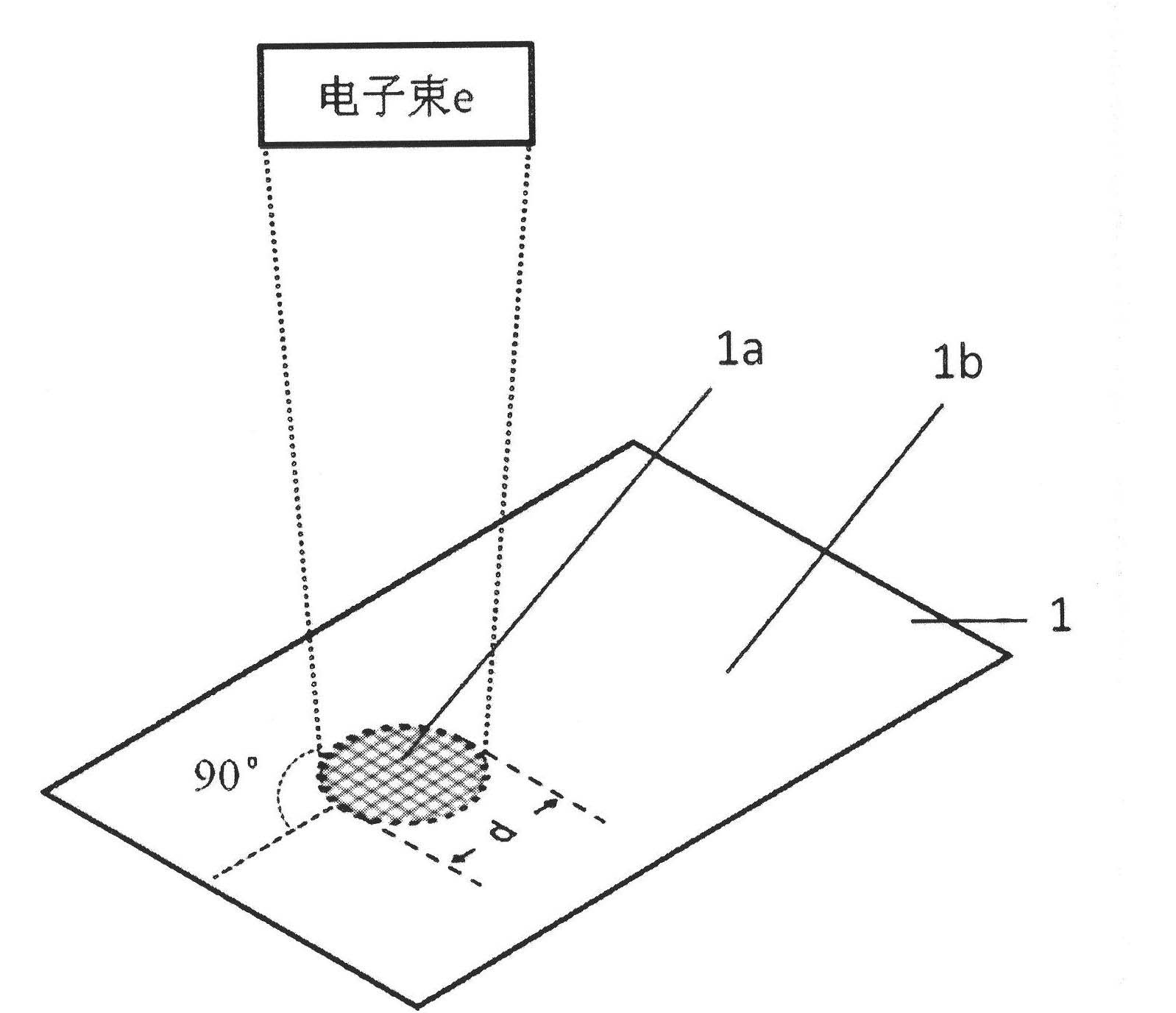

[0035] Such as image 3 As shown, the present embodiment adopts electron beam to p-typeCZ silicon The electron beam is perpendicular to the silicon wafer, the filament voltage in the electron beam evaporation instrument is 82V, the filament current is 0.50A, and the vacuum degree of the back is 5×10 -3 Pa, the beam current of the electron beam is 20mA, the gun voltage is 8.5kV, the beam spot diameter is 6.0mm, and the power per unit area of the electron beam is 1.5W / mm 2 .

[0036] After the irradiation, the irradiated area was a circular area with a diameter of 6mm, and the dislocation density was 5.2×10 6 cm -2 The area with dislocations is consistent with the diameter of the electron beam spot, indicating that the shape of the dislocation area can be controlled by the shape of the electron beam spot.

[0037] With 0.15mol / L of K 2 Cr 4 o 7 The aqueous solution and 50% (mole percent) HF aqueous solution were configured as Secco etching solution at a volume ratio of ...

Embodiment 2

[0040] The experimental conditions of this example are similar to those of Example 1. The n-type CZ silicon wafer is placed at the sample of the electron beam evaporation instrument, the filament voltage is 80V, the filament current is 0.92A, and the vacuum degree of the background is 2×10 -4 Pa, the beam current of the electron beam is 0.9A, the gun voltage is 2.0kV, the beam spot diameter is 4.0mm, and the power per unit area of the electron beam is 458.6W / mm 2 .

[0041] After the irradiation, it was measured that the dislocation density introduced in the irradiated area was 1.2×10 8 cm -2 , and photographed its optical microscopic corrosion topography, such as Figure 7 shown. It can be seen that the present invention can conveniently introduce ultra-high-density dislocations into the silicon wafer by adjusting the energy intensity of the electron beam.

Embodiment 3

[0043] The experimental conditions of this example are similar to those of Example 1. The p-type FZ silicon wafer is placed at the sample of the electron beam evaporation instrument, the filament voltage is 80V, the filament current is 0.60A, and the vacuum degree of the background is 2×10 -2 pa, the beam current of the electron beam is 30mA, the gun voltage is 10.0kV, the beam spot diameter is 1.0mm, and the power per unit area of the electron beam is 382.1W / mm 2 .

[0044] After the irradiation, it was measured that the dislocation density introduced in the irradiated area was 8.1×10 7 cm -2 , and photographed its optical microscopic corrosion topography, such as Figure 8 shown.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More