Prescaler with clock-controlled transistor

A prescaler, transistor technology, applied in pulse counters, counting chain pulse counters, electrical components, etc., can solve problems such as poor circuit stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment

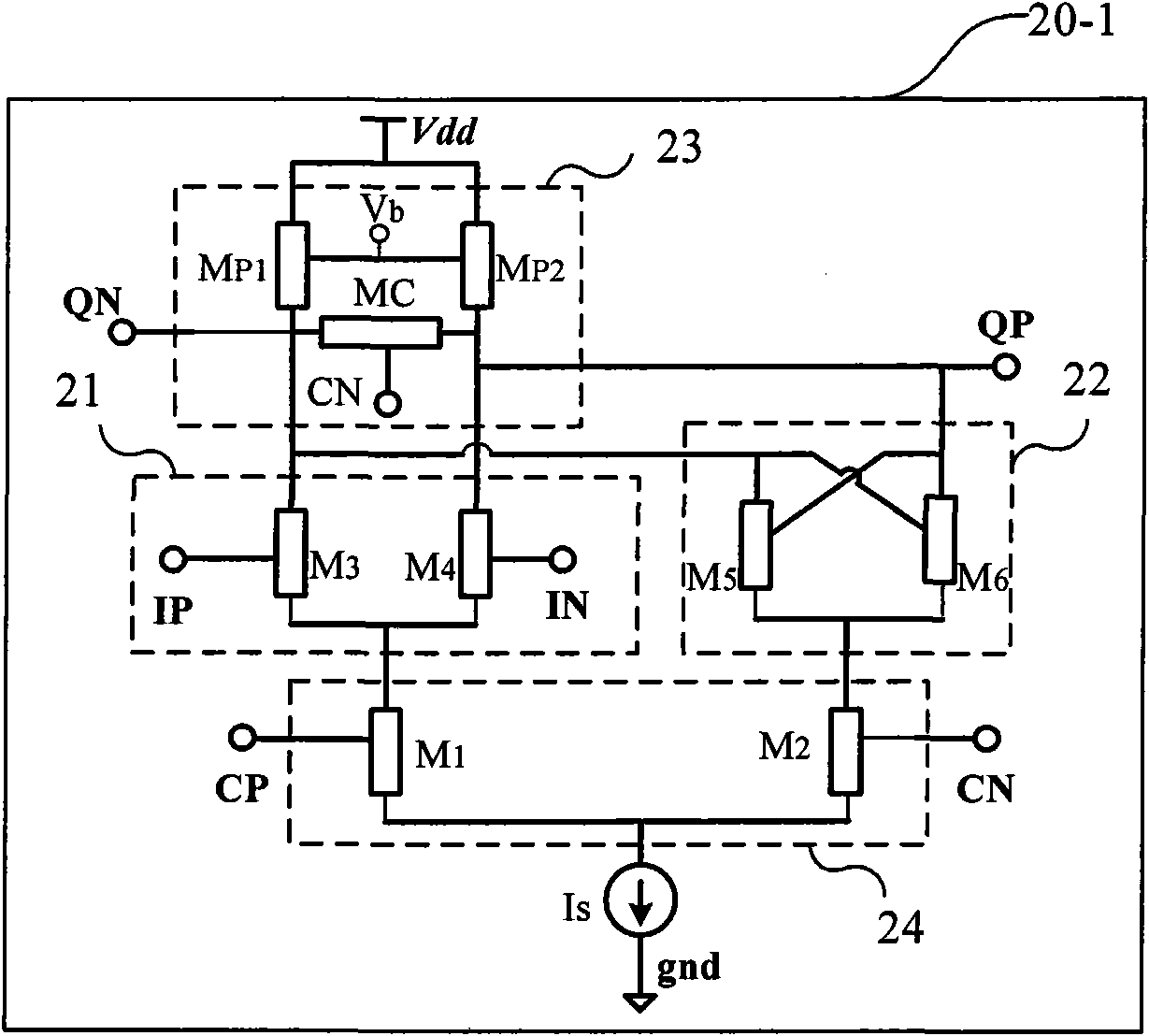

[0074] Such as image 3 Provided is a circuit diagram of the prescaler with clocked transistors in the first embodiment. The prescaler with clocked transistors includes a first flip-flop 30 and a second flip-flop 30 ′. The first flip-flop consists of M 3 and M 4 The sampling differential pair consists of tube 31 and consists of M 5 and M 6 Composed of a latched cross-coupled pair of transistors 32, consisting of MP 1 , MP2 and clock control tube MC 1 consists of load modules 33, and consists of M 1 and M 2 The clock input differential pair consists of transistors 34 . The second flip-flop consists of M 9 and M 10 The sampling differential pair consists of tube 35, and consists of M 11 and M 12 Composed of a latched cross-coupled pair of transistors 36, consisting of MP 3 , MP 4 and clock control tube MC 2 consists of load modules 37, and consists of M 7 and M 8 The clock input differential pair consists of transistors 38 . image 3 , amplifier M 1 ~ M 12 All...

no. 2 Embodiment

[0090] Such as Figure 4 The block diagram of the prescaler with clocked transistors involved in the second implementation example given is a modification of the first implementation example, using a resistive device instead of a MOS tube. The prescaler with clocked transistors includes a first flip-flop 40 and a second flip-flop 40', the first flip-flop 40 consists of M 3 and M 4 The sampling differential pair consists of tube 41, consisting of M 5 and M 6 The latching cross-coupled pair consisting of transistor 42, consists of Z 1 ,Z 2 and clock control tube M C1 consists of load module 43, and consists of M1 and M 2 The clock input differential pair consists of transistor 44 . The second flip-flop 40' consists of M 9 and M 10 The sampling differential pair consists of tube 45, consisting of M 11 and M 12 The latching cross-coupled pair consisting of transistor 46, consists of Z 3 ,Z 4 and clock control tube M C2 consisting of load module 47, and consisting of ...

no. 3 Embodiment

[0092] Such as Figure 5 The block diagram of the prescaler with clocked transistors involved in the third implementation example given is a modification of the first implementation example, using PMOS tubes as amplifier components, and NMOS tubes as load tubes and clock control tubes. The prescaler with clocked transistors includes a first flip-flop 50 and a second flip-flop 50'. The first flip-flop 50 consists of M 3 and M 4 composed of sampled differential pairs 51, consisting of M 5 and M 6 composed of 52 latched cross-coupled pairs, consisting of M N1 ,M N2 and clock control tube M C 1 consisting of a load module 53, and consisting of M 1 and M 2 Composed of the clock input differential amplifier 54'. The second flip-flop 50' consists of M 9 and M 10 consisting of 55 sampled differential pairs, and consisting of M 11 and M 12 composed of 56 latched cross-coupled pairs, consisting of M N3 ,M N4 and clock control tube M C2 Composed of load modules 57, and co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com