High-mobility quantum-dot field effect transistor and manufacturing method thereof

A field-effect transistor and high-mobility technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of few studies on the influence of output characteristics, achieve practical and reliable methods, increase yield, reduce The effect of small degradation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

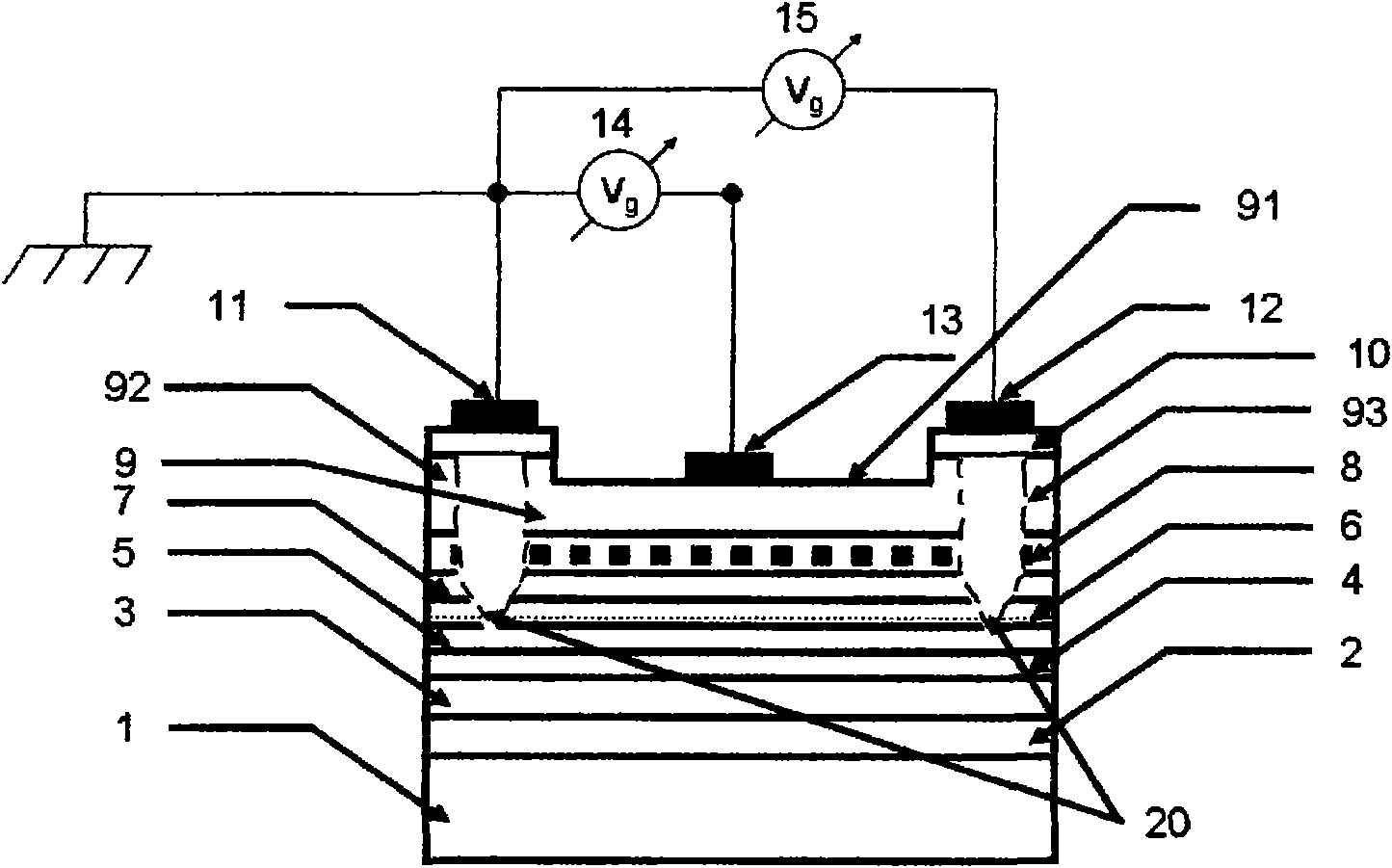

[0042] see figure 1 Shown, a kind of high mobility quantum dot field effect transistor of the present invention comprises:

[0043] A substrate 1, the substrate 1 is a semi-insulating gallium arsenide or indium phosphide substrate of the (100) plane, to provide the required crystal plane for anisotropic etching and reduce the leakage current of the substrate;

[0044] A first stress buffer layer 2, the first stress buffer layer 2 is fabricated on the substrate 1;

[0045] A second stress buffer layer 3, the second stress buffer layer 3 is made on the first stress buffer layer 2, the stress buffer layer 2 and the stress buffer layer 3 are undoped semiconductor materials, the purpose is to obtain high-quality epitaxy Layer, to reduce the influence of defects in the substrate on the electron channel layer 6, the thickness needs to be more than 100nm, and a thicker stress buffer layer will have a better effect, but the cost will increase accordingly. Generally, GaAs with a total ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More