A Phase Detector Circuit Applied to Clock Data Recovery

A clock data recovery, phase detector technology, applied in the direction of electrical components, power automatic control, etc., can solve the problem of insufficient phase detector gain of phase detection accuracy, so as to broaden the locking capture range, improve performance, and reduce locking time Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

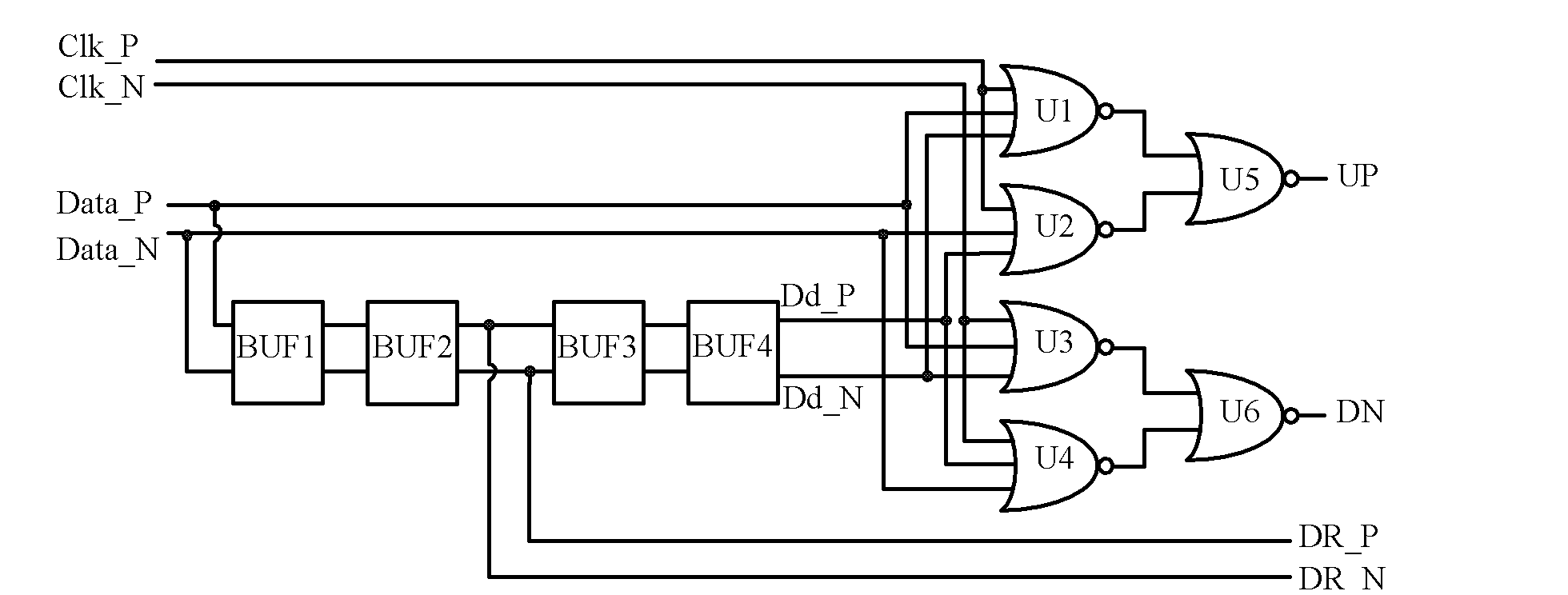

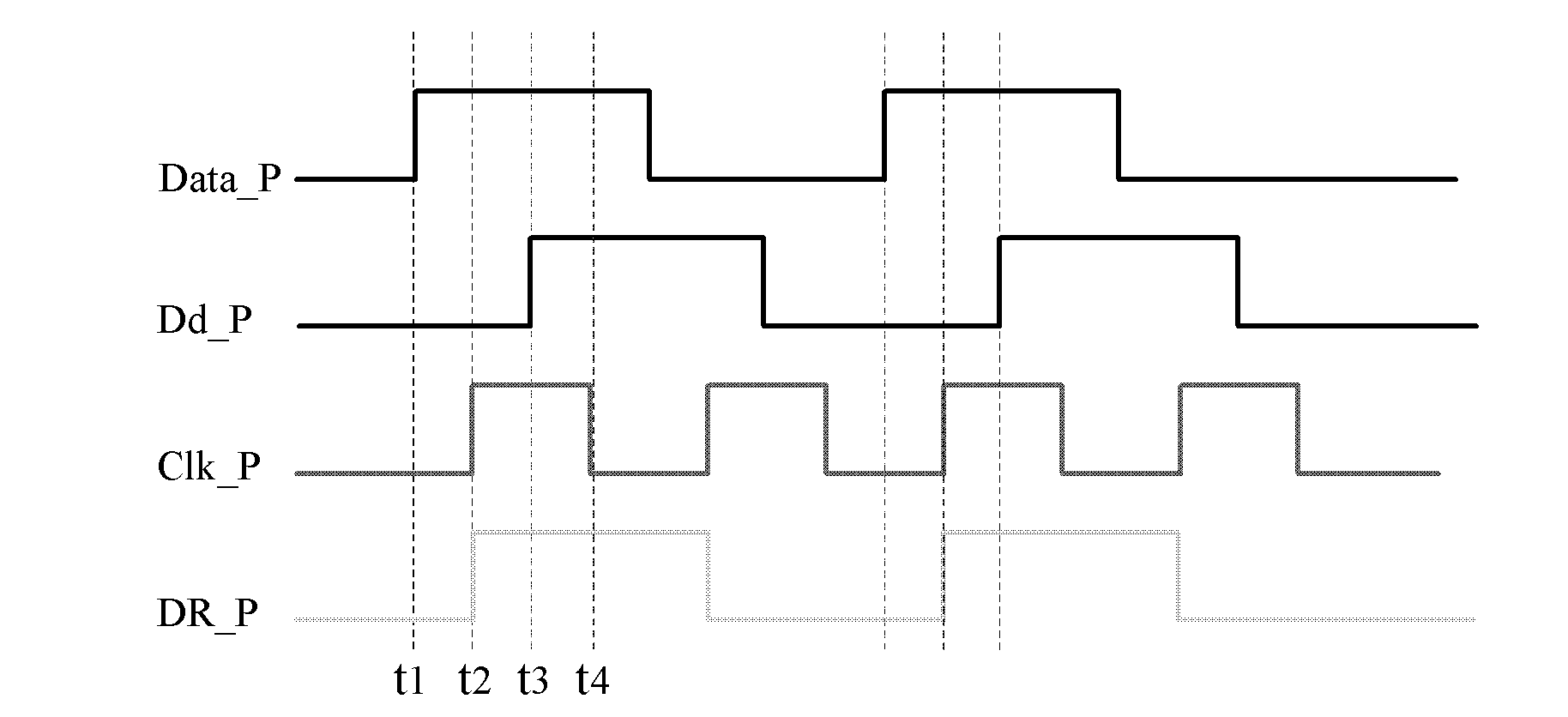

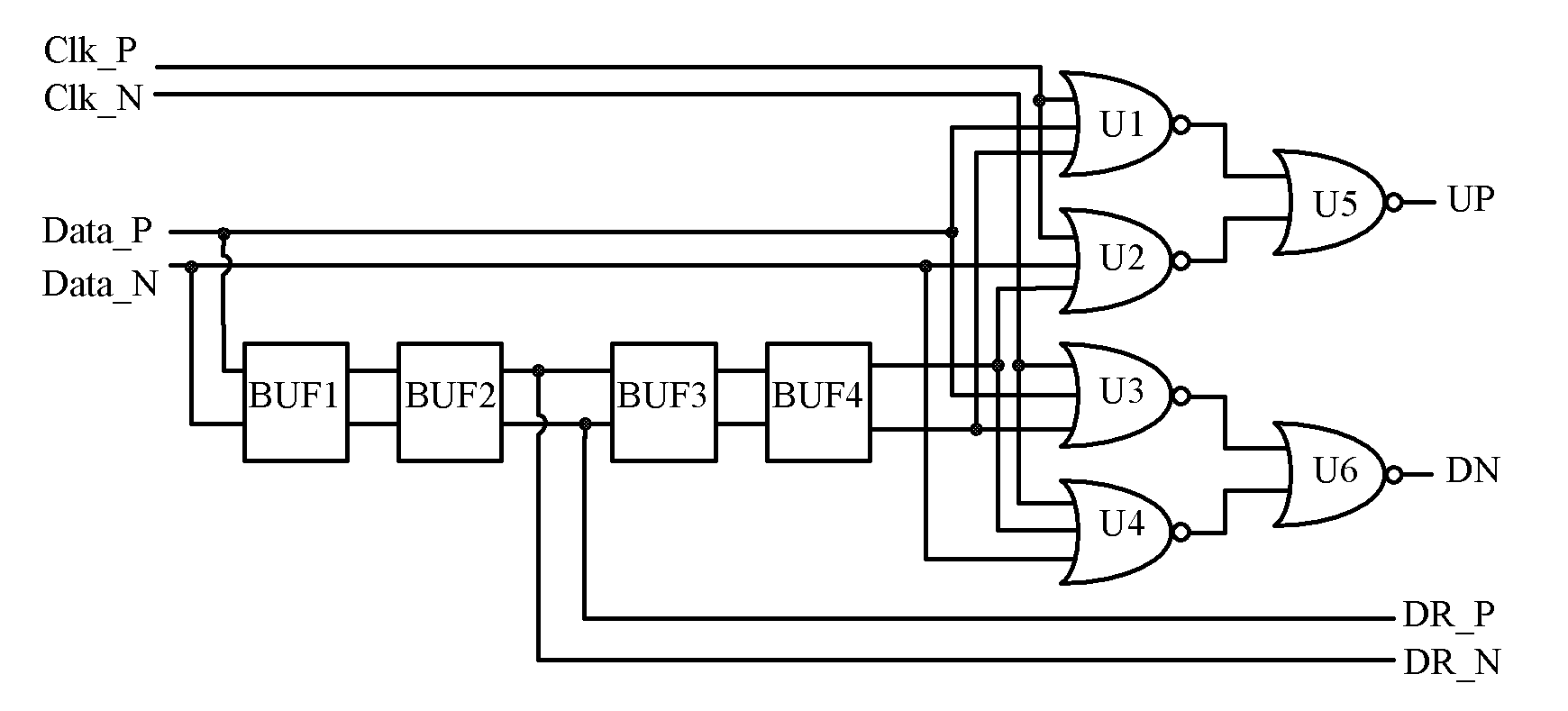

[0013] like figure 1 Shown, the present invention is a kind of phase detector circuit that is applied to clock data recovery, consists of 4 delay buffers BUF1, BUF2, BUF3, BUF4 and 4 three-input NOR gates U1, U2, U3, U4 and 2 Two-input NOR gate U5, U6 is composed, the structure is very simple. Clk_P and Clk_N are differential clock signals, Data_P and Data_N are differential data signals, DR_P and DR_N are signals of Data_P and Data_N after passing through delay buffers BUF1 and BUF2, Dd_P and Dd_N are signals of DR_P and DR_N after passing through delay buffers BUF3 and BUF4 Signals, DR_P and DR_N are the data signals recovered by CDR, Clk_P and Clk_N are the clock signals recovered by CDR, and the goal of CDR is to make the sampling edges of Clk_P and Clk_N in the center of DR_P and DR_N, which is the best sampling point; The output terminal UP of U5 and the output terminal DN of U6 represent the phase lead and phase lag signals respectively, which are used to control the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More