Integration method of dual Damascus

An integrated method and low dielectric constant technology, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems such as difficulty in controlling the key dimensions of through holes, affecting the reliability of copper interconnection, and connecting together, etc., to achieve Suitable for popularization and application, improving performance and reliability, and avoiding the effect of leakage current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The contact hole forming method for reducing the contact hole resistance of the present invention will be further described in detail below in conjunction with the accompanying drawings and specific implementation methods.

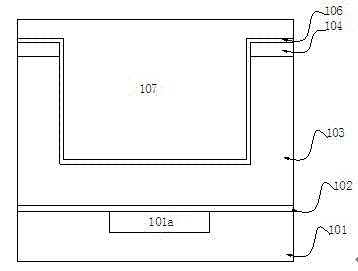

[0030] Such as figure 1 and Figure 2A-2I Shown, the integrated method of a kind of double damascene of the present invention, it comprises the following steps:

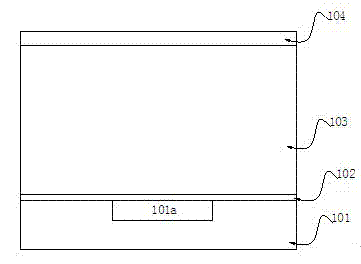

[0031] Step S1: Provide a silicon substrate 101, on which the completed front layer metal 101a is formed, and respectively adopt the chemical vapor deposition method to sequentially deposit via-hole etching barrier layers on the silicon substrate 101 from bottom to top 102, a low dielectric constant dielectric layer 103 and a dielectric protection layer 104;

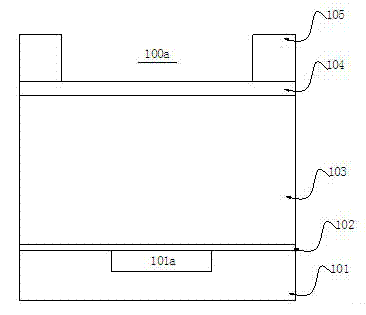

[0032] Step S2: Coating a layer of photoresist 105 on the dielectric protective layer 104 by spin coating, and performing a photolithography process (including exposure, development and other process steps) to form a trench opening...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More