Preparation method of double-layer silicon-on-insulator (SOI) mixed crystal orientation back-grid type transoid mode Si nanowire field effect transistor (NWFET)

A mixed crystal orientation and double-layer technology, applied in semiconductor/solid-state device manufacturing, nanotechnology for information processing, electrical components, etc., can solve the problem of gate resistivity adjustment, difficult process, and inability to adjust gate work function and other problems, to achieve the effect of convenient implementation, high device integration, and easy silicon layer peeling

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

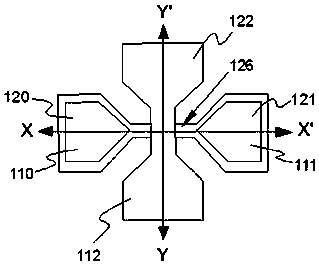

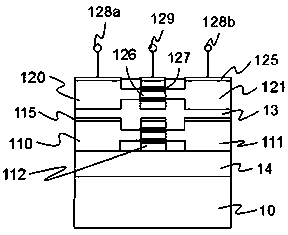

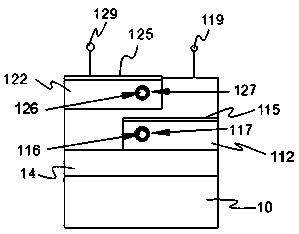

[0045] The invention provides a method for preparing a double-layer SOI mixed crystal orientation gate-back type inversion mode SiNWFET. That is, the channel regions of the upper and lower layers of MOSFETs are silicon nanowires with different surface orientations. In the low-temperature lift-off technology, as the hydrogen pressure increases, cracks tend to grow along the (100) crystal direction, so it is easier to peel off the silicon layer along the (100) crystal direction, so the lower PMOSFET + upper NMOSFET mode is used.

[0046] Theoretically speaking, the upper and lower layers of SiNWFETs can use silicon nanowires with any surface orientation. According to the research results of Yang M et al., (100) / has the largest electron mobility, and (110) / maximum hole mobility. Therefore, preferably, we use silicon nanowires with (100) surface orientation as the channel material of NMOSFET, and the channel direction of NMOSFET is , and use silicon nanowires with (110) surface...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com