Process for manufacturing series of intermediate-voltage N-type vertical conduction double-diffused metal oxide semiconductor transistors by using composite epitaxy

A field effect transistor and manufacturing process technology, applied in the field of manufacturing medium-voltage N-type series VDMOS process, can solve the problem of on-resistance drop and so on

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

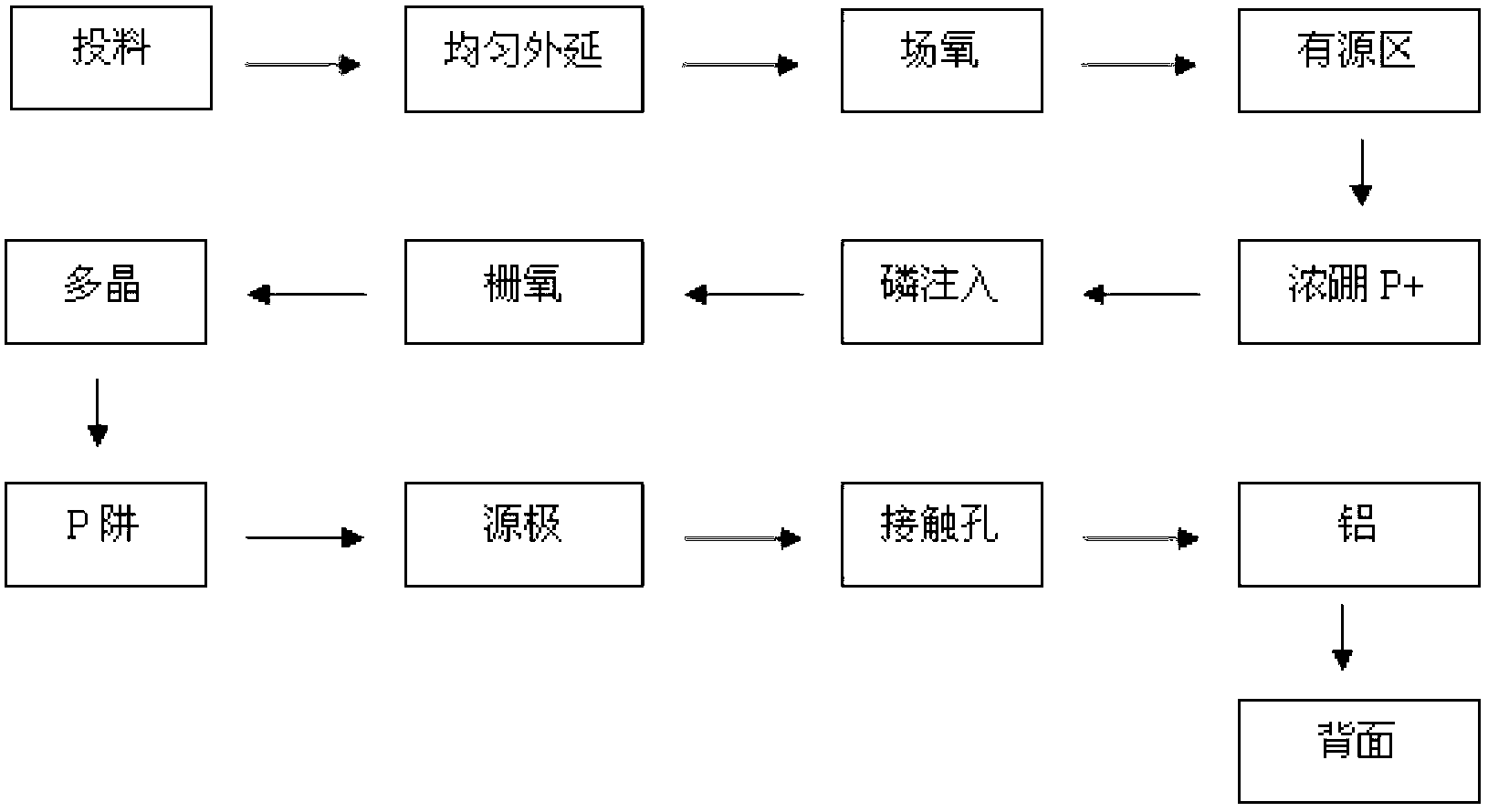

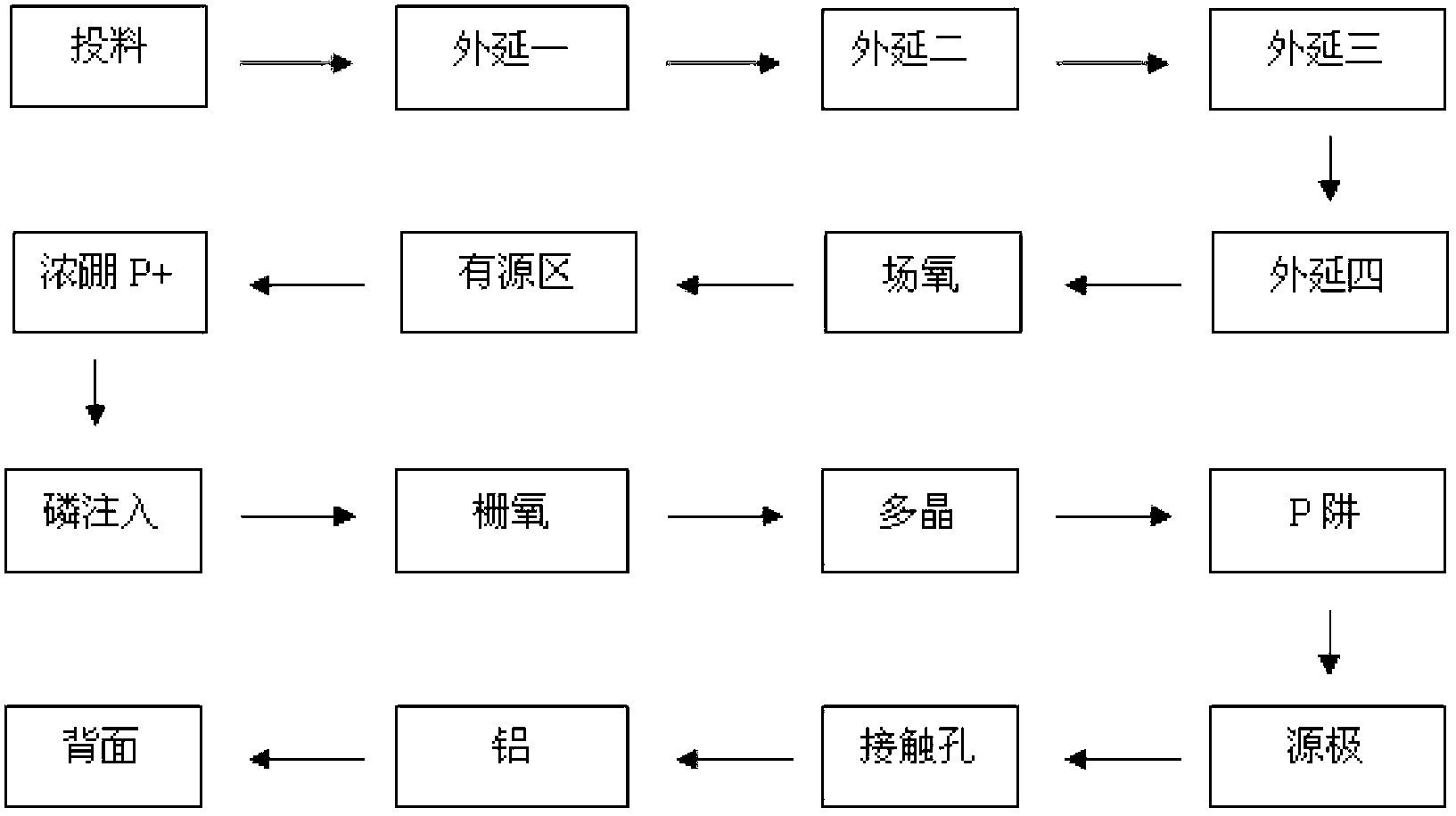

[0046] Such as figure 2 Shown is a composite epitaxy process for manufacturing medium-voltage series vertical double-diffused field effect transistors. The specific implementation method is as follows:

[0047] 1) Feeding: arsenic-doped or antimony-doped substrate silicon wafer material, with a resistivity of 0.03ohm.cm or below.

[0048] 2) The first step of epitaxy: grow N-type epitaxy with a thickness of 4um and a resistivity of 1 ohm.cm. It is used to form a high-concentration transition zone with a high-concentration substrate. On-resistance can be reduced.

[0049] 3) The second step of epitaxy: grow N-type epitaxy with a thickness of 4um and a resistivity of 10 ohm.cm. It is used to epitaxially form a medium-concentration transition region with the high-concentration first part. On-resistance can also be reduced.

[0050] 4) The third step of epitaxy: grow N-type epitaxy with a thickness of 42um and a resistivity of 18 ohm.cm. Provide a withstand voltage layer fo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More