Mixed-media copper-diffusion-resistant blocking layer for copper interconnection and fabrication method of blocking layer

A barrier layer and copper interconnection technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc., can solve the problem of poor consistency and compactness of the diffusion barrier layer, complex process, and thermal damage of devices, etc. problem, achieve the effect of enhancing anti-diffusion ability, simple and feasible process, and preventing failure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

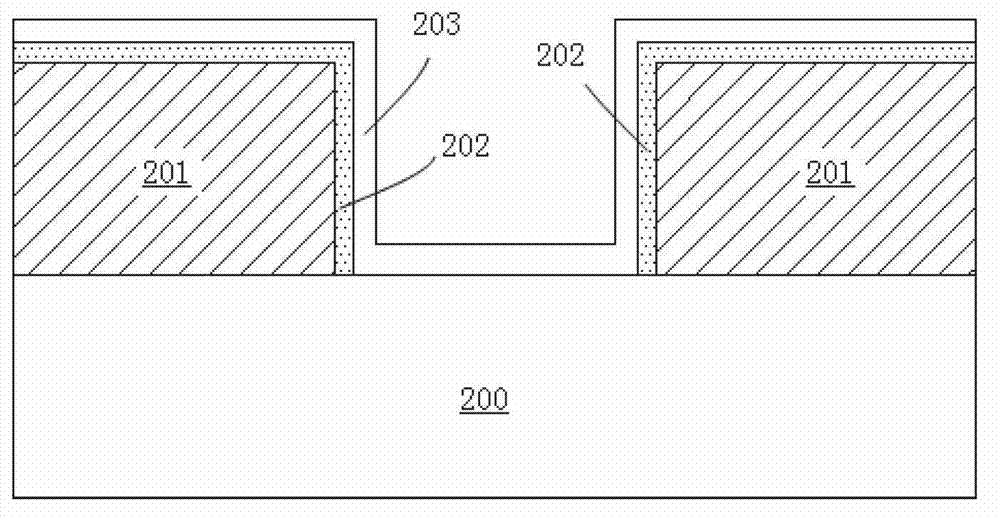

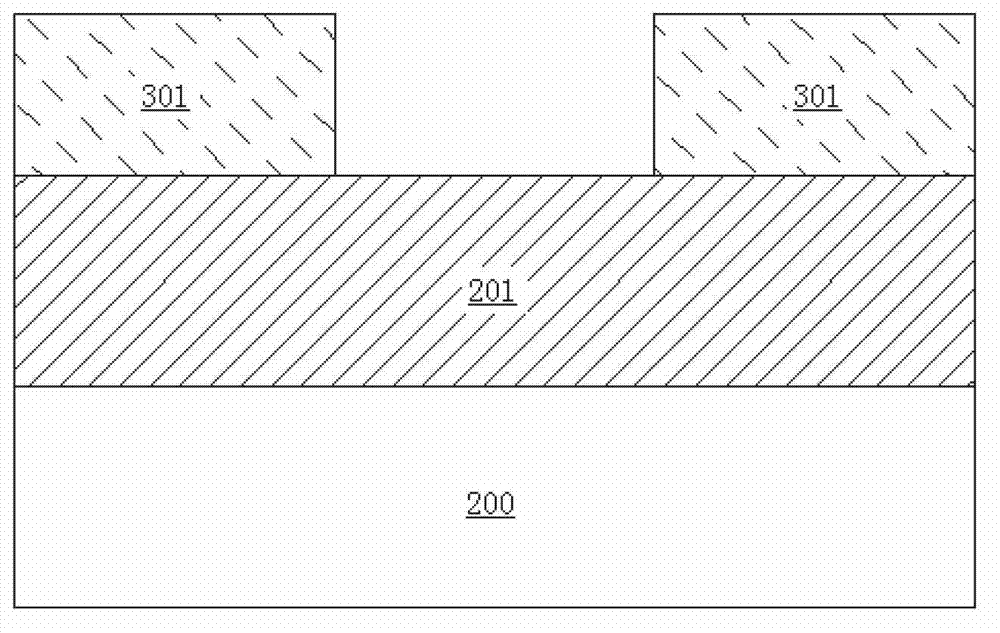

[0028] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments. In the drawings, for the convenience of illustration, the thicknesses of layers and regions are enlarged or reduced, and the sizes shown do not represent actual sizes. Although these figures do not fully reflect the actual size of the device, they still completely reflect the mutual positions between the regions and the constituent structures, especially the upper-lower and adjacent relationships between the constituent structures.

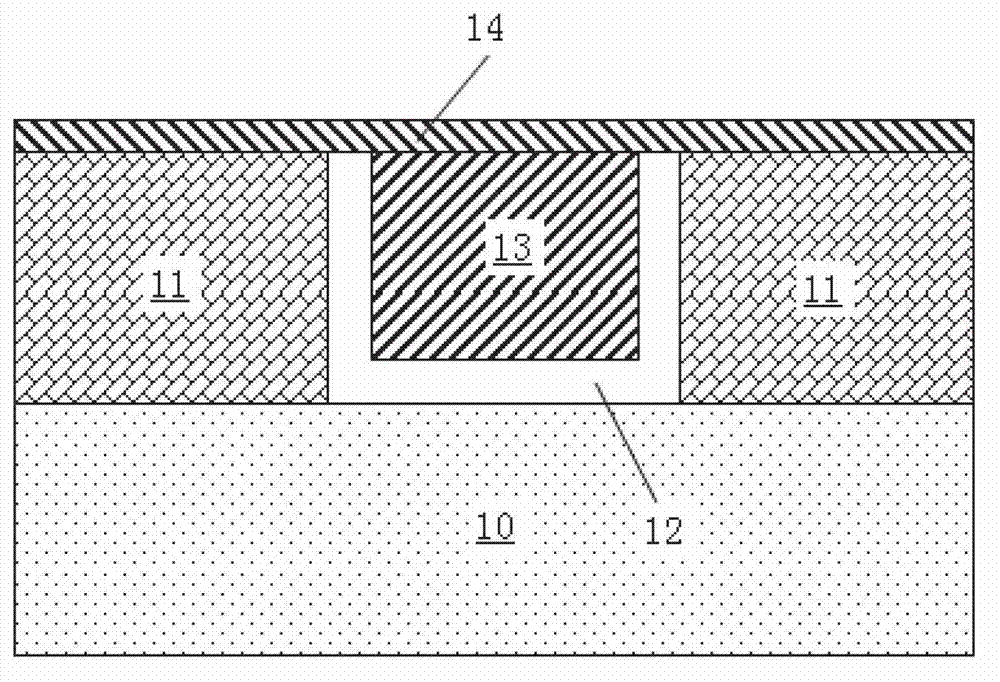

[0029] figure 2 It is a cross-sectional view of an embodiment of the mixed-dielectric anti-copper diffusion barrier layer proposed by the present invention. Such as figure 2 As shown, a low dielectric constant dielectric layer 201 is formed on the semiconductor substrate 200 , and interconnection holes are formed in the low dielectric constant dielectric layer 201 . An oxide layer 202 is formed on the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More