NMOS (N-channel metal oxide semiconductor) device, with GaAs material growing in silicon grooves, based on ART (aspect radio trapping ) structure

A device and trench technology, applied in the field of NMOS devices, can solve the problems of difficulty in maintaining the development mode of logic and storage devices, speed, power consumption, integration, reliability limitations, etc., to achieve good device quality, reduce defects, and reduce growth The effect of temperature

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

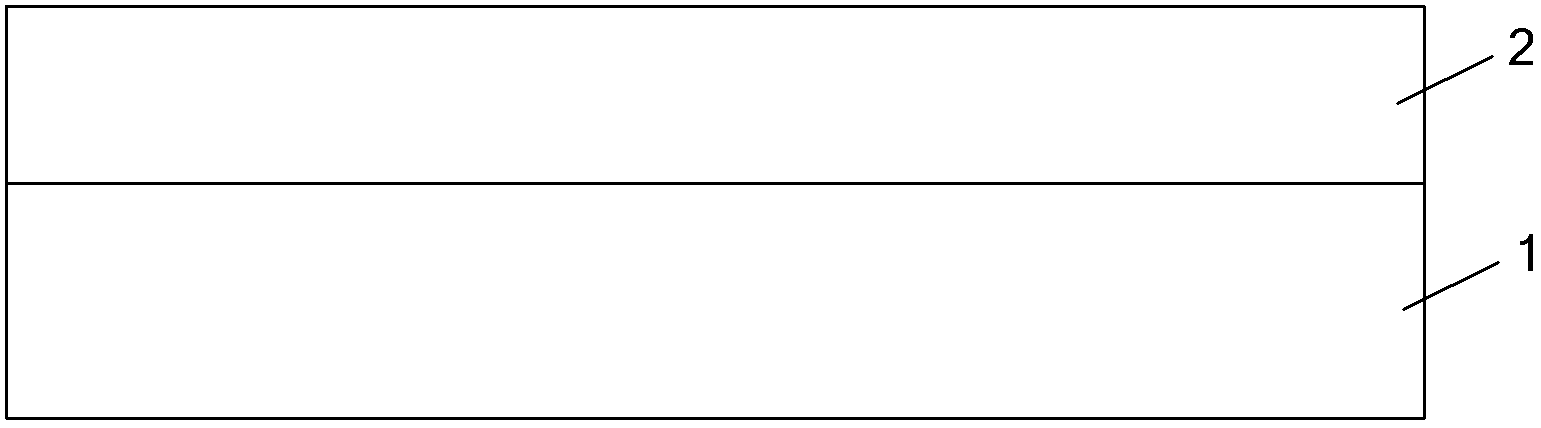

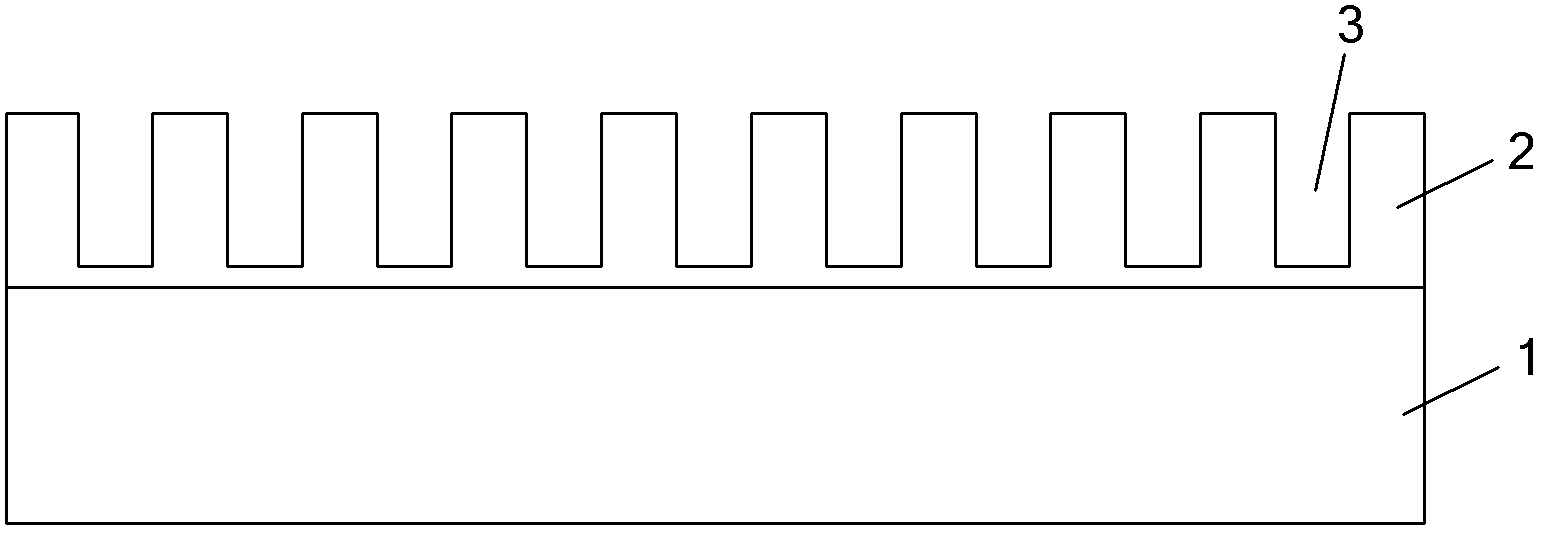

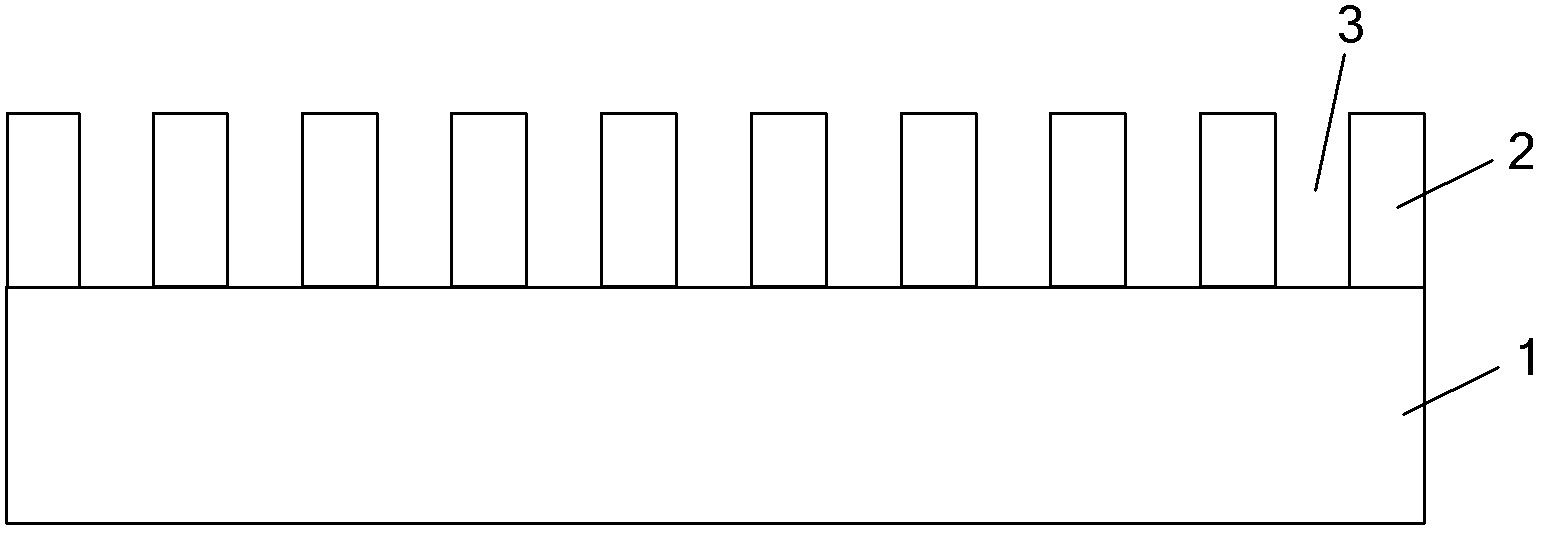

[0031] Epitaxy of high-quality III-V semiconductor materials on silicon substrates is the prerequisite for the preparation of silicon-based high-mobility NMOS. GaAs is a relatively mature III-V semiconductor material. The present invention uses GaAs as a representative of III-V semiconductor materials to study epitaxy. Al 0.3 GaAs is used as a barrier layer to obtain high-quality GaAs materials. The lattice fit of Si and GaAs is larger (4.1%), and the thermal fit is larger (the thermal expansion coefficients of Si and GaAs are 2.59×10 -6 K -1 , 5.75×10 -6 K -1 ), so there are a lot of dislocations. At the same time, due to the epitaxy of polar materials on non-polar substrates and the existence of substrate steps, a ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More