Engineered surfaces for reducing bacterial adhesion

An engineered, bacterial technology used in nanotechnology, cleaning methods and utensils, chemical instruments and methods for materials and surface science to solve problems such as increasing surface complexity, disrupting microbial adhesion, and clogging devices, Achieve improved method efficiency, high thermal uniformity, and reduced shrinkage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example A

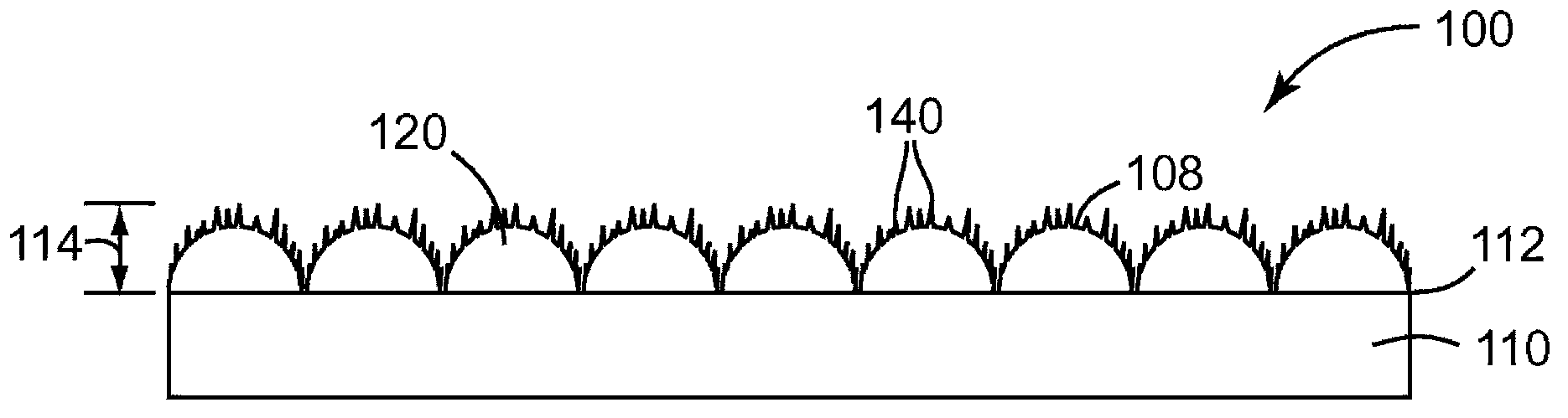

[0110] Generate first-level engineered surface (microstructure)

[0111] In order to manufacture a mother board for microstructures, a photoresist (PR) pattern is manufactured on a silicon wafer by optical lithography. Using the parameters listed in Table 1, a 1500nm-thick silicon dioxide layer was coated by plasma enhanced chemical vapor deposition (PECVD) using Model PlasmaLab System 100 available from Oxford Instruments, Yatton, UK PR microstructure. Use fast deposition rates to produce surface roughness.

[0112] Table 1. Used to deposit SiO 2 Layer condition

[0113] Reactants / conditions

Value

SiH 4

300sccm*

N 2 O

1600sccm

n2

600sccm

Stress

1600mTorr(=213Pa)

Temperature

60℃

High frequency (HF) power

ll0W

[0114] *Standard cubic centimeter

[0115] Then use double-sided tape to adhere the mother board prepared as above to the stainless steel pan. It is then made conductive by electroplating a thin layer of silver. Then at a temperature of 54.4°C (130...

preparation example B

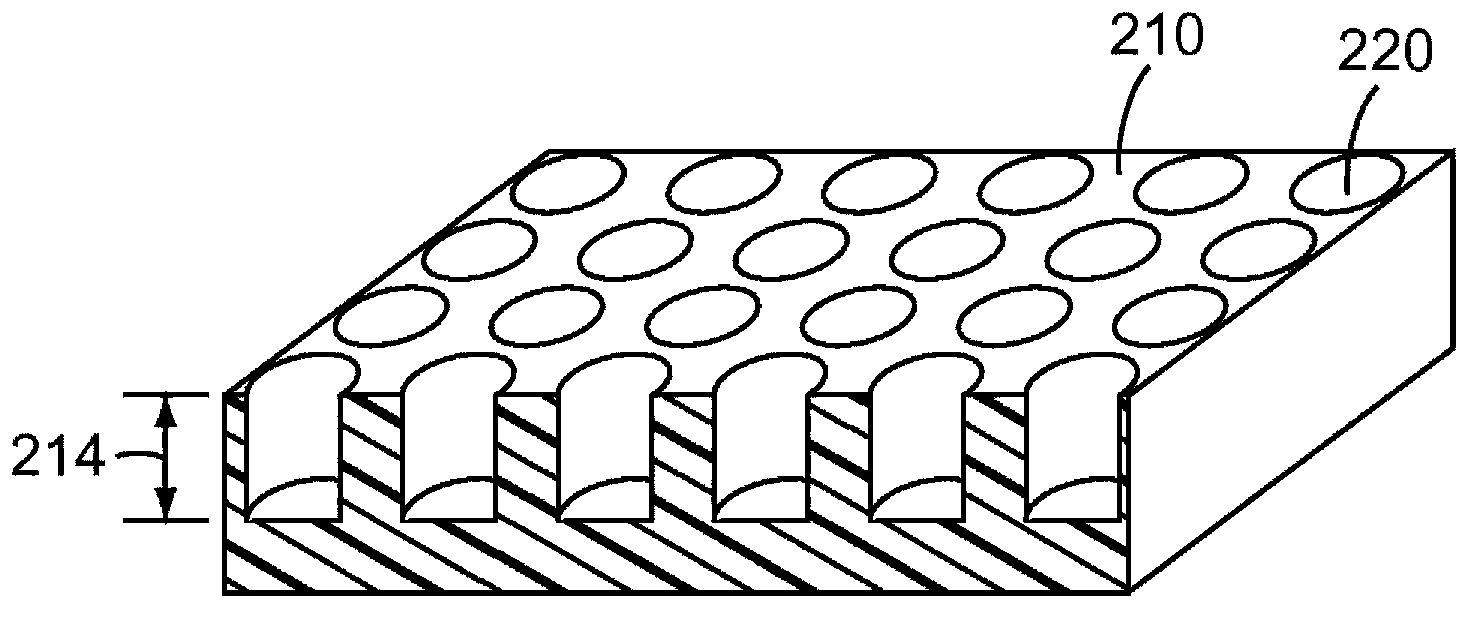

[0124] Generate second-level engineered features on the first-level structure (nanostructure / nanostructure on microstructure) Feature structure)

[0125] Fabrication of nano-featured structures on the surface of parallel triangular rail array

[0126] The second-level topography (nanostructures or nanofeatures) is produced on the substrate (first-level) microstructure, which is first generated by the method described in Preparation Example A above. The base PDMS structure is Comparative Example 3, which is a PDMS surface formed into an array of parallel triangular rungs, wherein the peaks of the rungs have a spacing of 11 μm. PDMS replica first use O 2 Plasma (O 2 Flow: 40sccm, RF power: 75W, P: 65mTorr, time: 15s) processing. This step is followed by immersion of indium tin oxide (ITO) nanoparticles (ITONP, available from Advanced Nano Products Co., Ltd, Chungcheonbuk-do, Chungcheonbuk-do, Korea) at a coating speed of 65mm / min. ,Korea)) suspension in isopropanol (IPA) in a vo...

example 5

[0133] Example 5 was prepared by the same method as Example 4 above, except that the base PDMS structure was an array of parallel triangular rungs with a pitch of 6 μm between rung peaks. Example 5 is shown in Figure 11c-11d in.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More