Manufacturing method of polycrystalline silicon layer and polycrystalline silicon thin film transistor and manufacturing method thereof

A technology of polysilicon thin film and polysilicon layer, which is applied in transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., and can solve the problems of poor uniformity of polysilicon layer, grain boundary defects, uneven grains, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

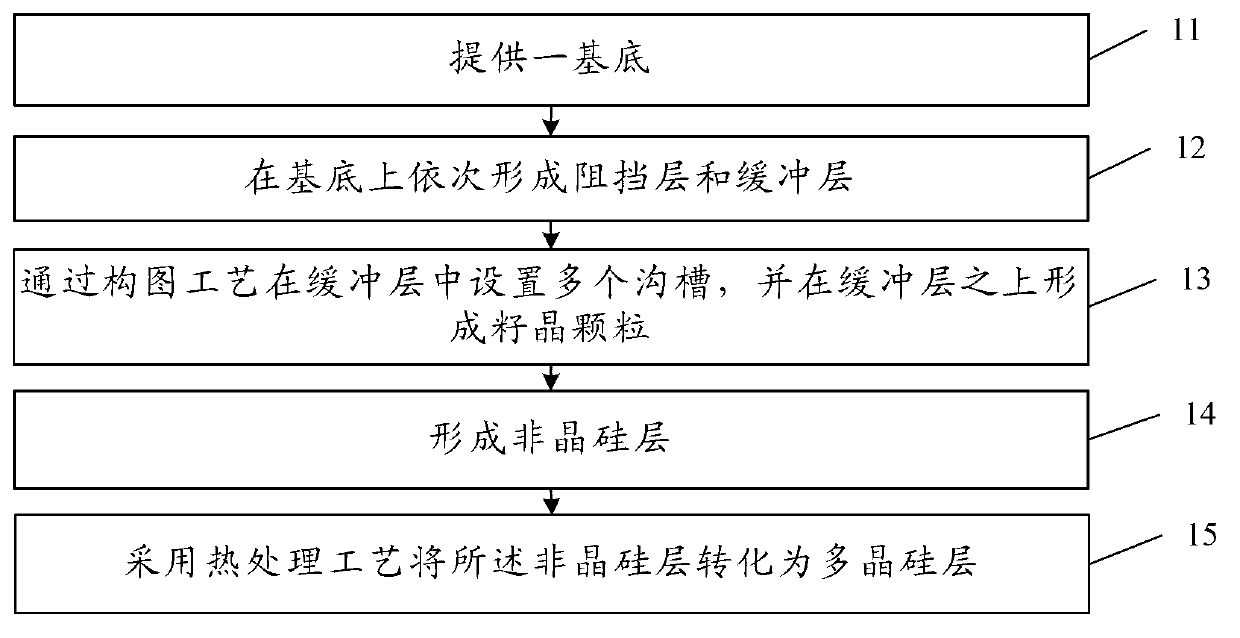

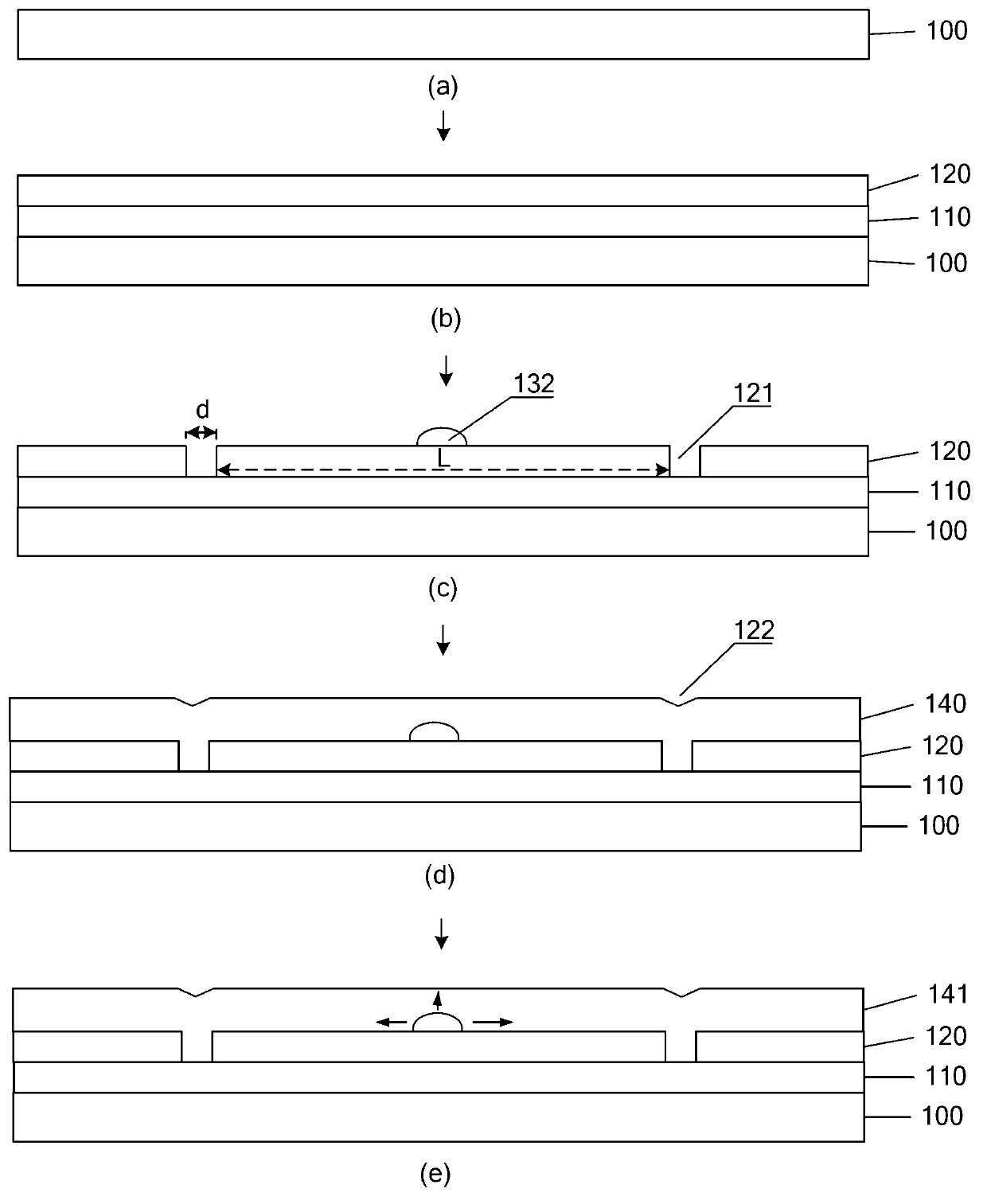

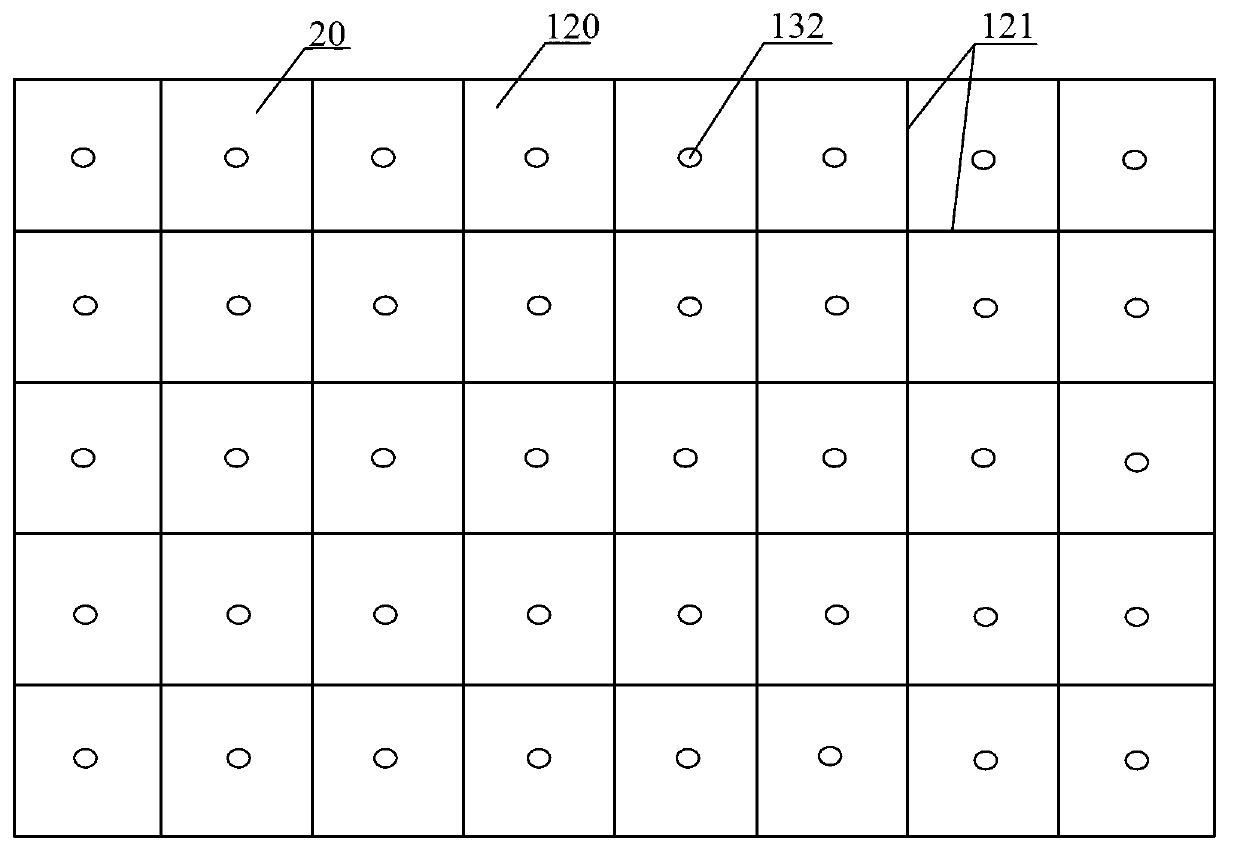

[0056] An embodiment of the present invention provides a method for manufacturing a polysilicon layer, such as figure 1 and figure 2 As shown, the method includes:

[0057] 11. Provide a substrate 100;

[0058] In this step, the substrate 100 is cleaned, and the substrate 100 may be a glass substrate or others.

[0059] 12. If figure 2 As shown in (b), a barrier layer 110 and a buffer layer 120 are sequentially formed on the substrate 100;

[0060]The barrier layer 110 is disposed between the substrate 100 and the buffer layer 120. When a trench is subsequently formed on the buffer layer 120, the barrier layer 110 can be used to prevent the substrate 100 from being etched. In practice, the buffer layer can also be formed directly on the substrate 100. 120, the barrier layer 110 is omitted.

[0061] Optionally, in this step, the barrier layer 110 and the buffer layer 120 are successively deposited on the substrate 100 using an enhanced chemical vapor deposition (PECVD) m...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More