Silicon chip thinning method

A silicon wafer, thinning rate technology, applied in the direction of electrical components, circuits, semiconductor/solid-state device manufacturing, etc., can solve the problems of reducing the lifetime of minority carriers, large leakage current, low injection efficiency, etc., to reduce crystal defects and surface damage and Effects of cracks, defect reduction, heat and stress reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

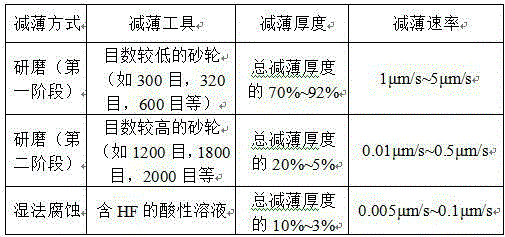

[0023] A method for thinning a silicon wafer. In step 1, a protective material is arranged on the front side of the silicon wafer; in step 2, the back side of the silicon wafer is thinned by grinding in stages. The specific thinning process is divided into two stages: In the first stage, the silicon wafer is thinned with a 300-600 mesh grinding wheel, and the thickness subtracted at this stage is d 1 , the thinning rate is v 1 In the second stage, the 1200-2000 mesh grinding wheel is used to thin the silicon wafer. In this stage, a low-speed grinding and thinning is adopted, and the thinning rate is v 2 , the thickness d of the first-stage thinning 1 is 70%~92% of the total thinning thickness d, the first stage thinning rate v 1 =1μm / s to 5μm / s, the second-stage thinned thickness d 2 It is 20%~5% of the total thinning thickness d, the second stage thinning rate v 2 =0.01μm / s to 0.5μm / s; step 3, put the ground and thinned silicon wafer into the etching solution, and use the...

Embodiment 2

[0025] A method for thinning a silicon wafer. In step 1, a protective material is arranged on the front side of the silicon wafer; in step 2, the back side of the silicon wafer is thinned by grinding in stages. The specific thinning process is divided into two stages: In the first stage, the silicon wafer is thinned with a 300-mesh grinding wheel, and the thickness subtracted at this stage is d 1 , the thinning rate is v 1 In the second stage, a 1200-mesh grinding wheel is used to thin the silicon wafer. In this stage, a low-speed grinding and thinning is adopted, and the thinning rate is v 2 , the thickness d of the first-stage thinning 1 70%% of the total thinning thickness d, the first stage thinning rate v 1 =1μm / s, the thickness d of the second stage thinning 2 is 20% of the total thinning thickness d, the second stage thinning rate v 2 =0.01μ; step 3, put the ground and thinned silicon wafer into the etching solution, and use the grinding wheel at the etching rate v ...

Embodiment 3

[0027] A method for thinning a silicon wafer, step 1, setting a protective material on the front side of the silicon wafer; step 2, thinning the back side of the silicon wafer by grinding in stages, and the specific thinning process is divided into two stages: In the first stage, the silicon wafer is thinned with a 600-mesh grinding wheel, and the thickness subtracted at this stage is d 1 , the thinning rate is v 1 , the second stage uses a 2000-mesh grinding wheel to thin the silicon wafer. In this stage, a low-speed grinding and thinning is adopted, and the thinning rate is v 2 , the thickness d of the first-stage thinning 1 is 92% of the total thinning thickness d, the first stage thinning rate v 1 = 5μm / s, the second-stage thinned thickness d 2 5% of the total thinning thickness d, the second stage thinning rate v 2 = 0.5μm / s; step 3, put the thinned silicon wafer into the etching solution, use the grinding wheel at the etching rate v 3 For wet etching, the corrosion ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More