An ultra-low loss device of drain-source region dielectric/pn junction isolation front gate p/n-mosfet radio frequency switch based on soi process

A technology of front gate and source region, applied in semiconductor devices, electrical components, transistors, etc., can solve problems such as being unfavorable to improve the overall performance of devices and systems, large losses, and low device efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

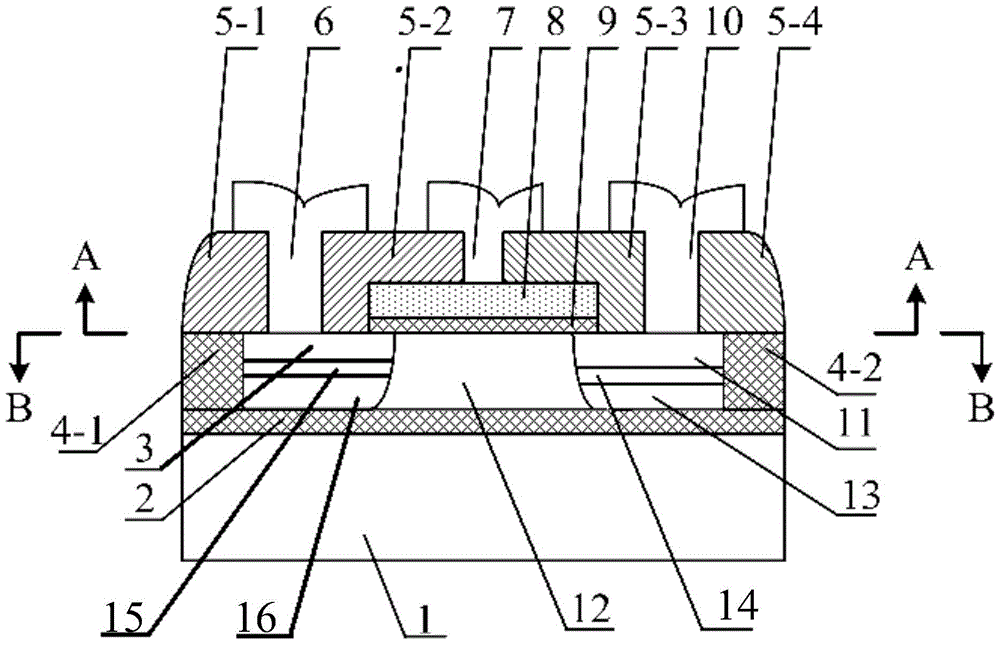

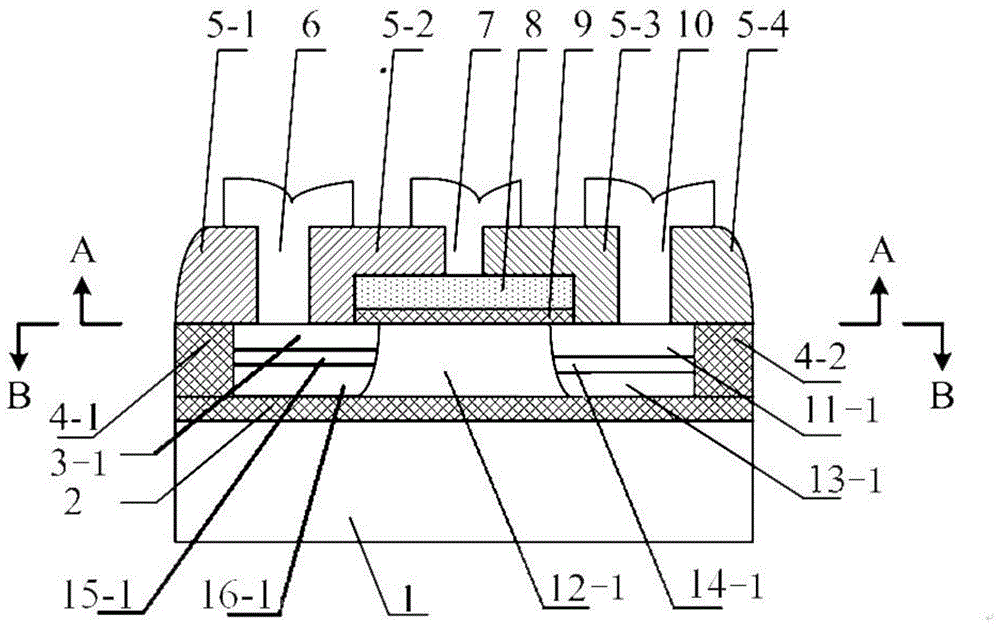

[0016] Such as figure 1 As shown, a drain-source region dielectric / PN junction isolation front gate P-MOSFET radio frequency switch ultra-low loss device based on SOI process, including P-type semiconductor substrate 1, buried oxide 2, N-type channel region 12, front gate P-type source region 3 of MOSFET, P-type drain region 11 of front gate MOSFET, P-type drain region 13 of back gate MOSFET, P-type drain isolation region 14, P-type source region 3 of front gate MOSFET, back gate MOSFET P-type drain region 16, P-type source region isolation region 15, deep trench isolation region (4-1, 4-2); buried oxide layer 2 is covered on P-type semiconductor substrate 1, and N-type channel region 12 is set On the buried oxide layer 2, deep trench isolation regions (4-1, 4-2) are arranged on the buried oxide layer 2 and surround the N-type channel region 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More