A Method of Saving Vdmosfet Chip Area in Low and Medium Voltage

A chip area, low voltage technology, applied in the direction of circuits, electrical components, electrical solid devices, etc., can solve the problems of increased product cost, large VDMOS area, long terminal diffusion area 6, etc., to increase the number of chip outputs and reduce Effect of chip area and cost reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] A kind of method of saving the VDMOSFET chip area of middle and low voltage of the present invention, comprises the steps:

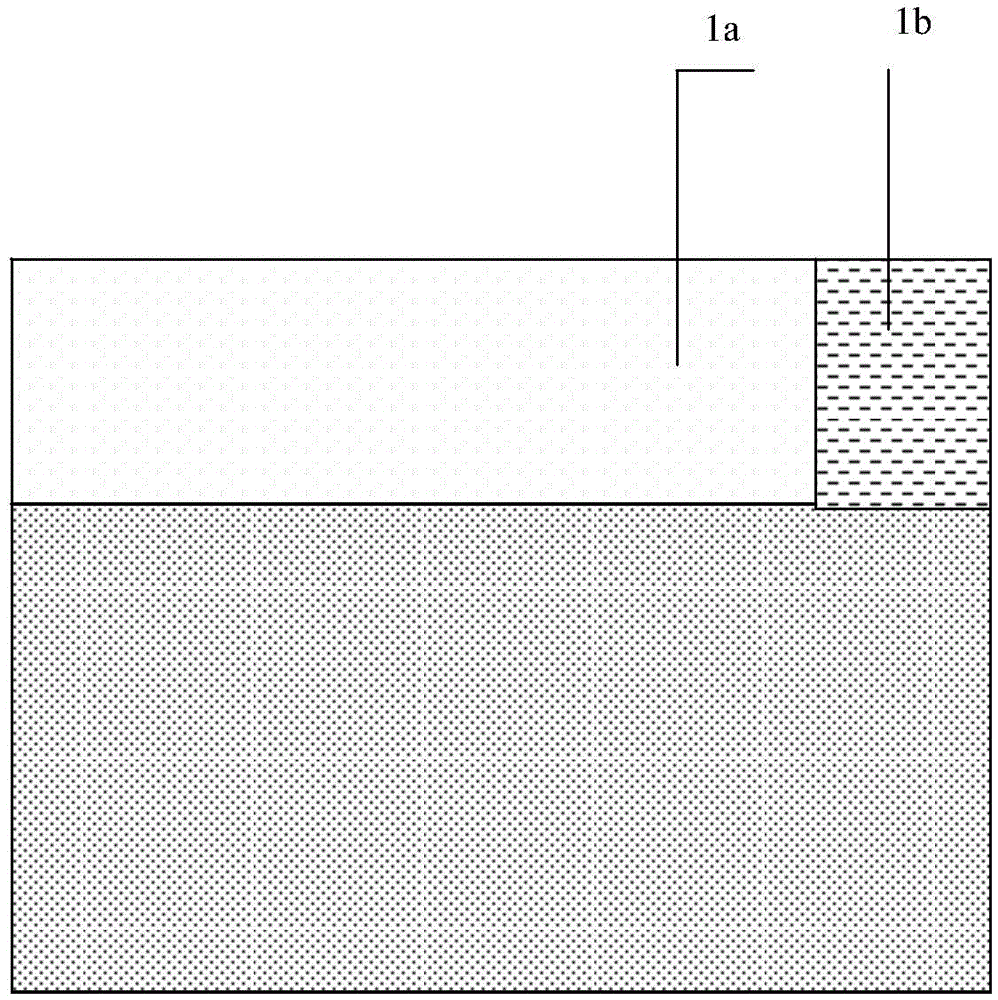

[0022] (1) if figure 1 As shown, an active region 1a and an unetched region 1b are formed by etching on polysilicon;

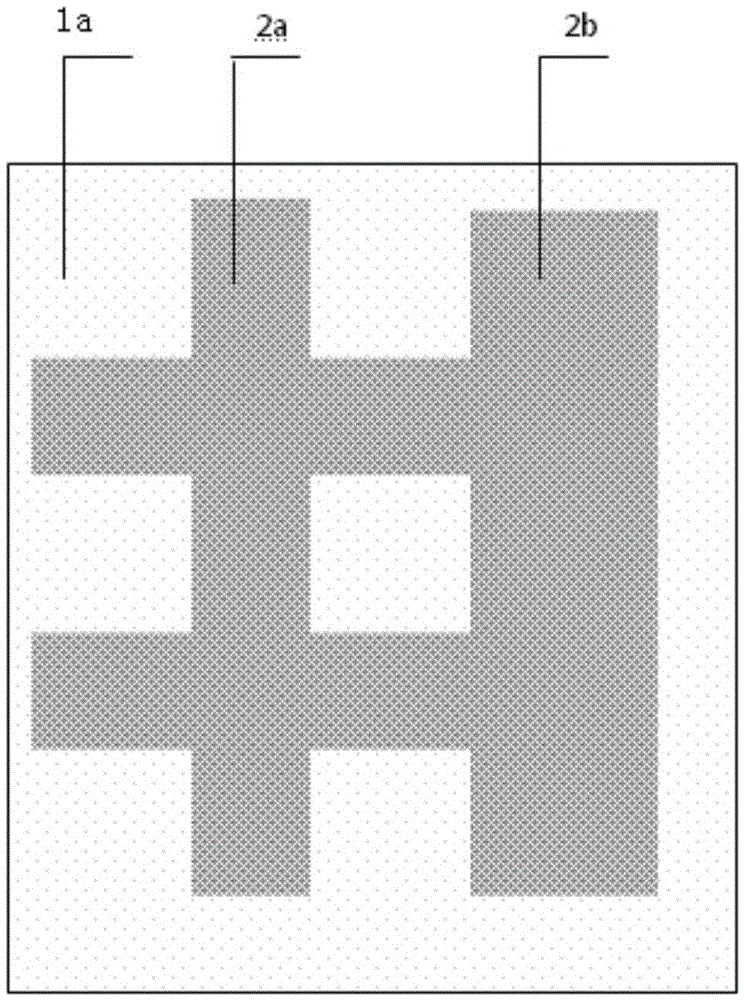

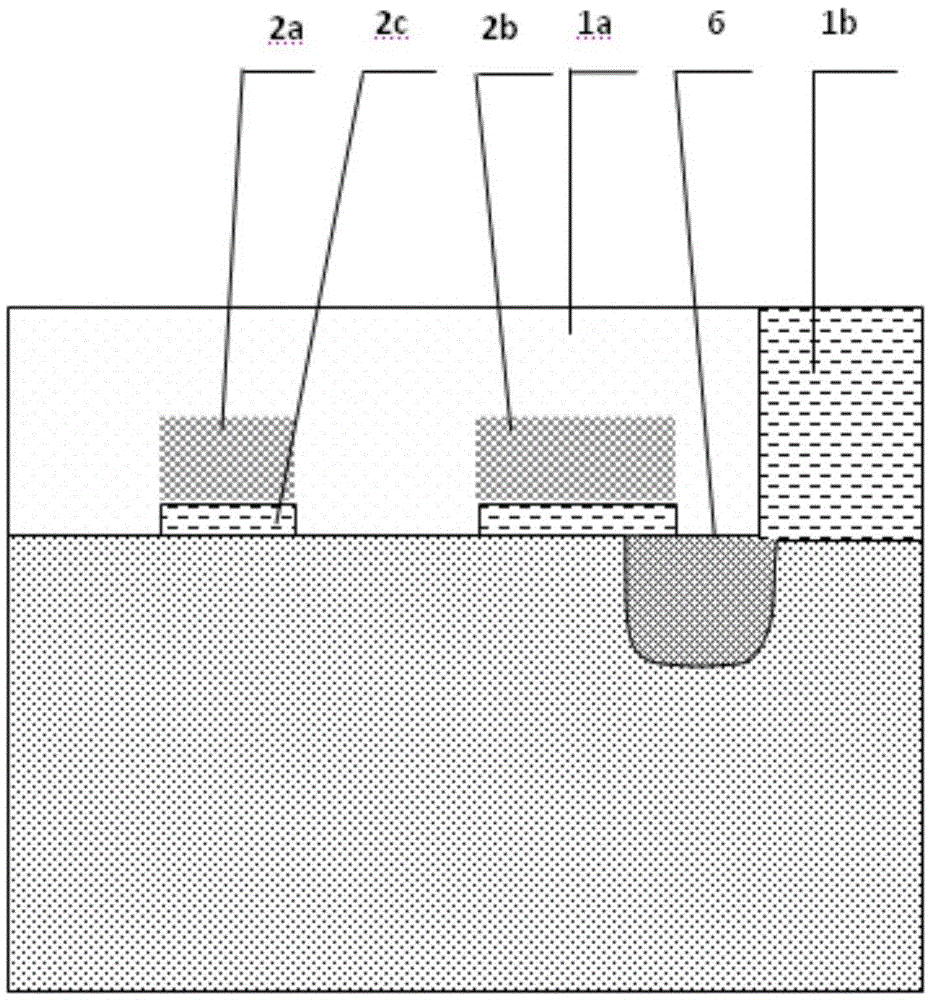

[0023] (2) As shown in Figure 2, a gate oxide region 2c and a polysilicon region 2 are formed by deposition on the active region 1a, wherein the polysilicon region 2 is located above the gate oxide region 2c; the polysilicon region 2 includes a polysilicon lead region 2a and a polysilicon region 2 Termination structure region 2b; terminal diffusion region 6 is formed by diffusion between the polysilicon termination structure region 2b and the unetched region 1b;

[0024] (3) if image 3 As shown, an N+ source region 3 is formed by diffusion under the polysilicon lead region 2a and between the polysilicon lead region 2a and the polysilicon termination structure region 2b;

[0025] (4) if Figure 4 As shown, a protective film...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More