Patents

Literature

43results about How to "Guaranteed Electrical Characteristics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

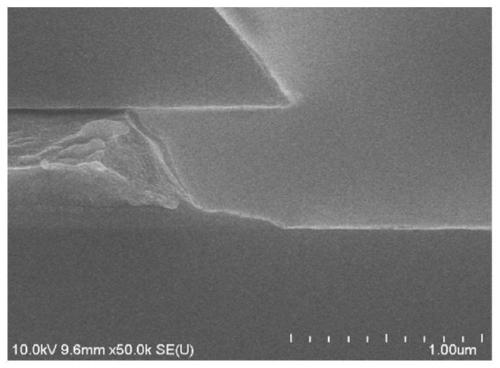

Unsealing method for flip chip device

ActiveCN104008956AGuaranteed completenessGuaranteed electrical characteristicsSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingScanning acoustic microscopeSilicon

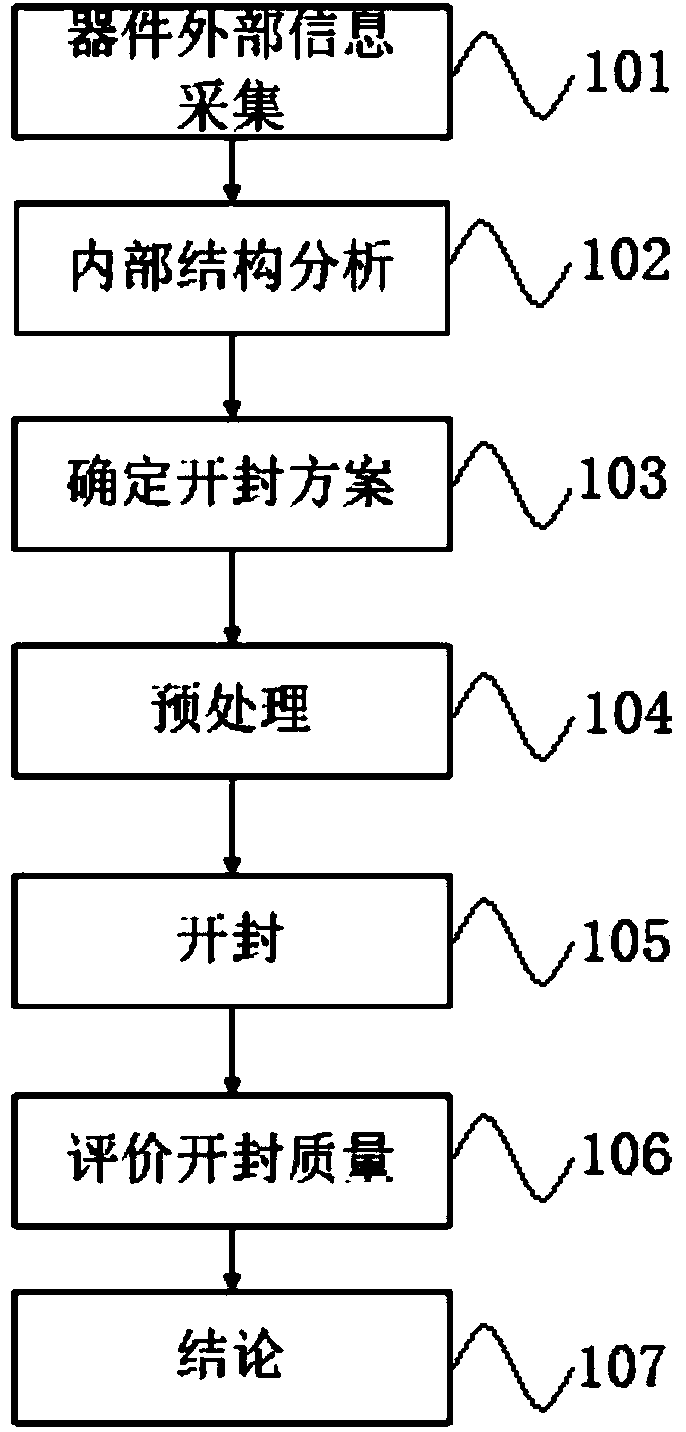

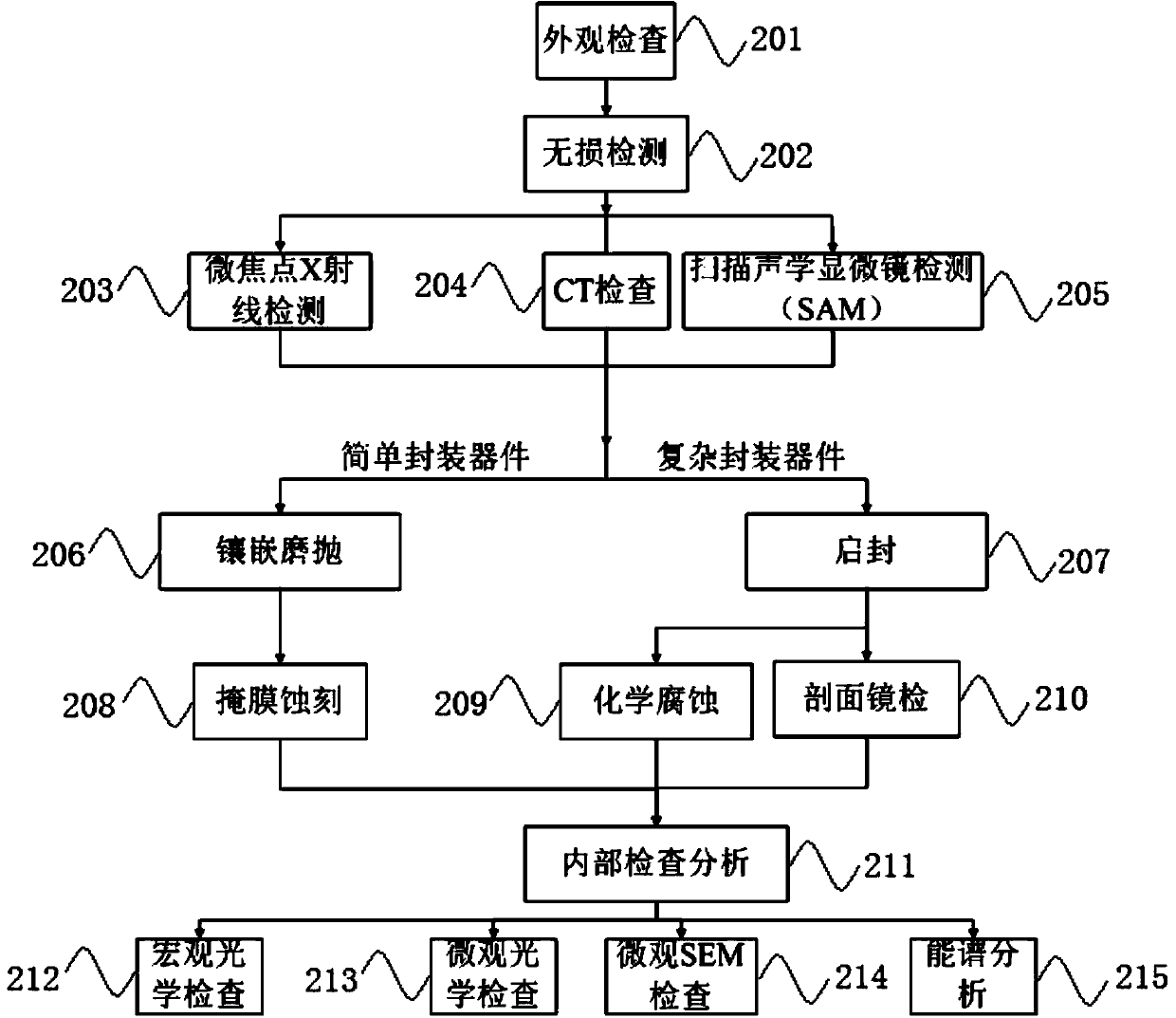

The invention discloses an unsealing method for a flip chip device. The method comprises the steps that a three-dimensional microscope is used for observing a device to be unsealed, and the appearance size, packaging thickness, packaging forms and packaging materials of the device to be unsealed are measured; one or more of a scanning acoustic microscope, a micro-focus X ray detector and a CT detector are selected to observe and record the device to be unsealed; the unsealing scheme of the device is determined according to the type of the device and the detecting results; embedding polishing or shell unsealing is used for carrying out unsealing pre-processing on the device to be unsealed; one or more of a mask etching method, a chemical etching method and a section microscopy method are used for carrying out chemical unsealing on the device to be unsealed; the interior technical parameters of the unsealed device are detected, evaluated and analyzed. Compared with a traditional unsealing method for a flip chip technology device, the unsealing method for the flip chip device has the advantages that the unsealing quality is greatly improved, and completeness and electrical characteristics of an unsealed silicon wafer are guaranteed.

Owner:CASIC DEFENSE TECH RES & TEST CENT

Composite material high-power RF coaxial connector

InactiveCN101247014ALow costGuaranteed Electrical CharacteristicsCoupling contact membersCouplings bases/casesElectrical conductorEngineering

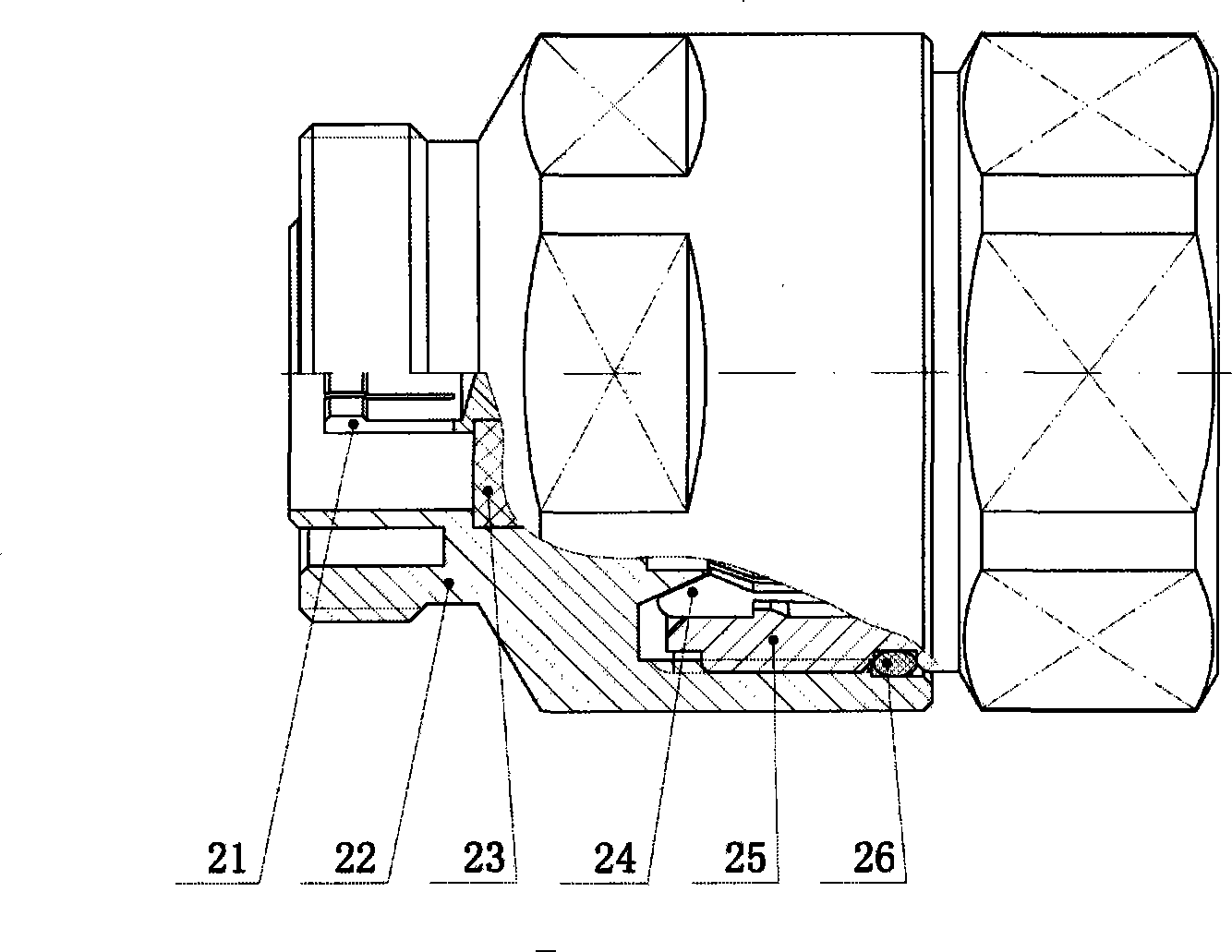

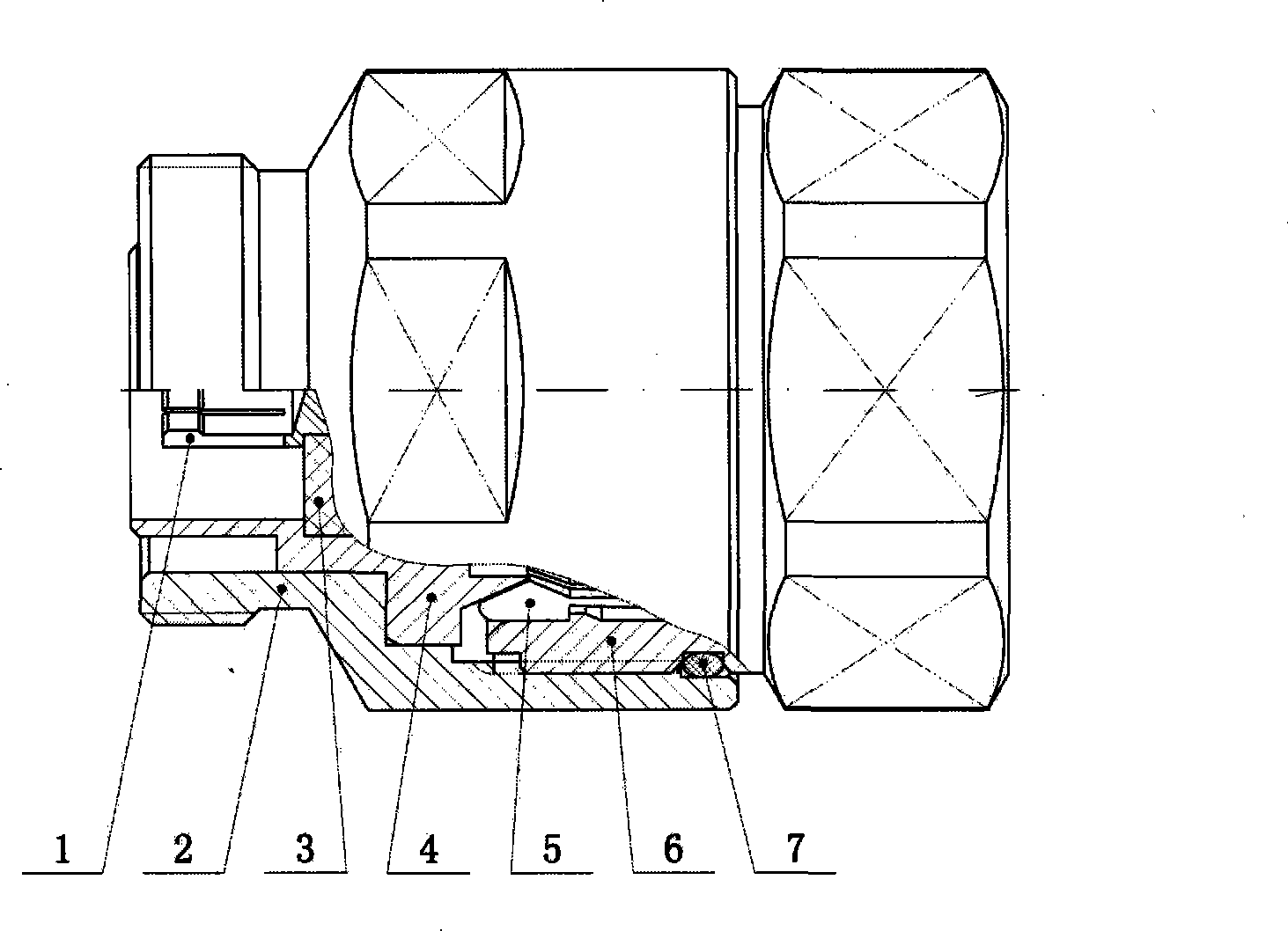

The present invention discloses a compound material high power RF coaxial linker which comprises of inner conductor, crust, insulation, outer conductor, cable clip, rear thread sleeve and seal ring. Insulation is set between inner conductor and outer conductor, seal ring is set between crust and rear thread sleeve, crust coats on surface of outer conductor, cable clip and rear thread sleeve, the inner conductor and outer conductor on circuit are made from copper alloy, the crust and rear thread sleeve is made from aluminum alloy or stainless steel or project plastic. The present invention changes the original conductor made from copper alloy totally to conductor made from compound material, reduces cost under the premise of ensuring product capability, improves the market competition of products and meets the requirement of market.

Owner:JIANGSU JST TECH

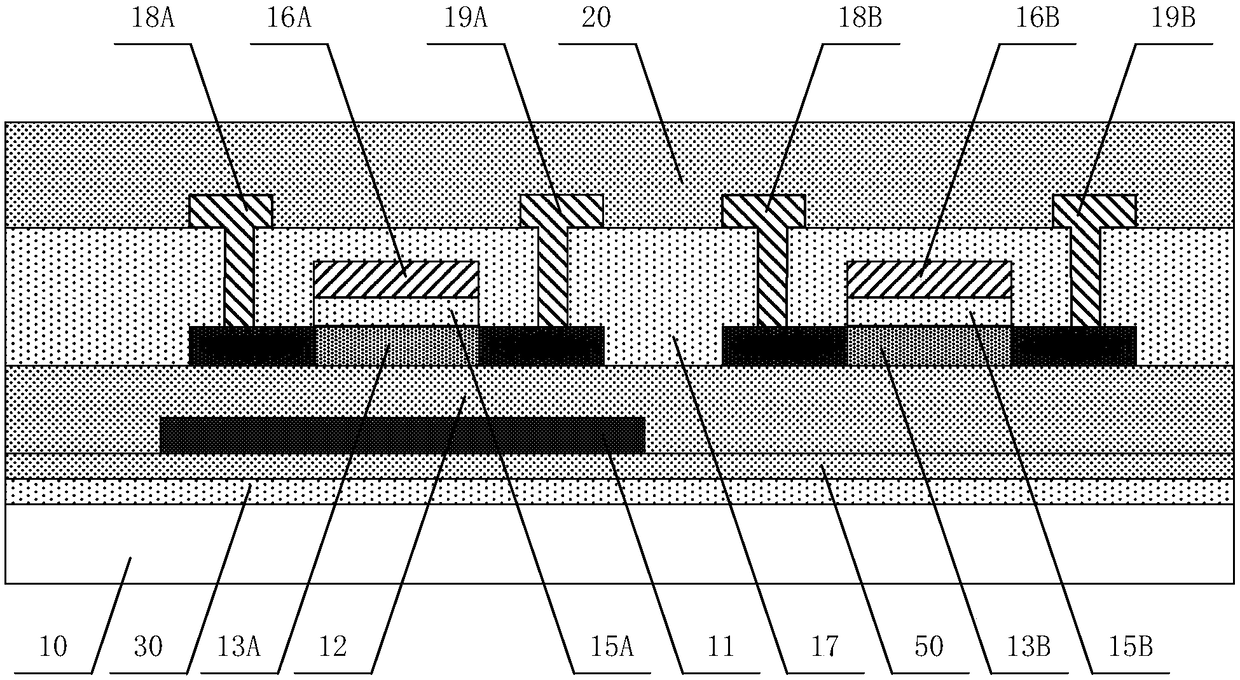

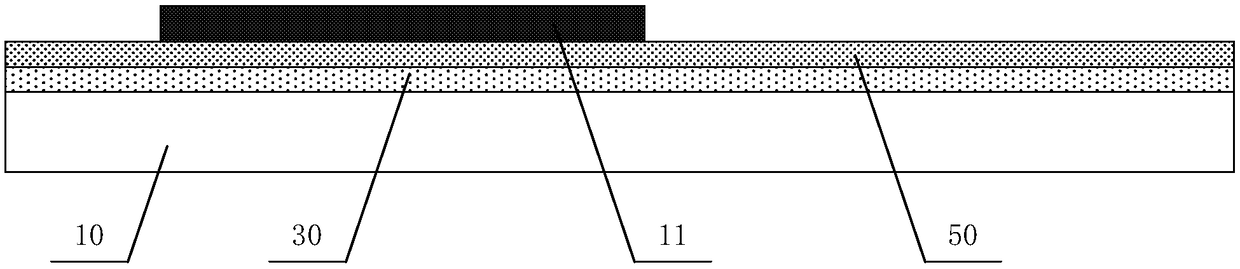

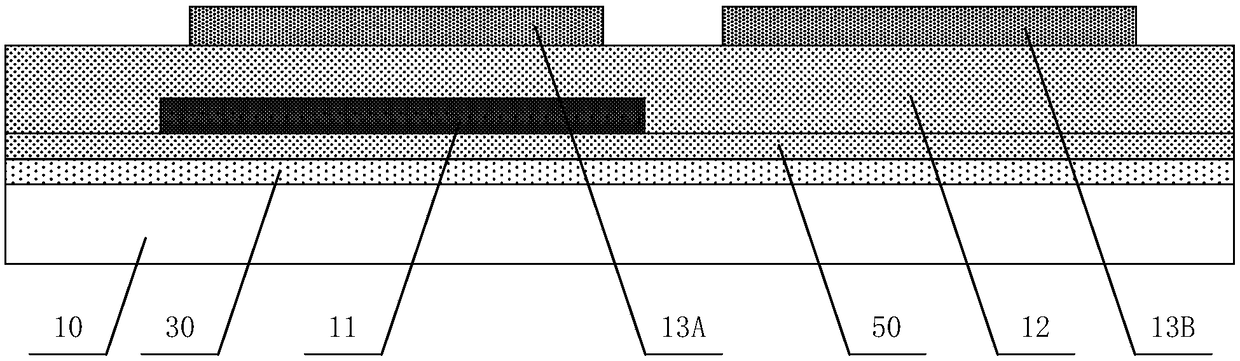

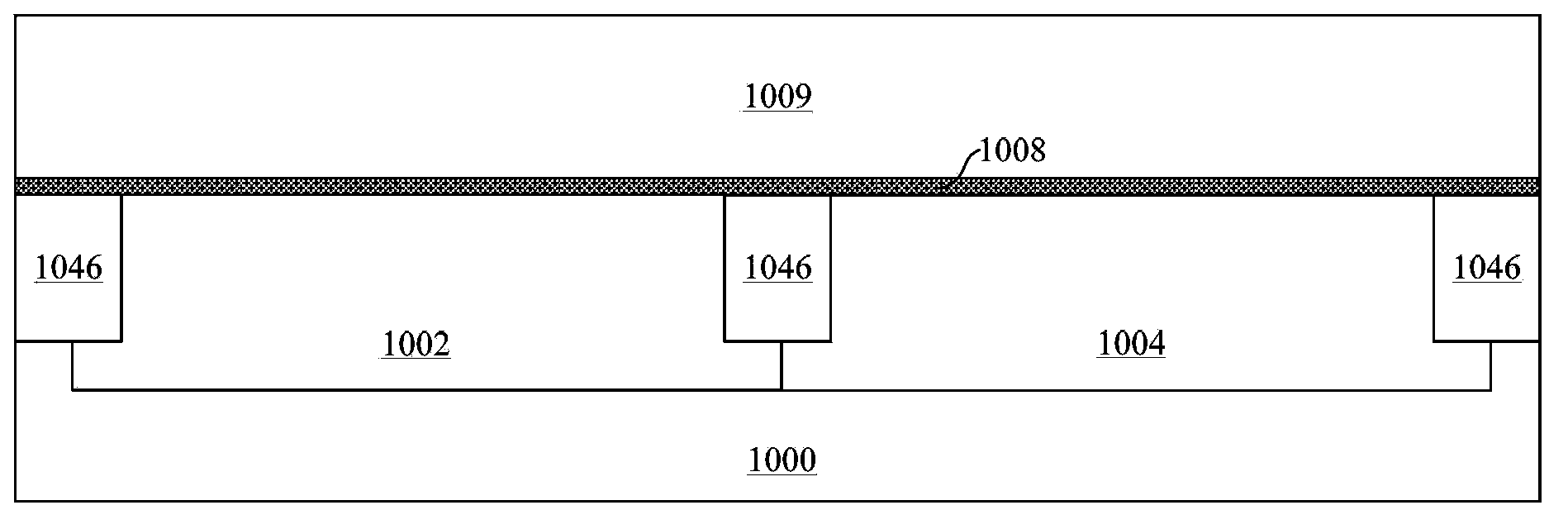

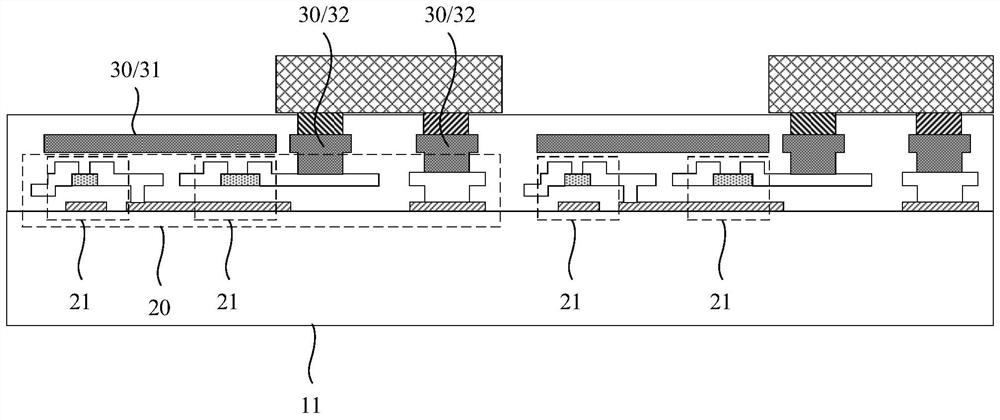

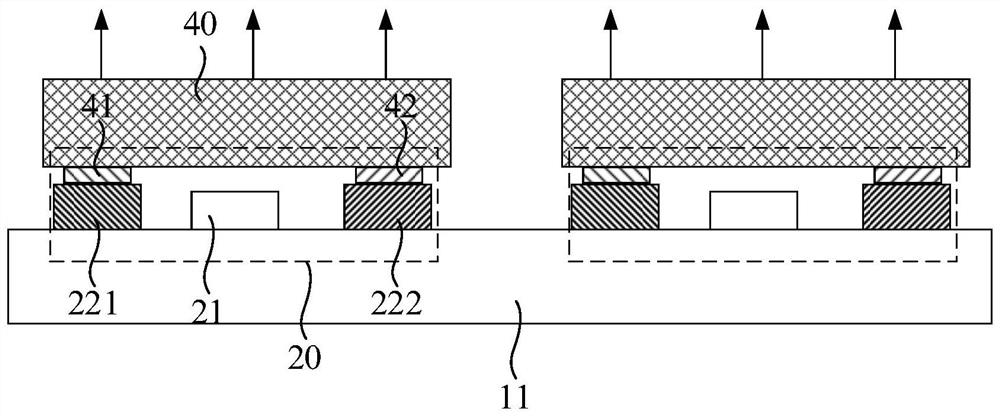

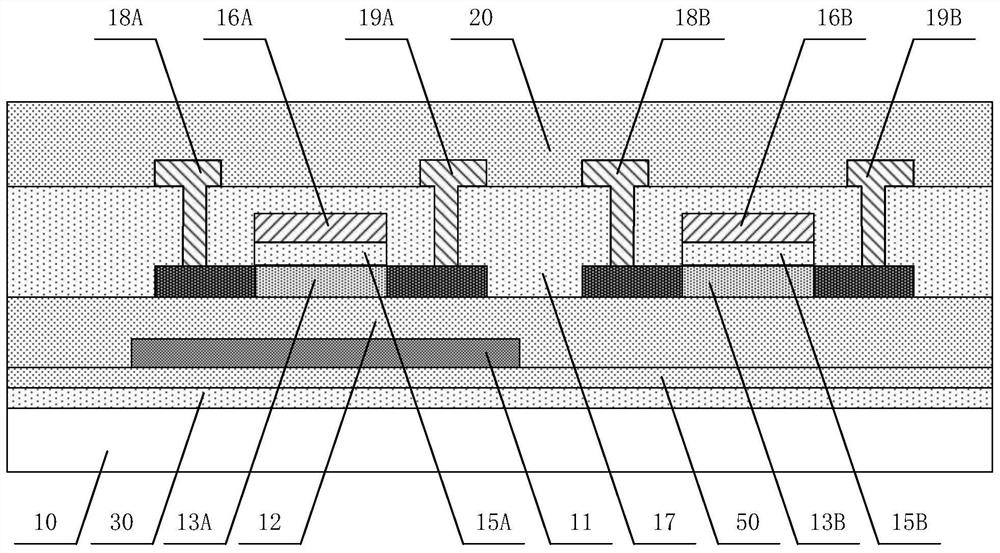

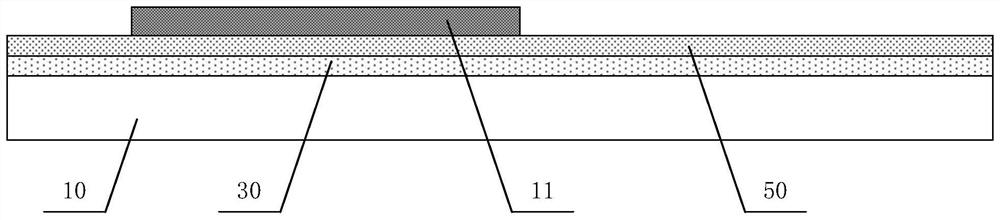

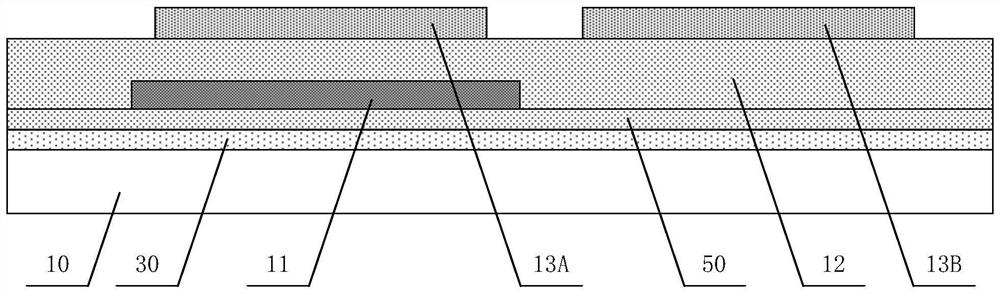

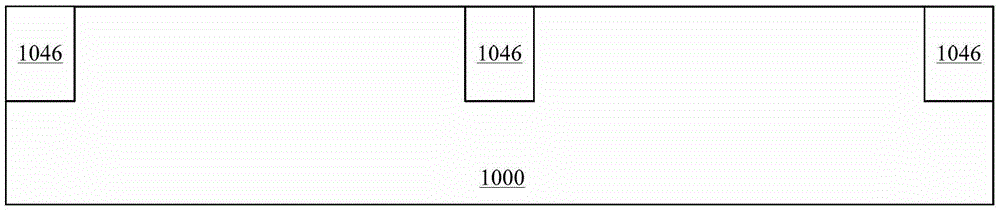

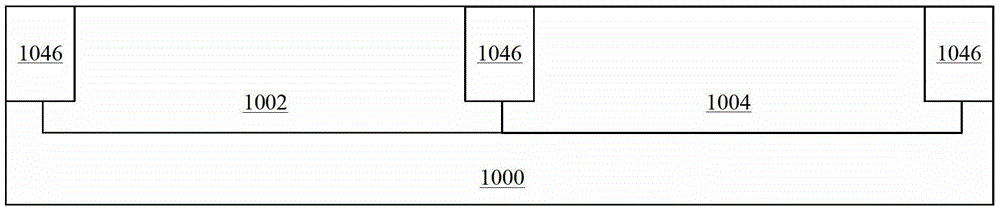

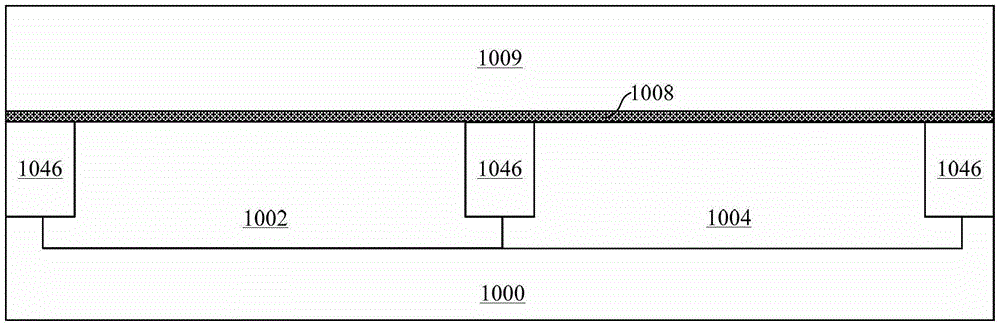

Display backplane, preparation method thereof, and display device

ActiveCN109148482AImprove work performanceImprove cooling efficiencySemiconductor/solid-state device detailsSolid-state devicesDisplay deviceSemiconductor

An embodiment of the present invention provides a display backplane, a preparation method thereof, and a display device. The display backplane includes a substrate, a transparent heat conduction layerdisposed on the substrate, and an array structure layer disposed on the heat conduction layer. The array structure layer includes a light shielding layer, a first thin film transistor and a second thin film transistor, and the light shielding layer is disposed between the transparent heat conduction layer and the first thin film transistor. The transparent heat conductive layer comprises a transparent conductive layer, a transparent semiconductor layer or a transparent conductive layer and a transparent semiconductor layer. As that transparent heat conduction lay is arranged between the substrate and the array structure lay, the invention can effectively solve the problem that the characteristics of the driving thin film transistor and the switching thin film transistor of the prior OLEDdisplay device are separated.

Owner:BOE TECH GRP CO LTD +1

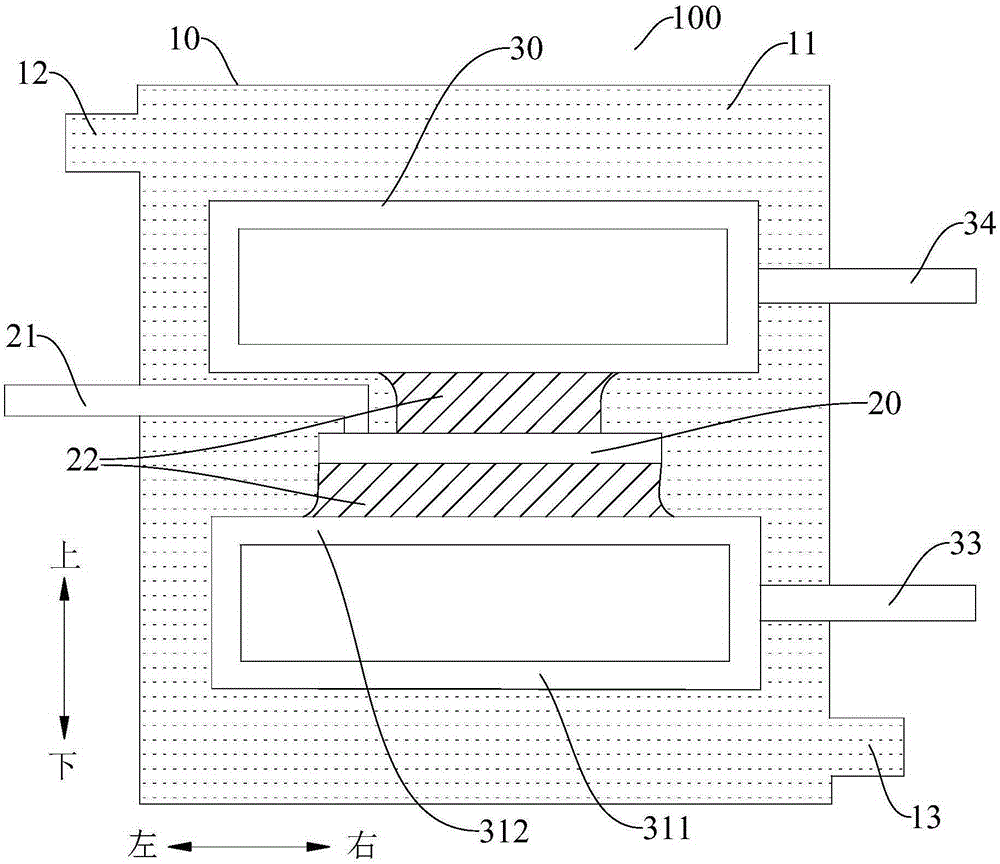

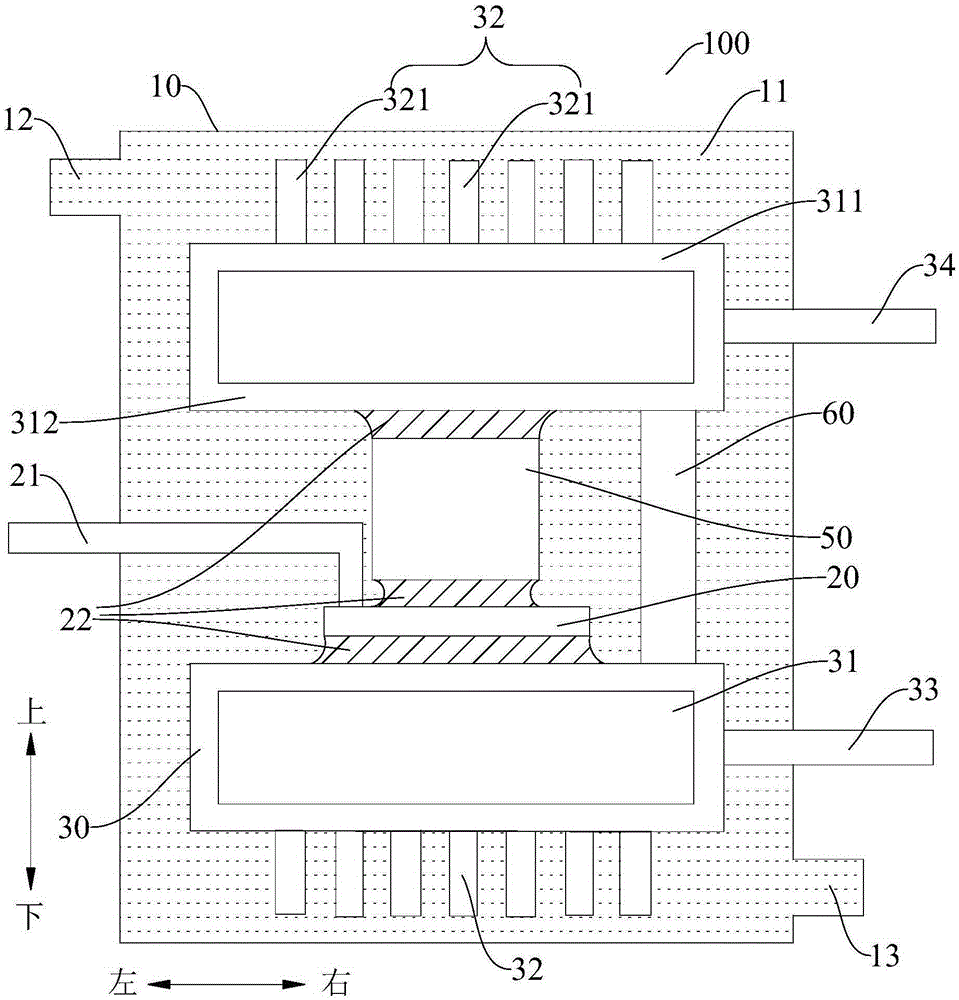

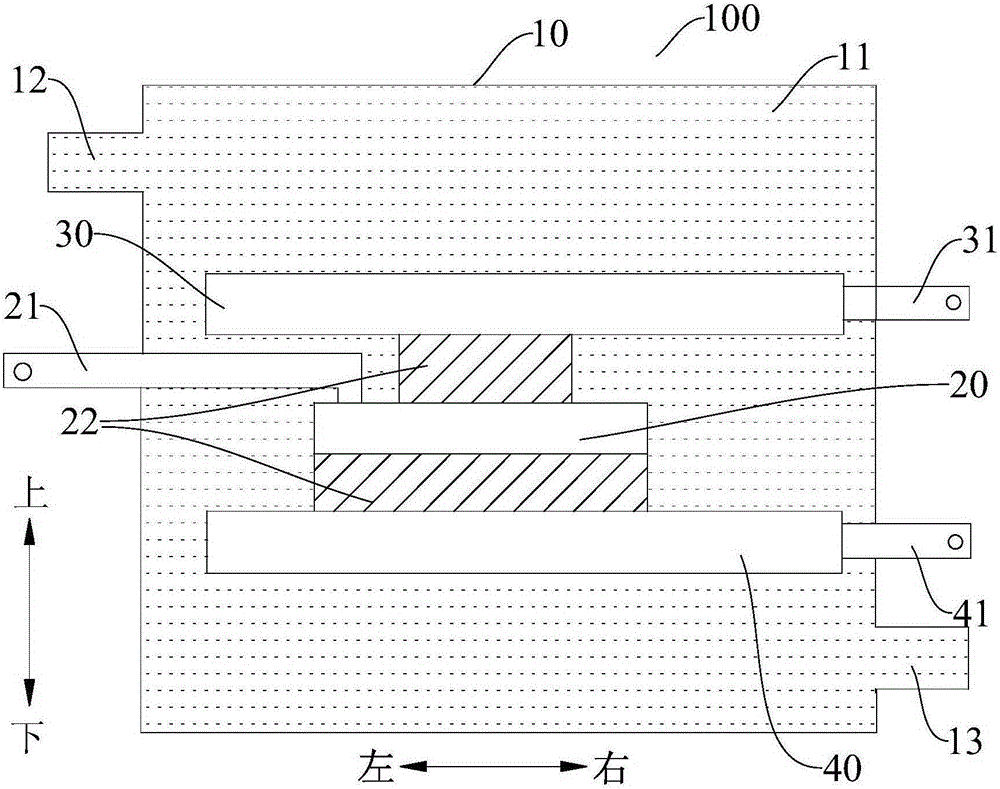

Power module and vehicle having same

ActiveCN106558563AImprove cooling effectImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesEvaporationCopper

The present invention discloses a power module and a vehicle having the same. The power module comprises: a housing, wherein a holding cavity is limited in the housing, and the holding cavity is internally provided with insulation materials; a power chip and two panel heat pipes which are all arranged in the holding cavity and wrapped by the insulation materials, each panel heat pipe has one condensation portion and an evaporation portion, the evaporation portions of the two panel heat pipes are respectively arranged at the upper and lower surfaces of the power chip, and electrodes are led out from the power chip and each panel heat pipe. According to the power module provided by the embodiment of the invention, the upper and lower surfaces of the power chip can realize heat dissipation at the same time to enhance the heat dissipation function of the power module and improve the reliability of the power module; and moreover, the power module omits the copper-clad ceramic substrate in the prior art to simplify the structure and the production process, the insulation materials are arranged in the housing to play an effect of electrical insulation so as to allow each device in the housing to ensure the independent electrical features.

Owner:BYD SEMICON CO LTD

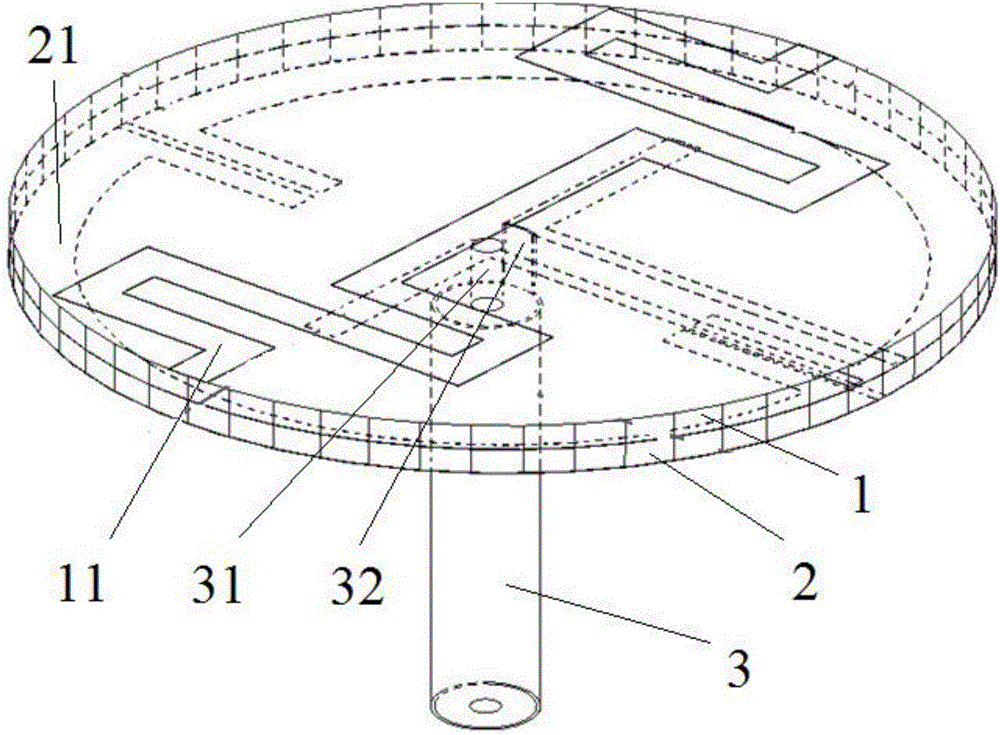

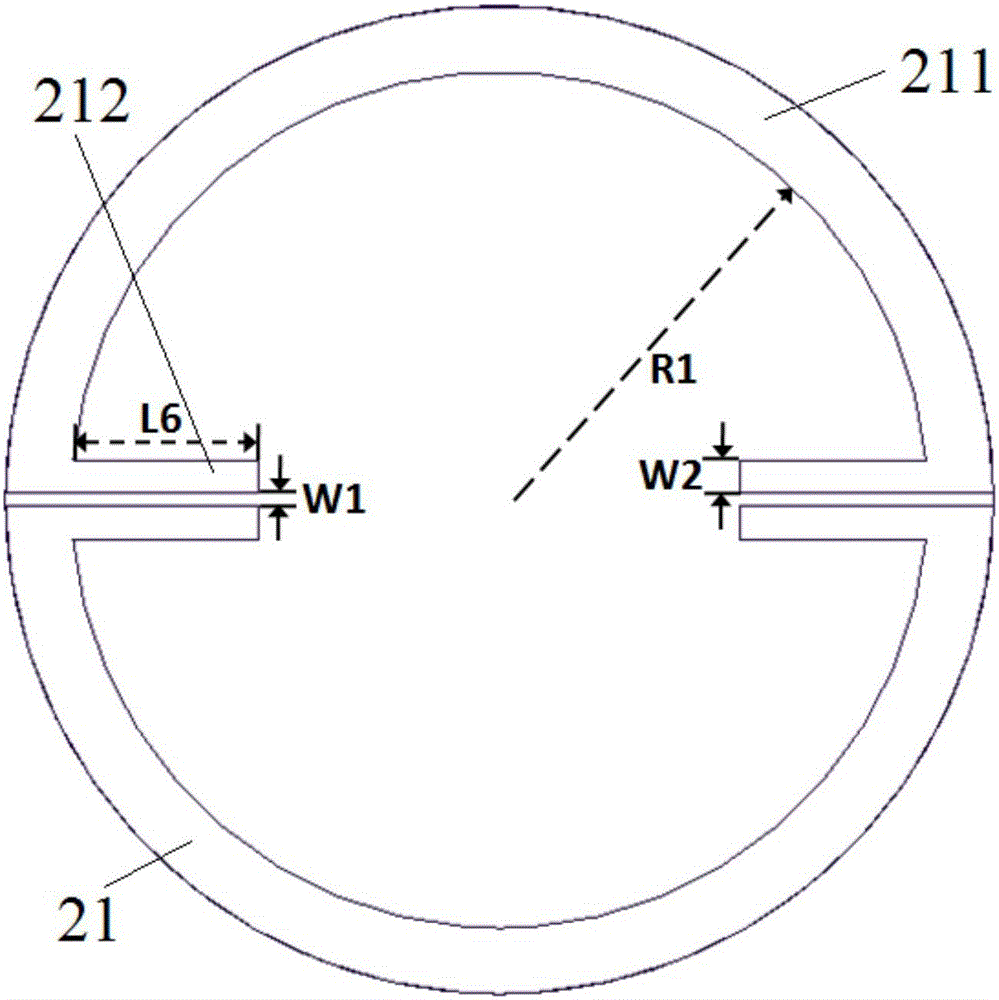

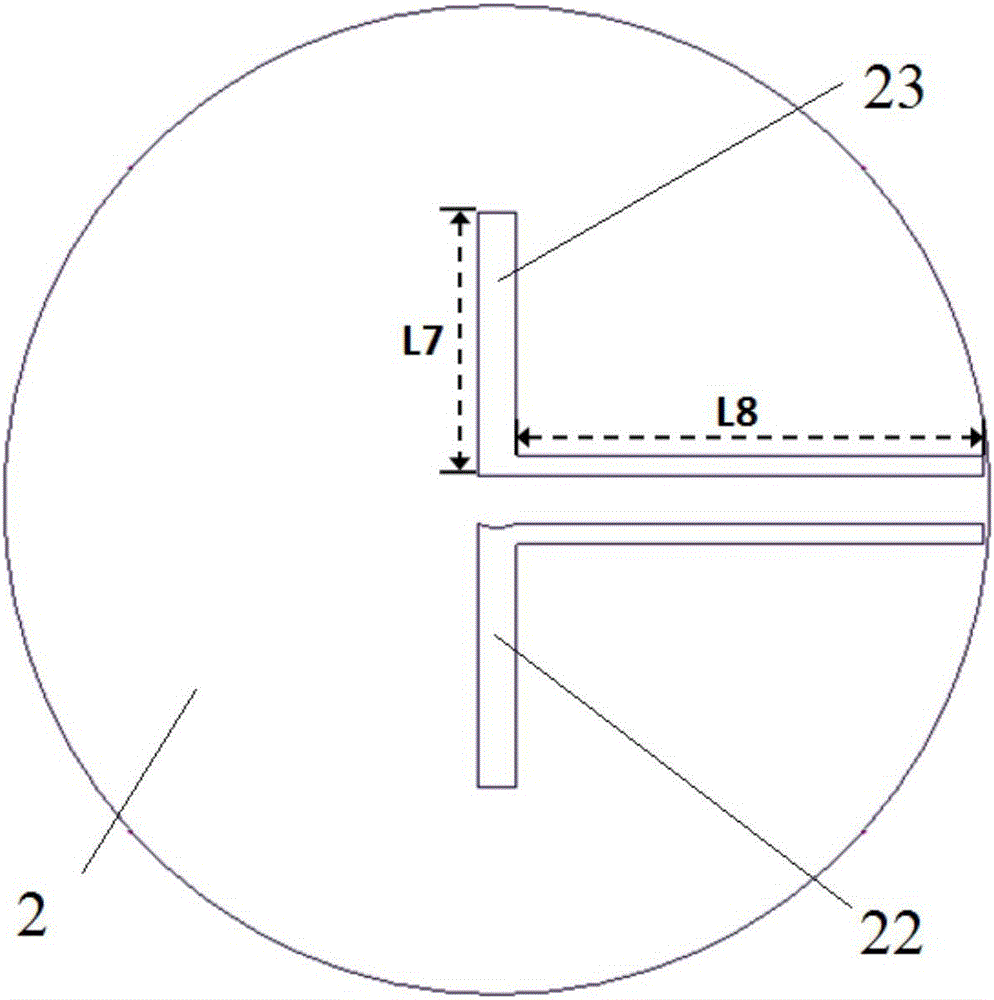

Small electrical planar huyghens source antenna

ActiveCN106252861AEasy to adjustReduce face to faceRadiating elements structural formsAntennas earthing switches associationCoaxial cableElectrical conductor

The invention discloses a small electrical planar huyghens source antenna. The small electrical planar huyghens source antenna comprises an upper-layer dielectric substrate, a lower-layer dielectric substrate, an electric dipole, a magnetic dipole, a first excitation strip, a second excitation strip and a coaxial cable, wherein the upper-layer dielectric substrate and the lower-layer dielectric substrate are laminated, the electric substrate is in contact with an upper surface of the upper-layer dielectric substrate, the magnetic dipole is in contact with a lower surface of the lower-layer dielectric substrate, the first excitation strip and the second excitation strip are arranged between the upper-layer dielectric substrate and the lower-layer dielectric substrate, the coaxial cable comprises an inner conductor and an outer conductor, the inner conductor passes through the lower-layer dielectric substrate to be connected with the first excitation strip, and the outer conductor passes through the lower-layer dielectric substrate to be connected with the second excitation strip. Through the abovementioned technical scheme, on one hand, the small electrical huyghens source antenna with a single feeding source is achieved by organically combining the electric dipole and the magnetic dipole by means of a near-field coupling resonant technology; and on the other hand, the huyghens source antenna directly adopts non-balance feeding, namely the single coaxial cable feeds, and other auxiliary feeding structures such as a Balun and a power divider are not needed.

Owner:CHONGQING UNIV +1

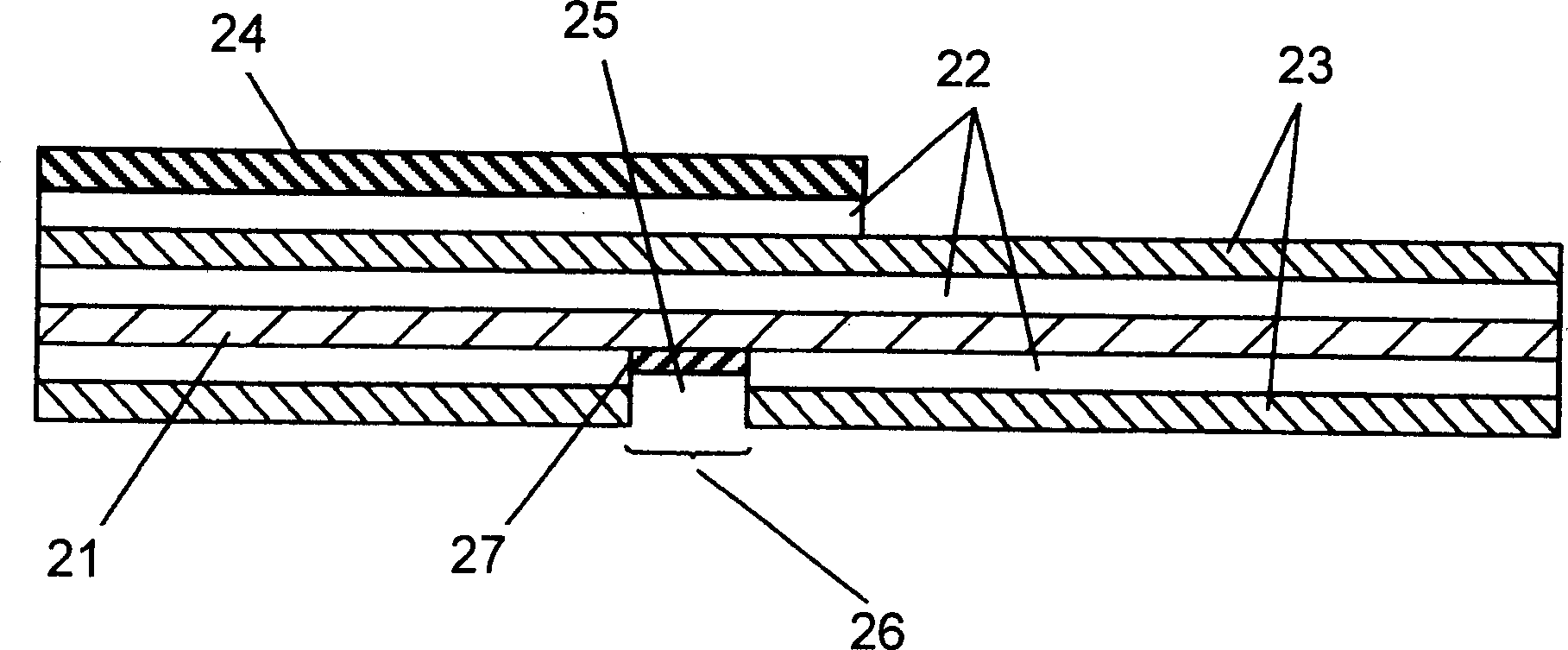

Electronic assembly wire and flat cable comprising same

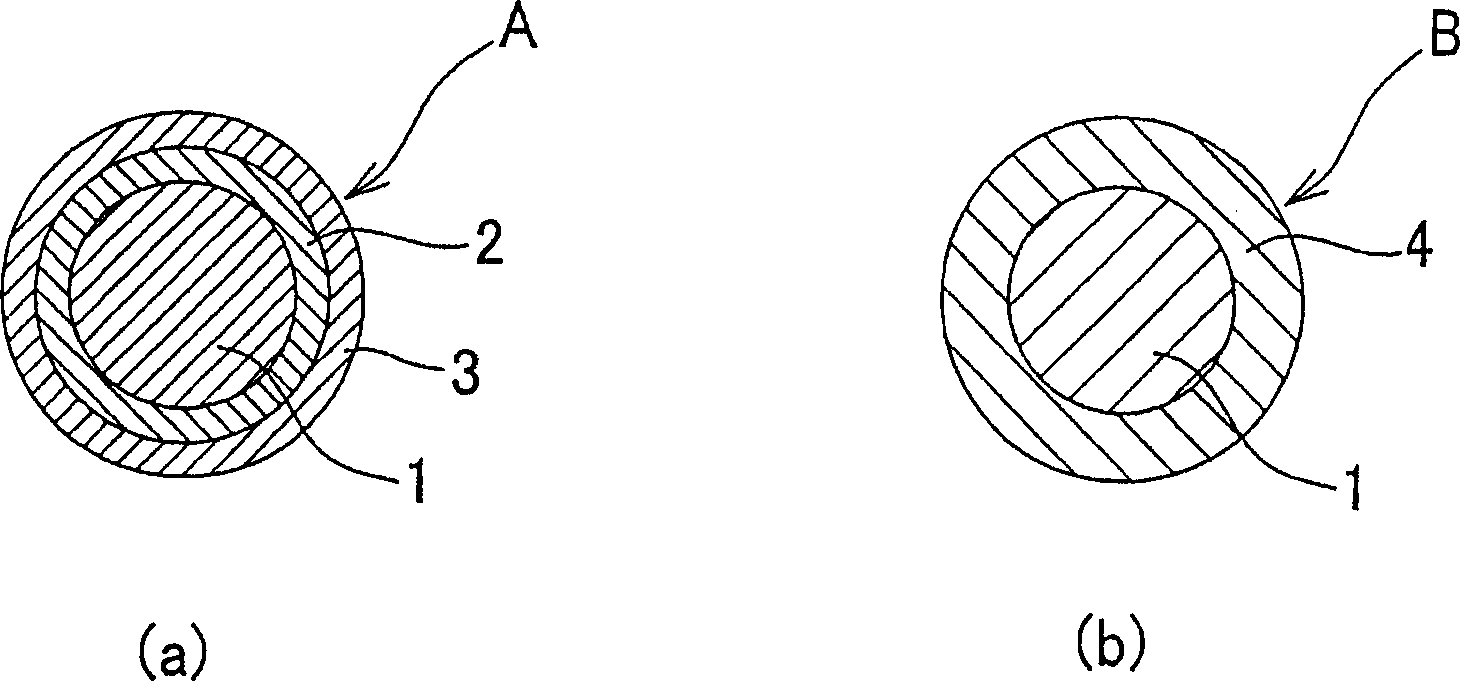

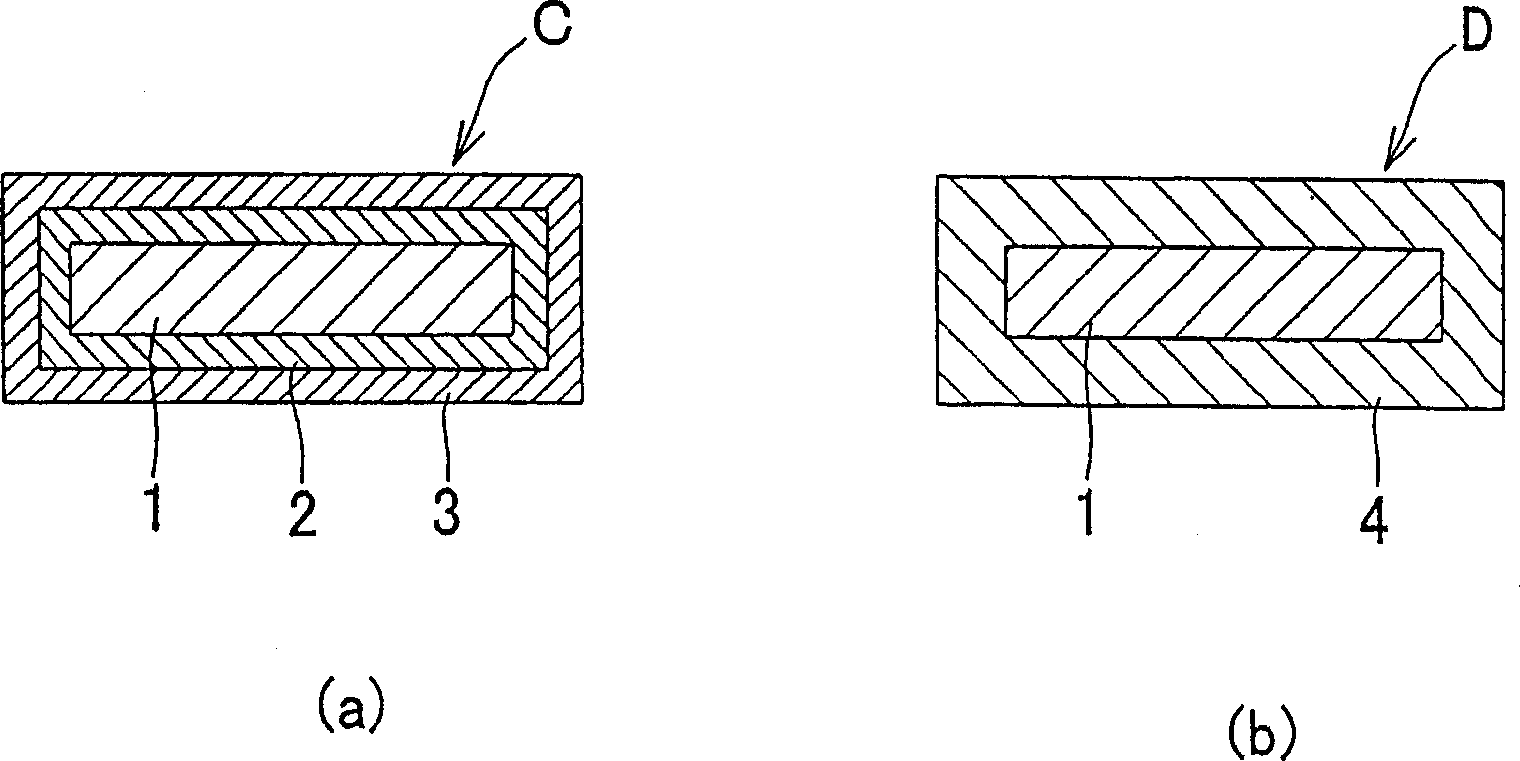

ActiveCN1848305AWhisker suppressionWhisker preventionSingle bars/rods/wires/strips conductorsSemiconductor/solid-state device detailsAlloy coatingElectronic component

The invention provides a wire for electronic components, comprising: a conductive substrate (1), a Sn alloy plating layer (2) of Sn and Bi, Cu, Ag or Sn and Zn covering its surface (front side), and forming a Zn alloy coating layer (2) on its upper layer. Plating layer, Ag plating layer, SnZn alloy plating layer, SnAg alloy plating layer, or upper layer plating layer of SnBi alloy plating layer (3). The concentration of Bi, Cu, Ag or Zn is set at 0.1 to 15% by weight, and the total thickness of the Sn alloy plating layer (2) and the upper layer plating layer (3) is set at 0.5 to 20 μm. Thereby, a lead wire for an electronic component having a tin-based plating layer, no toxic lead at all, low cost, and capable of reliably preventing whisker generation, and a flat cable composed of the lead wire are provided.

Owner:MISUZU CORP +1

Method for forming semiconductor-device replacement gate and method for manufacturing semiconductor device

ActiveCN103854980AGuaranteed electrical characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricGate stack

The invention provides a method for forming a semiconductor-device replacement gate and a method for manufacturing the semiconductor device. The method includes: providing a semiconductor substrate which includes an N-type area and a P-type area; forming a sacrifice-gate stack on each of the N-type area and the P-type area respectively, wherein each sacrifice-gate stack includes a sacrifice-gate dielectric and a sacrifice-gate electrode, the sacrifice-gate electrode is located on the sacrifice-gate dielectric and the sacrifice-gate electrode in the N-type area is higher than the gate electrode of the P-type area; forming a side wall around each sacrifice-gate stack; forming source-drain areas on the semiconductor substrate at the two sides of the sacrifice-gate stacks; removing the sacrifice-gate stack in the N-type area so as to form a first opening in the side wall; and forming an N-type replacement-gate stack in the first opening; removing the sacrifice-gate stack in the P-type area so as to form a second opening; forming a P-type replacement-gate stack in the second opening; and performing planarization until the N-type replacement-gate stack is exposed. The method is simple in process.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

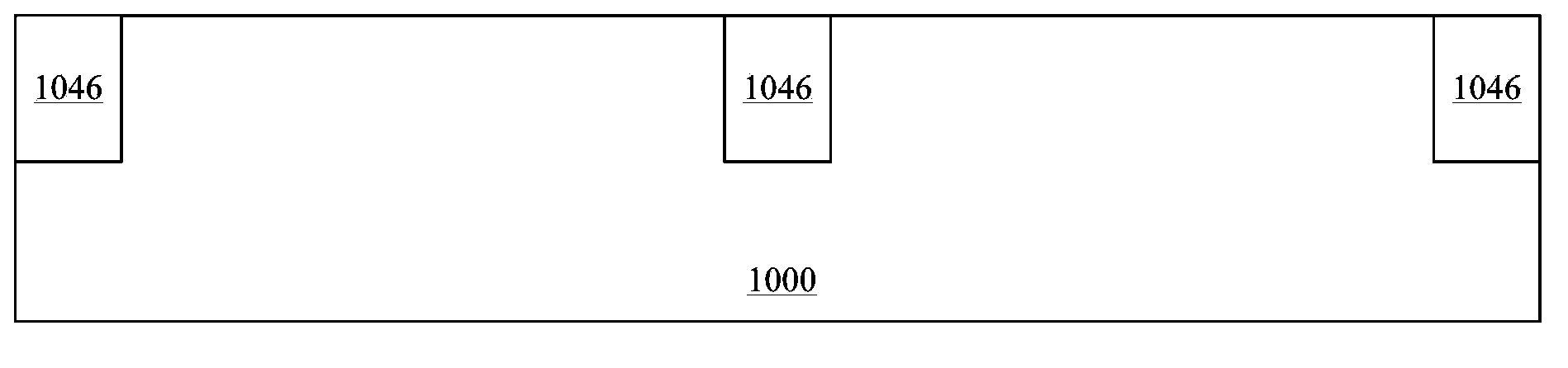

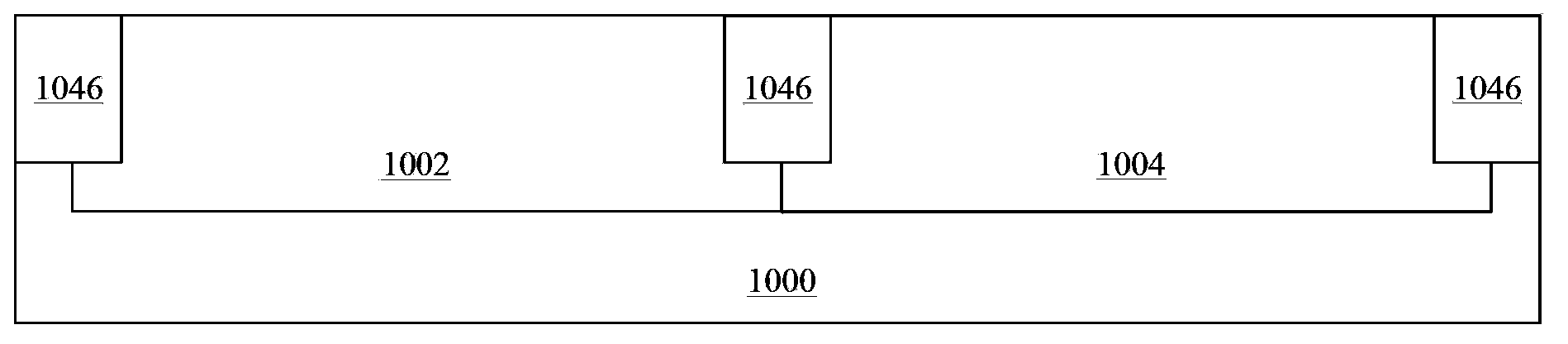

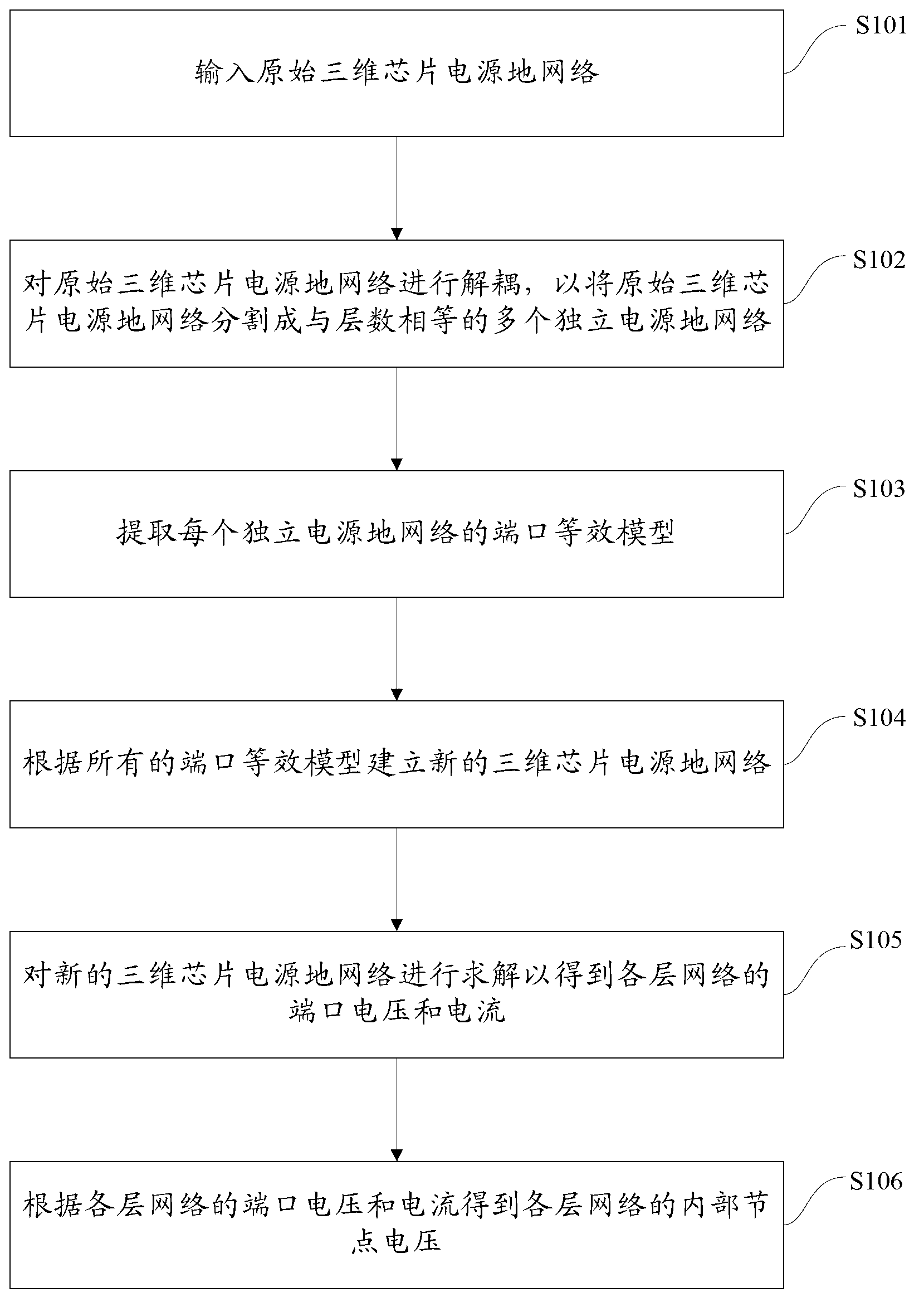

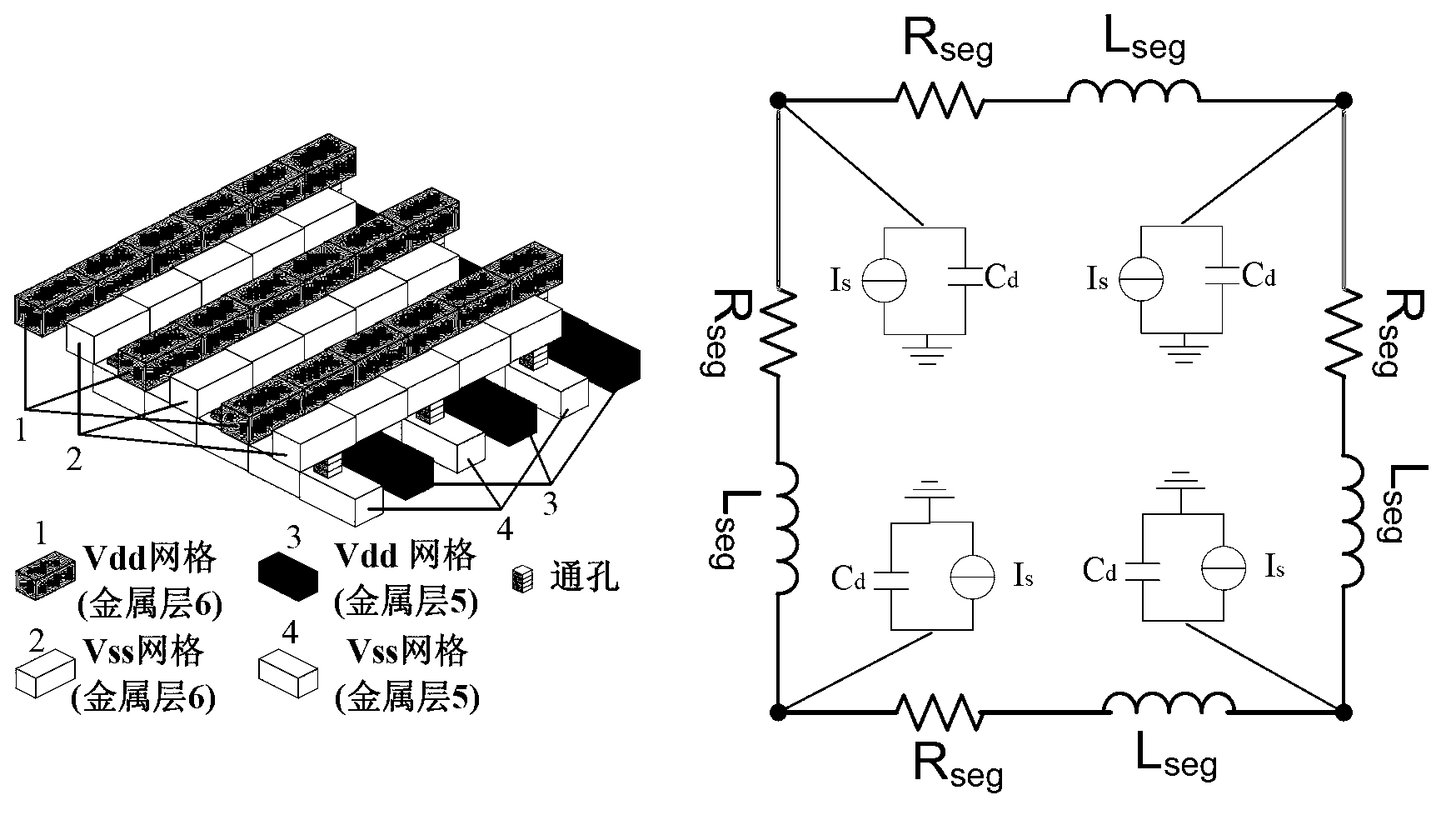

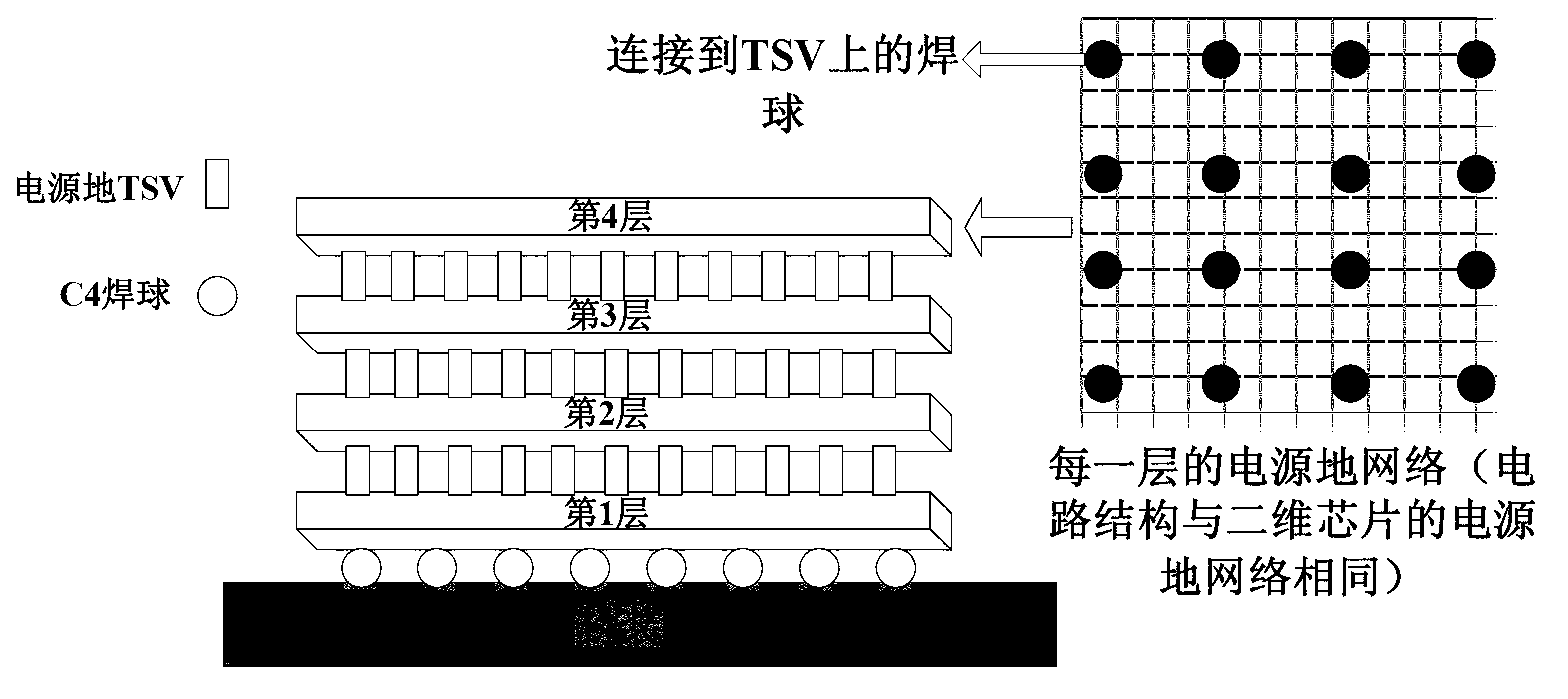

Hierarchical simulation method for three-dimensional chip power supply ground network

InactiveCN103310070AReduce complexityGuaranteed electrical characteristicsSpecial data processing applicationsEngineeringThree-dimensional integrated circuit

The invention provides a hierarchical simulation method for a three-dimensional chip power supply ground network. The method comprises the following steps: inputting an original three-dimensional chip power supply ground network; decoupling the original three-dimensional chip power supply ground network so as to divide the original three-dimensional chip power supply ground network into a plurality of independent power supply ground networks with the number as same as the layer number; extracting a port equivalent model of each independent power supply ground network; establishing a new three-dimensional chip power supply ground network according to all the port equivalent models; solving the new three-dimensional chip power supply ground network to obtain port voltage and current of each layer of network; obtaining the internal node voltage of each layer of network according to the port voltage and current of each layer of network. According to the method provided by the invention, simulating calculation can be performed on each layer in parallel, so that the calculating efficiency is improved and the simulating complexity is reduced.

Owner:TSINGHUA UNIV

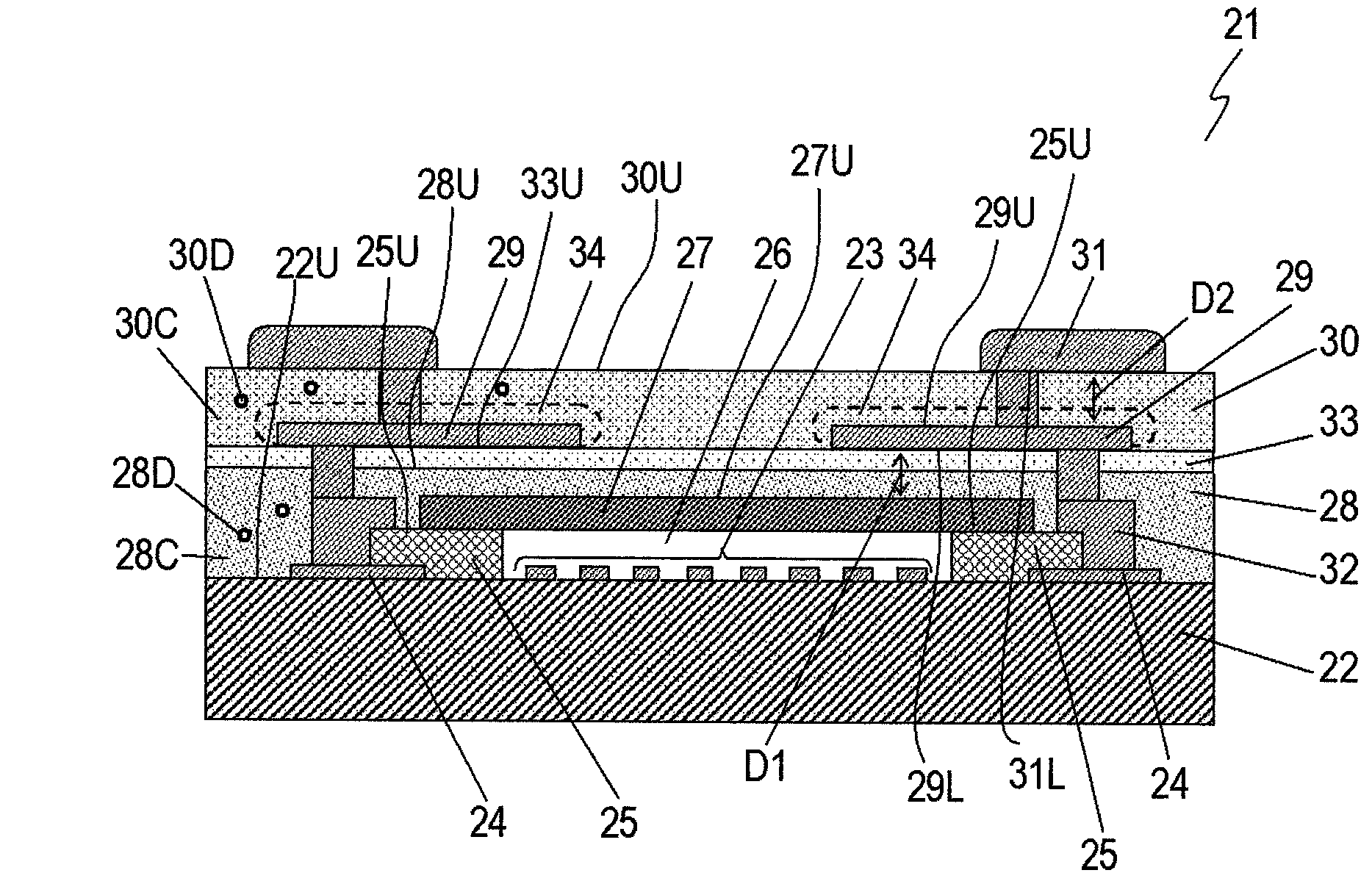

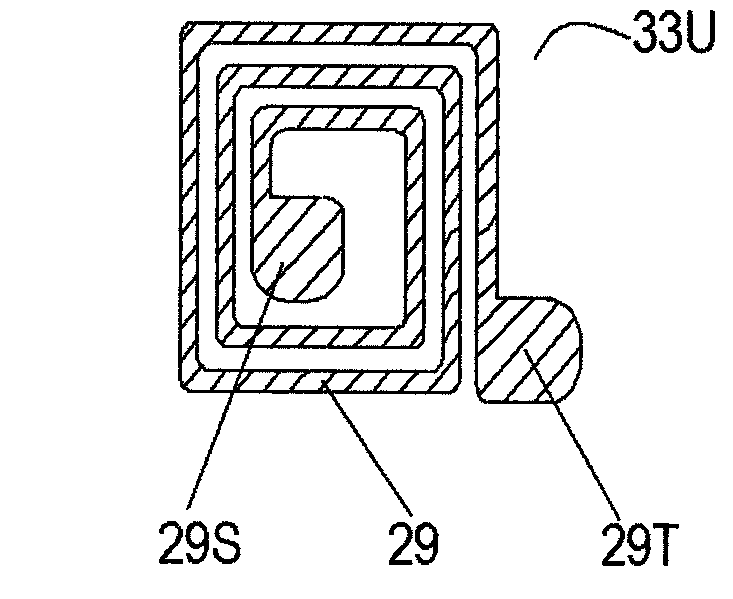

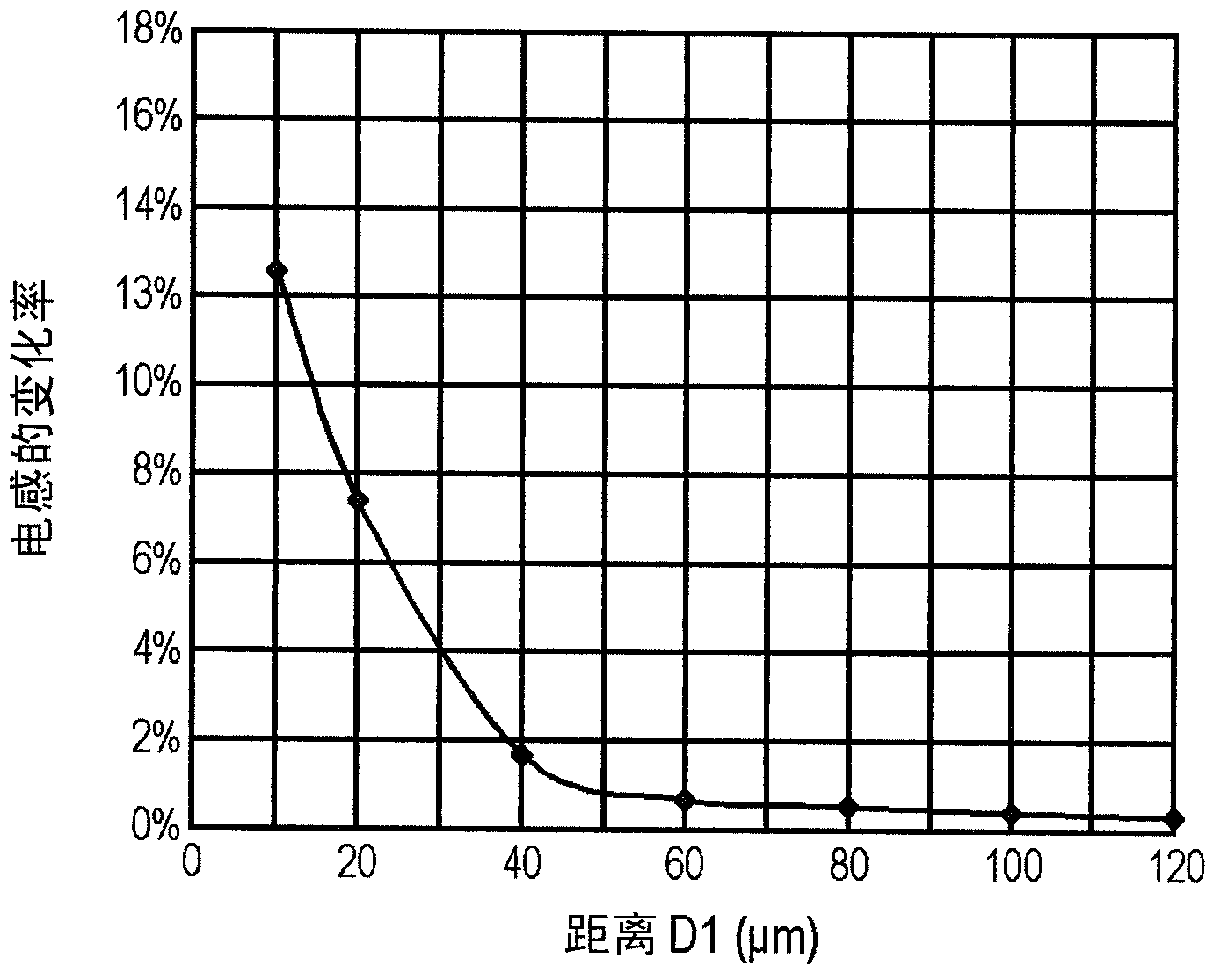

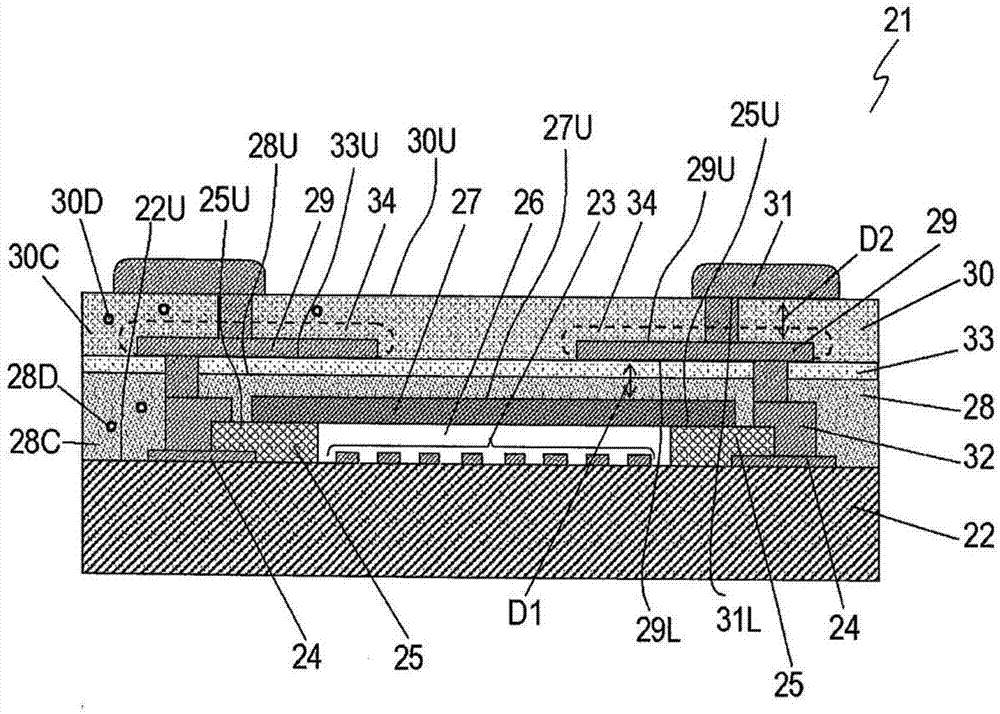

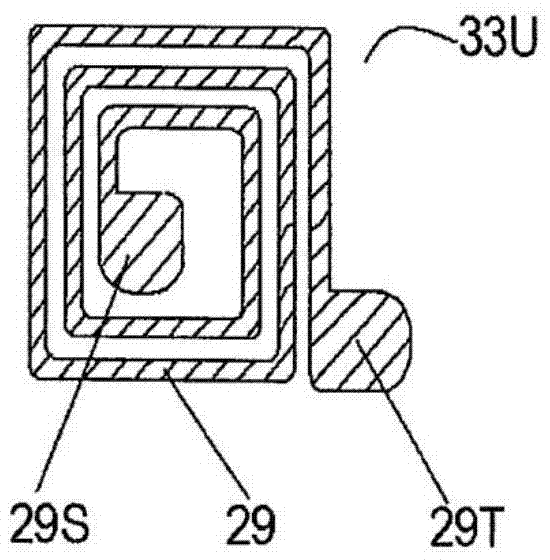

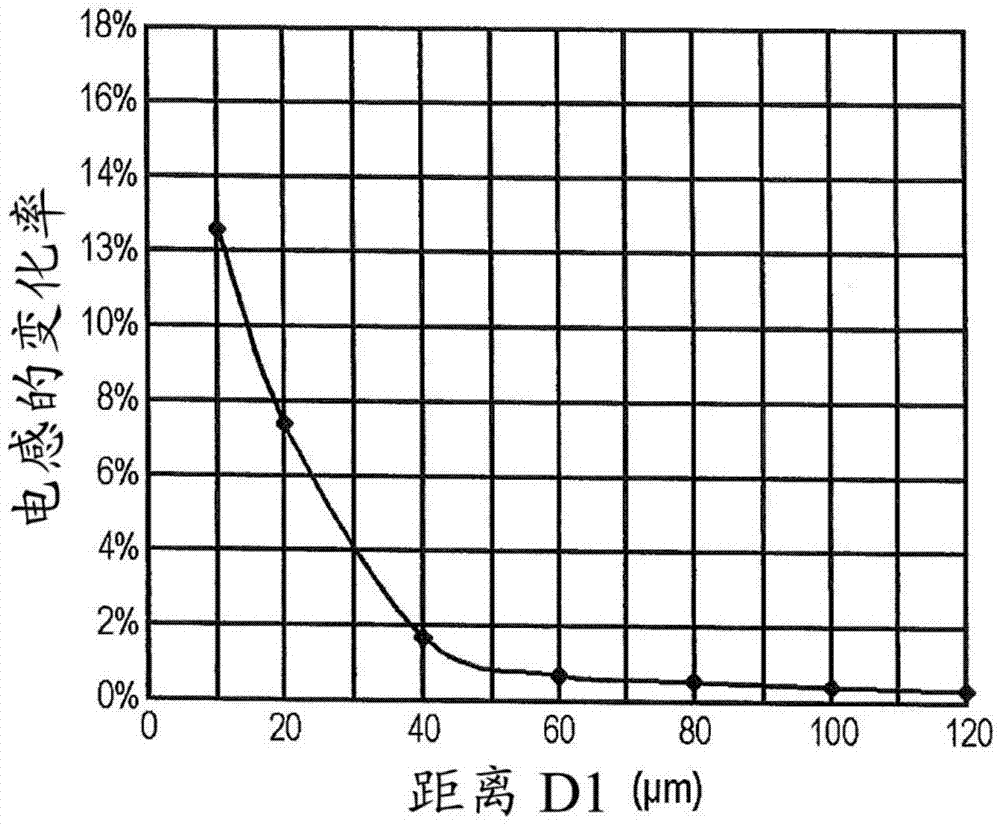

Elastic wave device

ActiveCN102763328AGuaranteed Electrical CharacteristicsReduce biasTransformersImpedence networksInductorElectric properties

An elastic wave device comprises a piezoelectric substrate, an IDT electrode which is arranged on the piezoelectric substrate, a wiring electrode which is arranged on the piezoelectric substrate and is connected to the IDT electrode, a first insulating body which is arranged on the piezoelectric substrate and can seal the IDT electrode and the wiring electrode, a resin layer which is arranged on the first insulating body, an inductor electrode which is arranged on the resin layer, a second insulating body which is arranged on the resin layer and covers the inductor electrode, a terminal electrode which is arranged on the second insulating body, and a connection electrode which penetrates through the first insulating body, the second insulating body and the resin layer and electrically connects the wiring electrode, the terminal electrode and the inductor electrode to one another. The first insulating body comprises a resin and a filler dispersed in the resin. The density of the filler in the resin layer is smaller than the average density of the filler in the first insulating body. The elastic wave device secures the electric properties of an inductor and can have reduced fluctuations in the electric properties.

Owner:SKYWORKS PANASONIC FILTER SOLUTIONS JAPAN

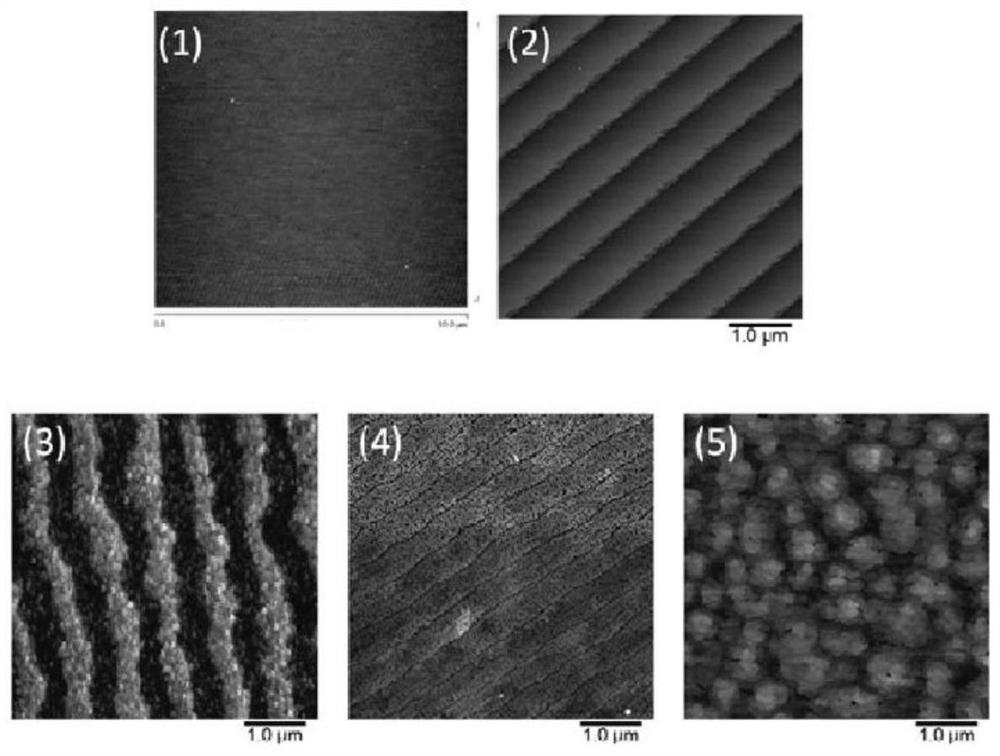

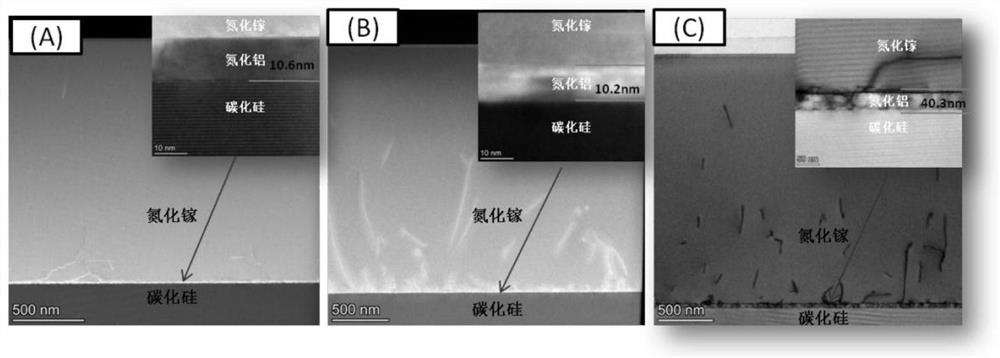

Preparation method of low-thermal-resistance gallium nitride high-electron-mobility transistor epitaxial material

ActiveCN112670161AGuaranteed quality characteristicsGuaranteed electrical characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesInterfacial thermal resistanceGallium nitride

The invention discloses a preparation method of a low-thermal-resistance gallium nitride high-electron-mobility transistor epitaxial material, and belongs to the technical field of semiconductor epitaxial materials. According to the invention, the method comprises the steps: employing high-temperature chemical vapor deposition equipment for carrying out high-temperature etching on the surface of a silicon carbide substrate, so the surface of the substrate presents controllable atomic-scale step morphology; carrying out the atomic-scale aluminum nitride nucleation on silicon carbide atomic steps by utilizing a metal organic chemical vapor deposition technology; transversely and rapidly combining the aluminum nitride nucleation points in an intermittent source supply mode, and performing layered deposition, so high-quality nanoscale aluminum nitride nucleation layer growth is achieved, and the gallium nitride high-electron-mobility transistor is prepared by taking aluminum nitride as a substrate. According to the method, the thickness of the aluminum nitride nucleating layer can be greatly reduced, the interface thermal resistance introduced by the aluminum nitride nucleating layer can be effectively reduced, the heat dissipation characteristic of the gallium nitride power device can be improved, and the method has extremely important significance for improving the power performance of the gallium nitride microwave power device.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

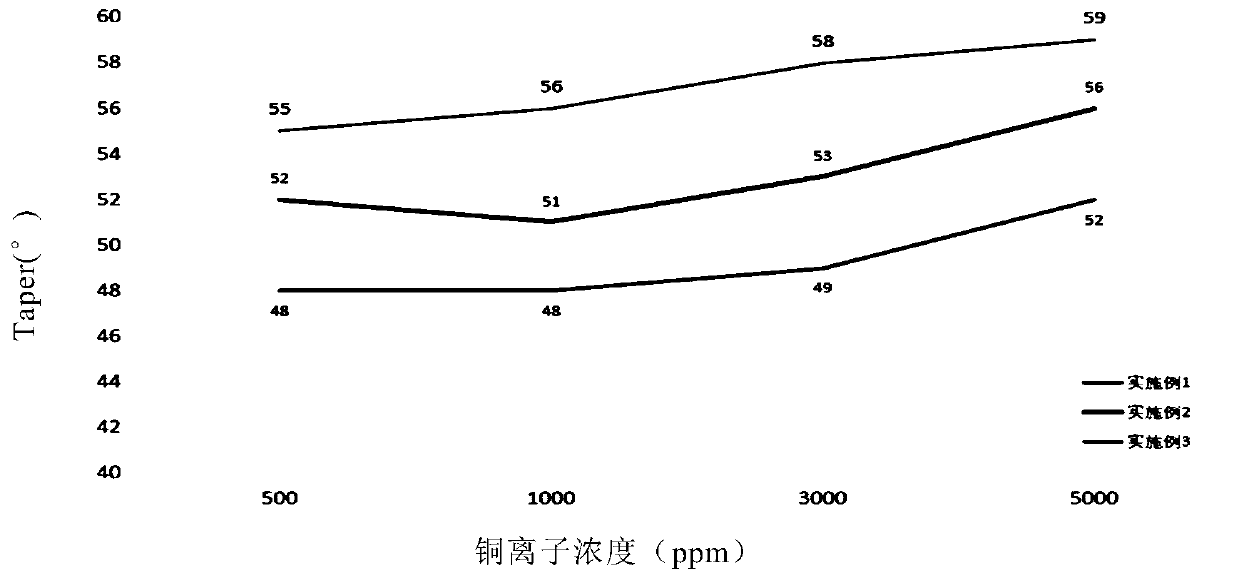

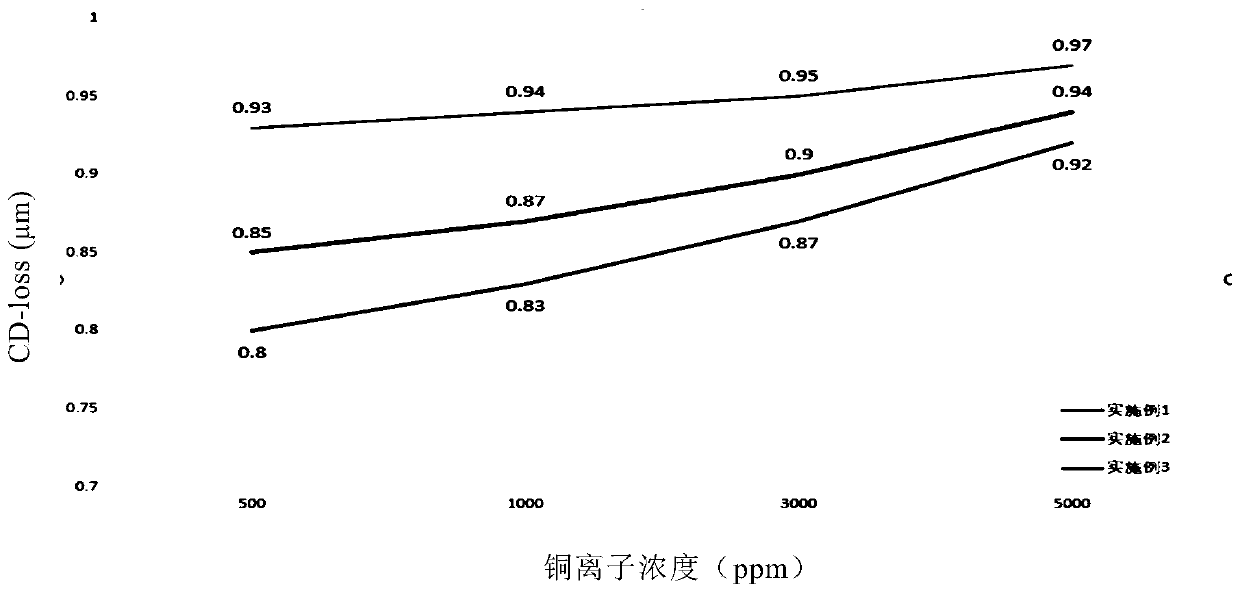

Etching solution and preparation method thereof

ActiveCN111334299ASimultaneous etchMaintain etch rateSurface treatment compositionsDevice materialPhysical chemistry

The invention provides an etching solution and a preparation method thereof. The etching solution comprises, by mass, 1-20% of hydrogen peroxide, 0.01-5% of an inorganic acid, 0.01-5% of a hydrogen peroxide stabilizer, 1-10% of a pH regulator, 1-10% of a complexing agent, 0.01-2% of a metal corrosion inhibitor, and the balance of water, wherein the inorganic acid at least comprises a fluorine compound. The etching solution can realize etching of source and drain metal electrodes and a metal oxide film layer at the same time, the use number of photomasks is reduced under the condition that theperformance of a semiconductor device is not influenced, the material cost is reduced, and the technological process is simplified.

Owner:CHENGDU ZHONGDIAN PANDA DISPLAY TECH CO LTD

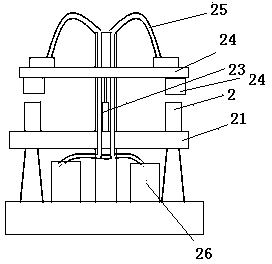

Overlying adhesive processing method for motor rotor iron core

ActiveCN104113169AGuaranteed accuracyGuaranteed Electrical CharacteristicsManufacturing stator/rotor bodiesAdhesiveSilicon

The invention relates to an overlying adhesive processing method for a motor rotor silicon steel sheet and belongs to the field of motor manufacturing. According to the method, an iron core which is not solidified is arranged on a special framework, a special heating device and a special pressurizing device are used, the iron core is solidified through repeatedly heating and pressurizing, a shot blasting device is used for performing shot blasting on the periphery of the iron core, a special tool is used for removing adhesive of the inner circumference of the iron core, the high accuracy of the iron core can be maintained by the aid of the iron core overlying adhesive processing method, and good function on guaranteeing electrical characteristics of a motor can be achieved.

Owner:ANYANG HENGAN MOTOR

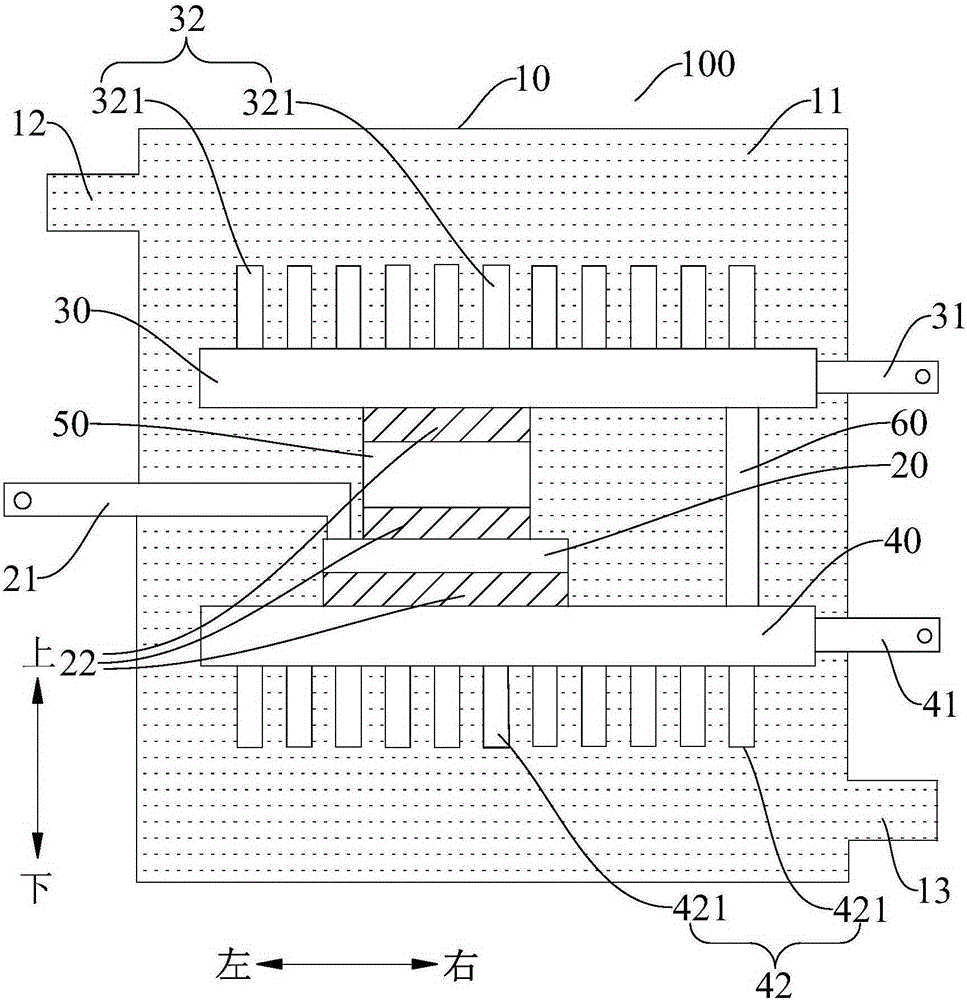

Power module and vehicle with same

InactiveCN106558560AImprove cooling effectImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesOptoelectronicsPower module

The invention discloses a power module and a vehicle with the same. The power module comprises a shell, a power chip, a first heat radiation substrate and a second heat radiation substrate. An accommodation cavity is defined in the shell and is filled with insulation material. The first heat radiation substrate and the second heat radiation substrate are oppositely arranged. The power chip, the first heat radiation substrate and the second heat radiation substrate are all positioned in the accommodation cavity and are covered by the insulation material. The first heat radiation substrate and the second heat radiation substrate are arranged on the upper surface and the lower surface of the power chip respectively. A collector electrode is led out of the second heat radiation substrate, an emitting electrode is led out of the first heat radiation substrate, and a gate electrode is led out of the power chip. According to the power module provided by the embodiment of the invention, the upper and lower surfaces of the power chip achieve heat radiation at the same time, so that the heat radiation performance of the power module is greatly enhanced, thereby improving the reliability of the power module, and by arranging the insulation material in the shell, the effect of electrical insulation is achieved, devices in the shell are prevented from interference, and independent electrical features of each device are ensured.

Owner:BYD SEMICON CO LTD

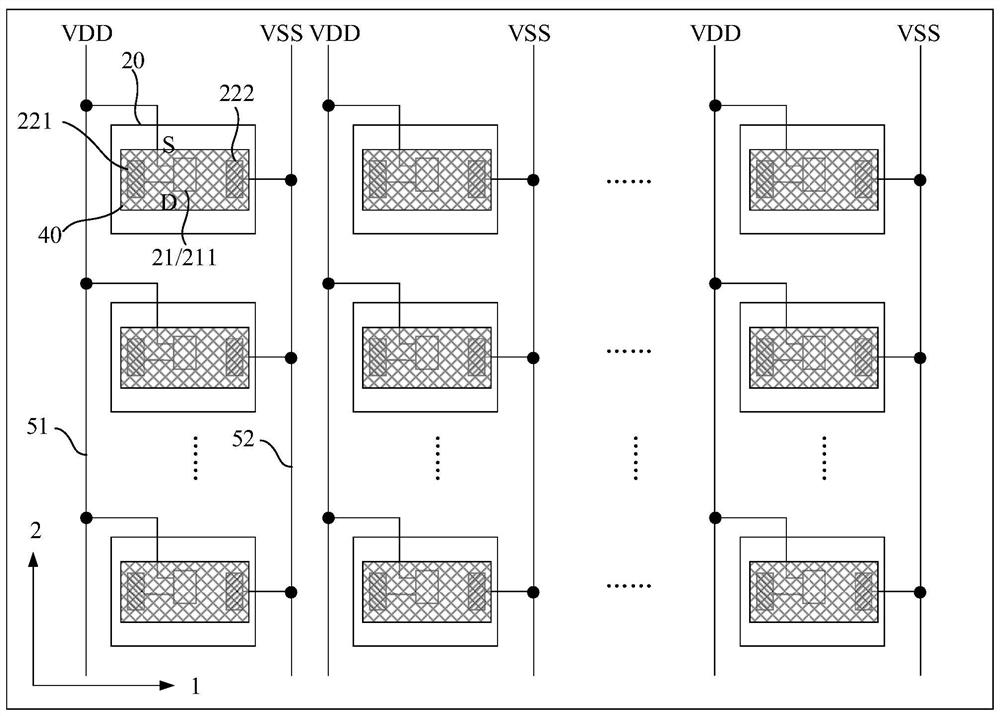

Array substrate, backlight module, display panel, display device and preparation method

ActiveCN111913323ASolve the complex preparation processSimple manufacturing processStatic indicating devicesSemiconductor lamp usageDisplay deviceThin membrane

The embodiment of the invention discloses an array substrate, a backlight module, a display panel, a display device and a preparation method. The array substrate comprises a plurality of driving units. Each driving unit comprises a first electrode, a second electrode and at least one thin film transistor; the first electrode and the second electrode are used for being connected with the anode andthe cathode of a light emitting diode respectively, so that the vertical projection of the light emitting diode on the array substrate can be overlapped with the at least one thin film transistor, andthe thin film transistor is located at the backlight side of the light emitting diode in the light emitting direction of the light emitting diode. The driving unit controls the light-emitting diode to be turned on or off according to the driving signal. According to the embodiment of the invention, the problem that an existing array substrate needs to be additionally provided with a shading layer, so that the preparation process is complex, is solved; the influence of external illumination on the thin film transistor can be avoided, masks and preparation procedures required for preparing theshading layer are saved, the preparation process of the array substrate is simplified, and the manufacturing cost is reduced.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD

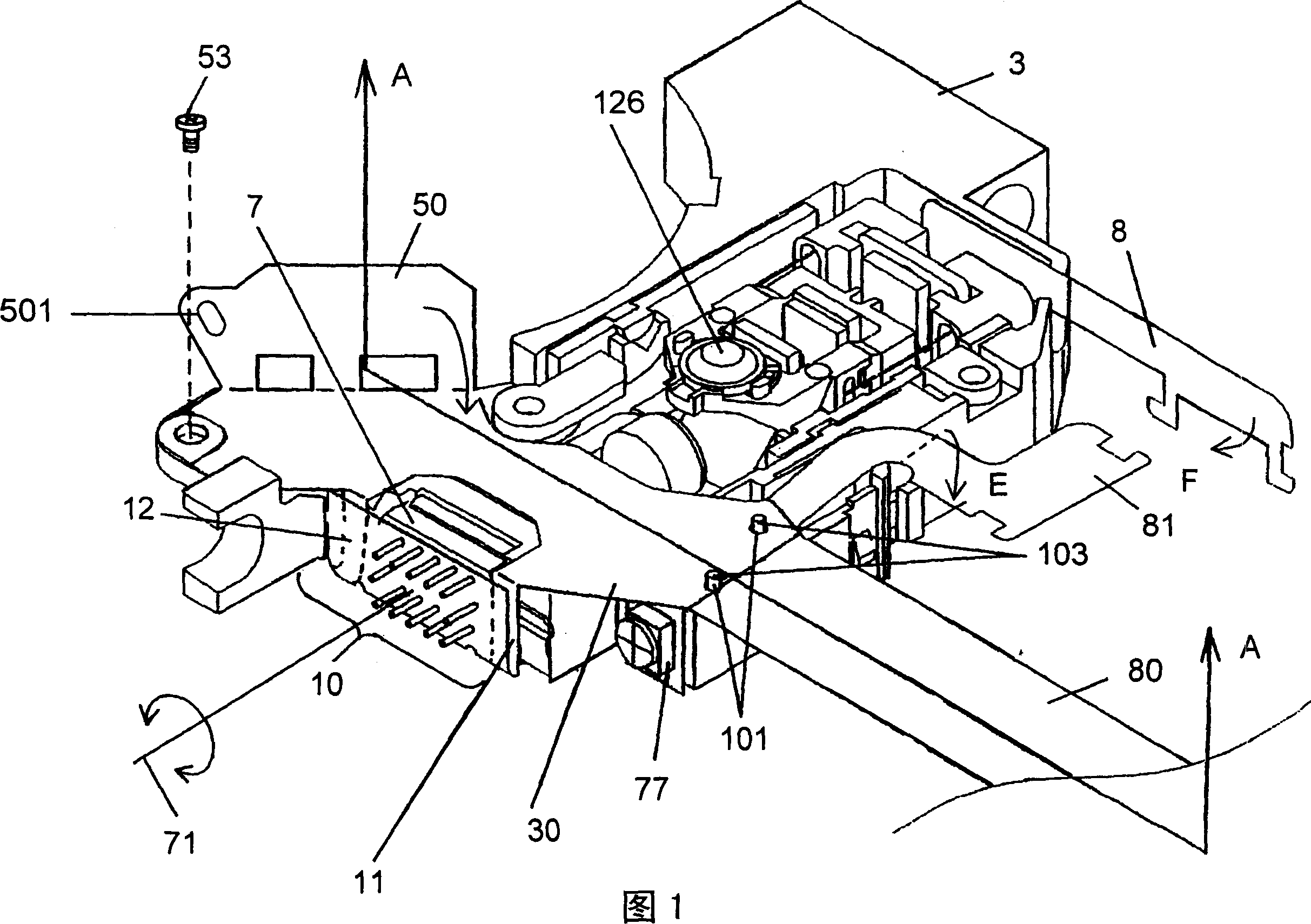

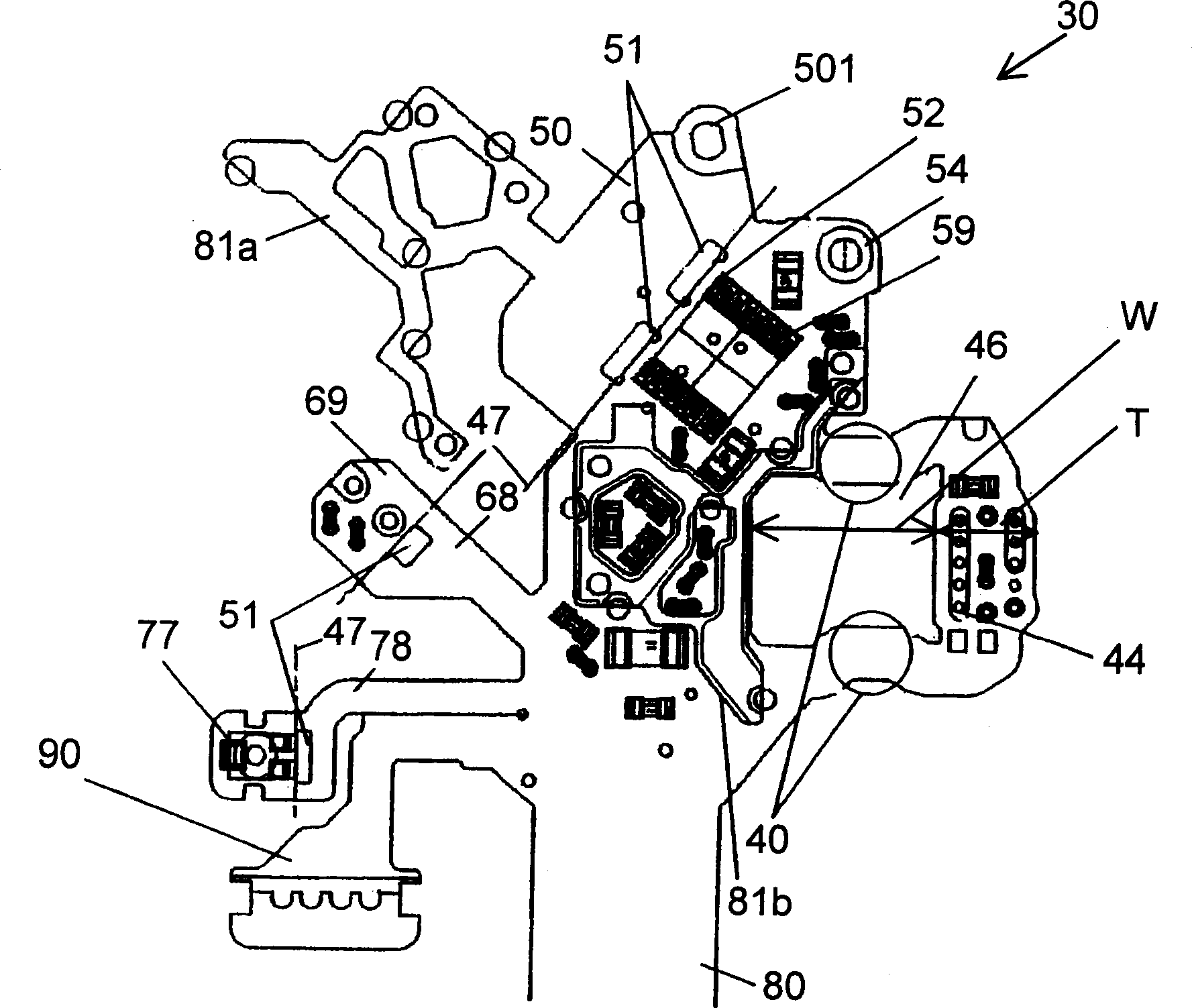

Pickup device and optical disk device using the same

InactiveCN1428772AReduce usageGuaranteed Electrical CharacteristicsTrack finding/aligningDisposition/mounting of recording headsEngineeringElectrical and Electronics engineering

A pickup device employing an inexpensive flexible printed circuit sheet (FPC) which demonstrates preferable electrical characteristics. FPC has a signal conductive layer inside, and a U-shape bending portion is formed in a midway of FPC at a position where a hologram unit is connected. An opening is formed on FPC adjacent to an area when the hologram unit is connected, and the length of this opening is longer than the height of the hologram unit.

Owner:PANASONIC CORP

Elastic wave device

ActiveCN104767499AGuaranteed Electrical CharacteristicsReduce biasTransformersImpedence networksEngineeringInductor

An elastic wave device includes a piezoelectric substrate, an IDT electrode disposed on the piezoelectric substrate, a wiring electrode disposed on the piezoelectric substrate and connected to the IDT electrode, a first insulator disposed on the piezoelectric substrate to seal the IDT electrode and the wiring electrode, a resin layer provided on the first insulator, an inductor electrode disposed on the resin layer, a second insulator disposed on the resin layer to cover the inductor electrode, a terminal electrode disposed on the second insulator, and a connecting electrode passing through the first insulator, the second insulator, and the resin layer to electrically connect the wiring electrode, the terminal electrode, and the inductor electrode. The first insulator includes a resin and filler dispersed in the resin. A density of filler in the resin layer is smaller than an average density of the filler in the first insulator. This elastic wave device has excellent characteristics of the inductor while reducing variations of the characteristics.

Owner:SKYWORKS PANASONIC FILTER SOLUTIONS JAPAN

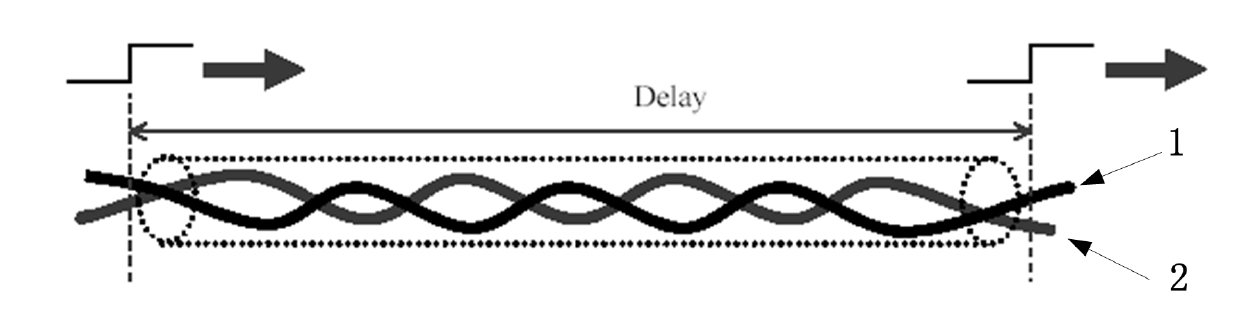

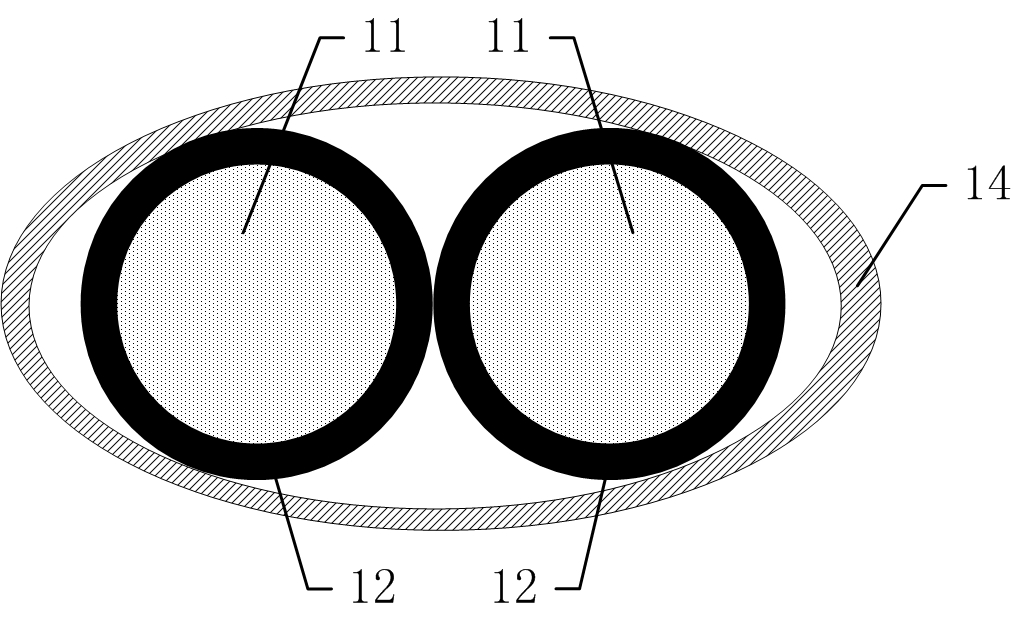

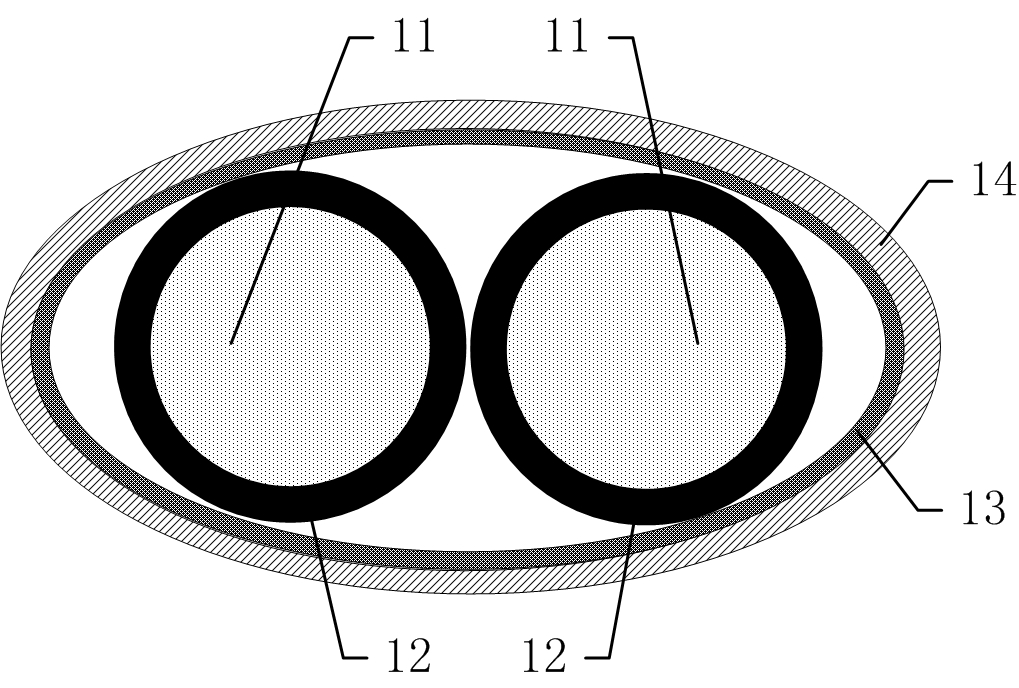

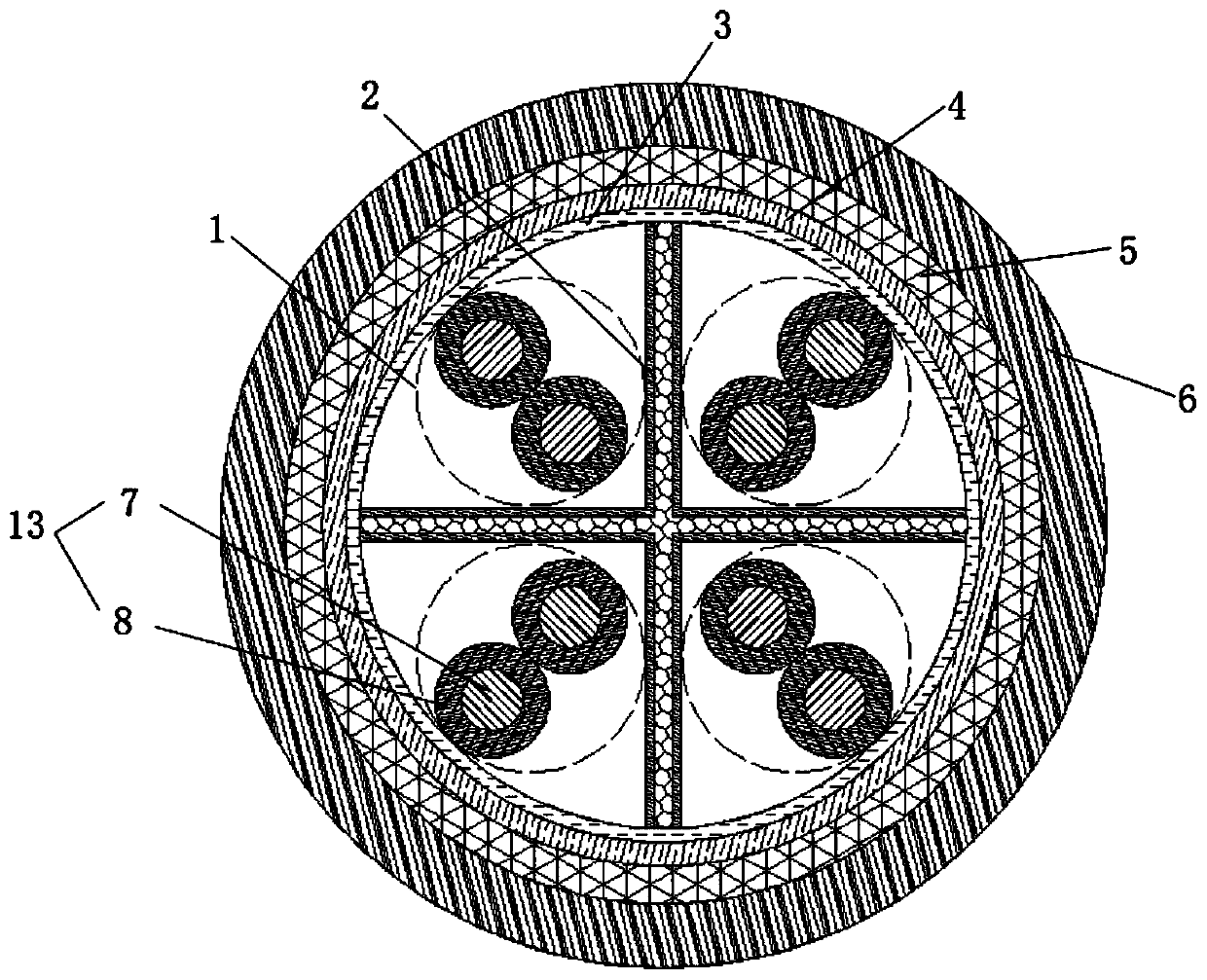

Side-by-side cable

InactiveCN102610302AGuaranteed Electrical CharacteristicsReduce processing efficiencyInsulated cablesInsulated conductorsPolyesterElectrical conductor

The invention provides a side-by-side cable which comprises at least two conductors and insulating layers respectively coating each conductor, wherein the conductors and the insulating layers form a wire; two wires are arranged side by side and then are coated by one coating layer; and the coating layer is coated on the outer layers of the two wires which are arranged side by side by adopting a polyester tape; and the insulating layers are dielectric media by which the cables are insulated; each conductor is further coated by the insulating layer through an Teflon wire; the coating layer further comprises a copper foil which is coated on the outer layer of the wire; and the polyester tape is coated on the outer layer of the copper foil. Compared with general twisted pair cables, the side-by-side cable disclosed by the invention is more stable in performance and smaller in impedance difference and delay difference.

Owner:大同电线电缆科技(吴江)有限公司

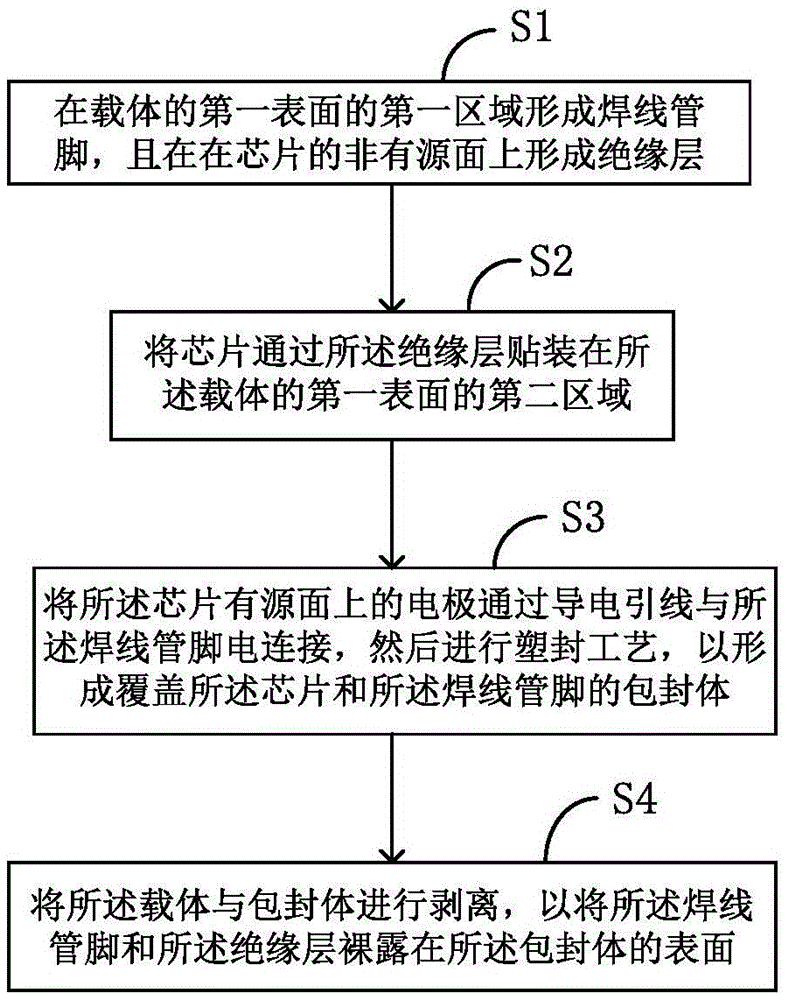

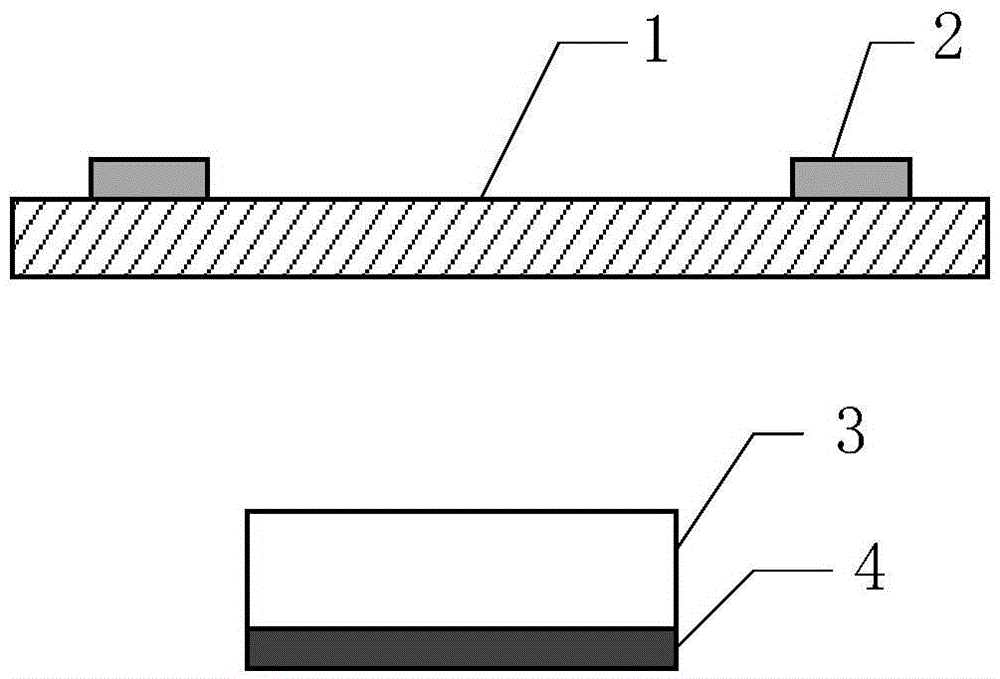

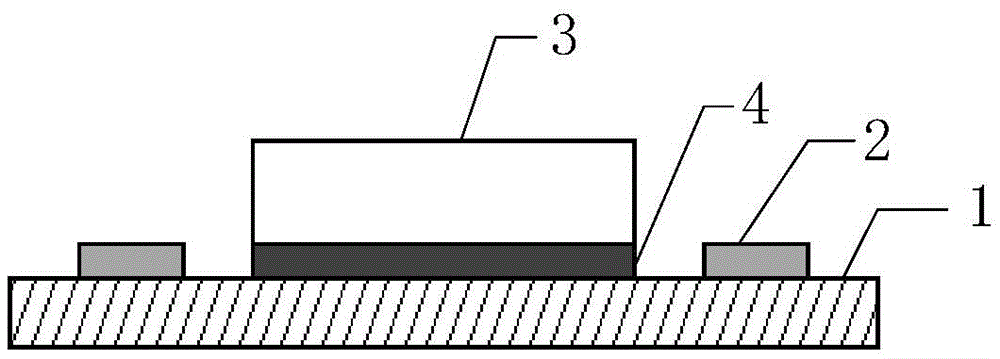

Chip packaging method and chip packaging structure

ActiveCN105489542AGuaranteed Electrical CharacteristicsGuaranteed insulation performanceSemiconductor/solid-state device detailsSolid-state devicesElectrical and Electronics engineeringEngineering

The invention provides a chip packaging method and a chip packaging structure. The chip packaging method comprises the steps of forming a bonding wire pin on a first region of a carrier surface; forming an insulating layer on a non-active surface of a chip; adhering the chip to a second region of the carrier surface through the insulating layer; and after lead bonding and packaging process are completed, peeling off the carrier from a plastic packaging body to enable the insulating layer and the bonding wire pin to be exposed on the surface of the plastic packaging body. When the packaging structure formed by the packaging method is mounted on a PCB, the insulation between the non-active surface of the chip and the PCB can be ensured, and the electrical characteristic of the packaging structure is ensured as well; and in addition, according to the packaging method, a pre-fabricated lead frame is not required, instead, the bonding wire pin is formed in the packaging process, so that the flexibility of the packaging design can be improved.

Owner:SILERGY SEMICON TECH (HANGZHOU) CO LTD

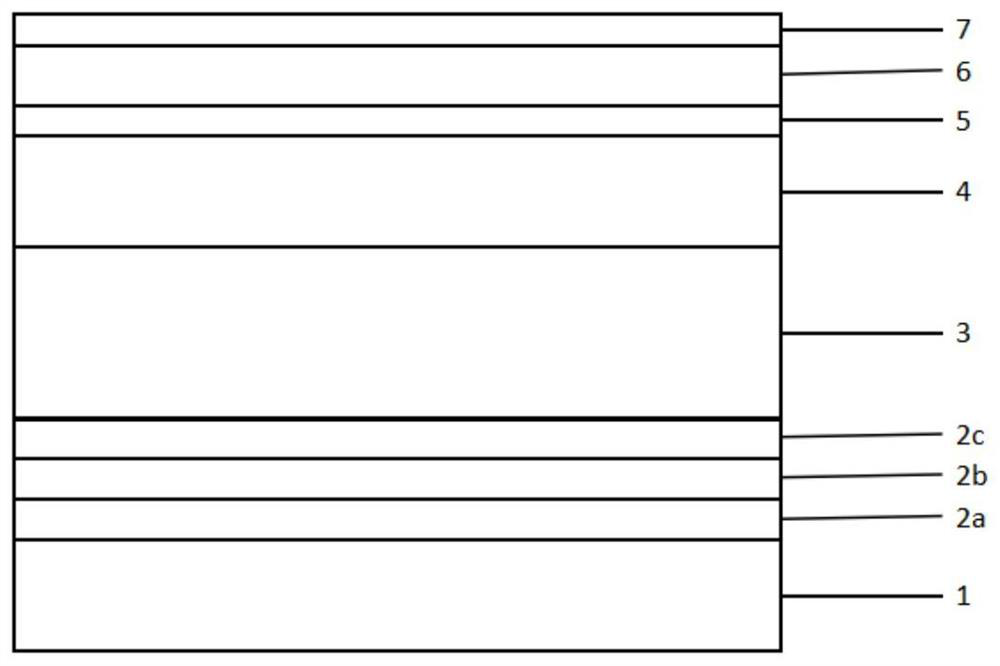

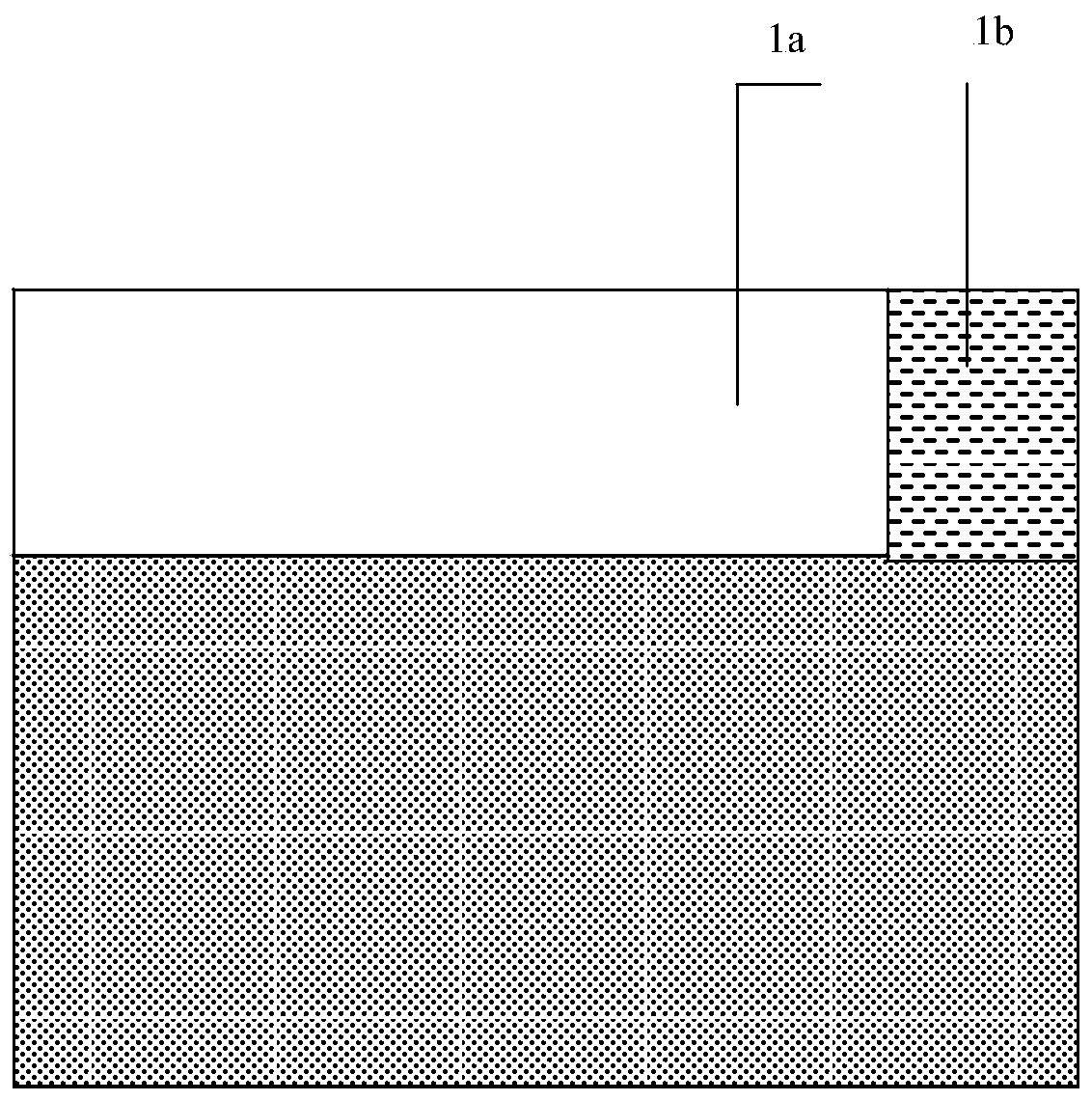

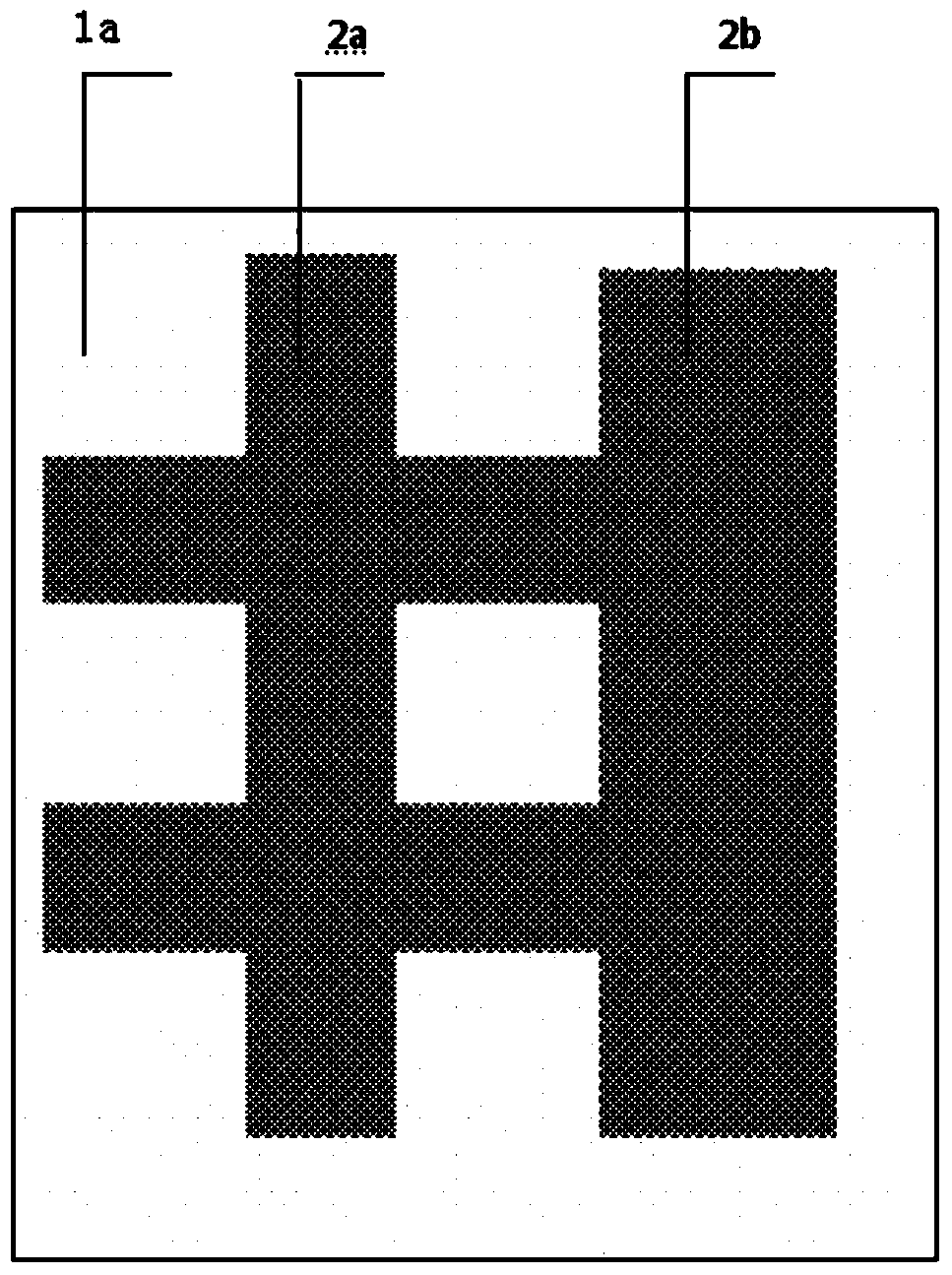

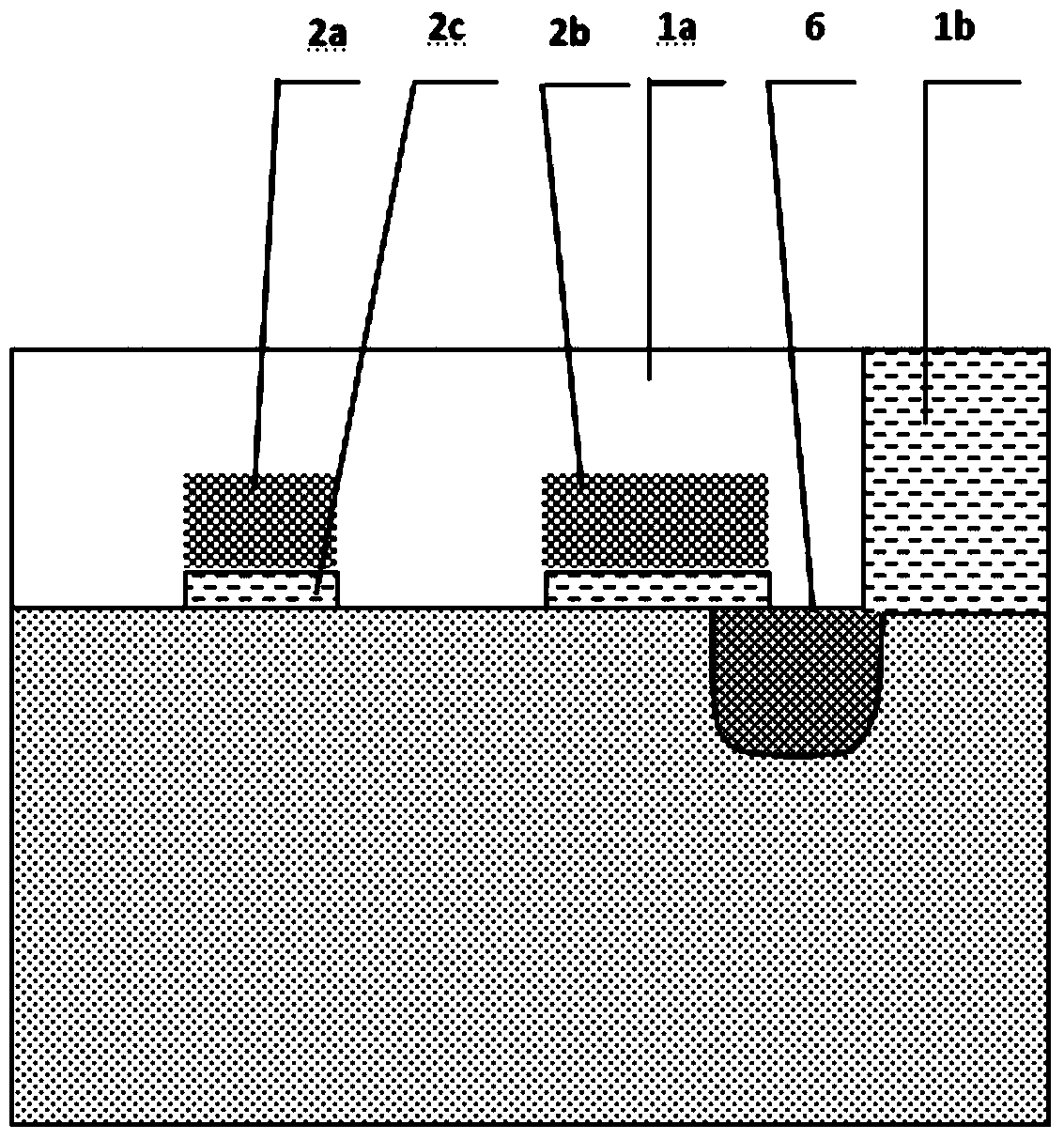

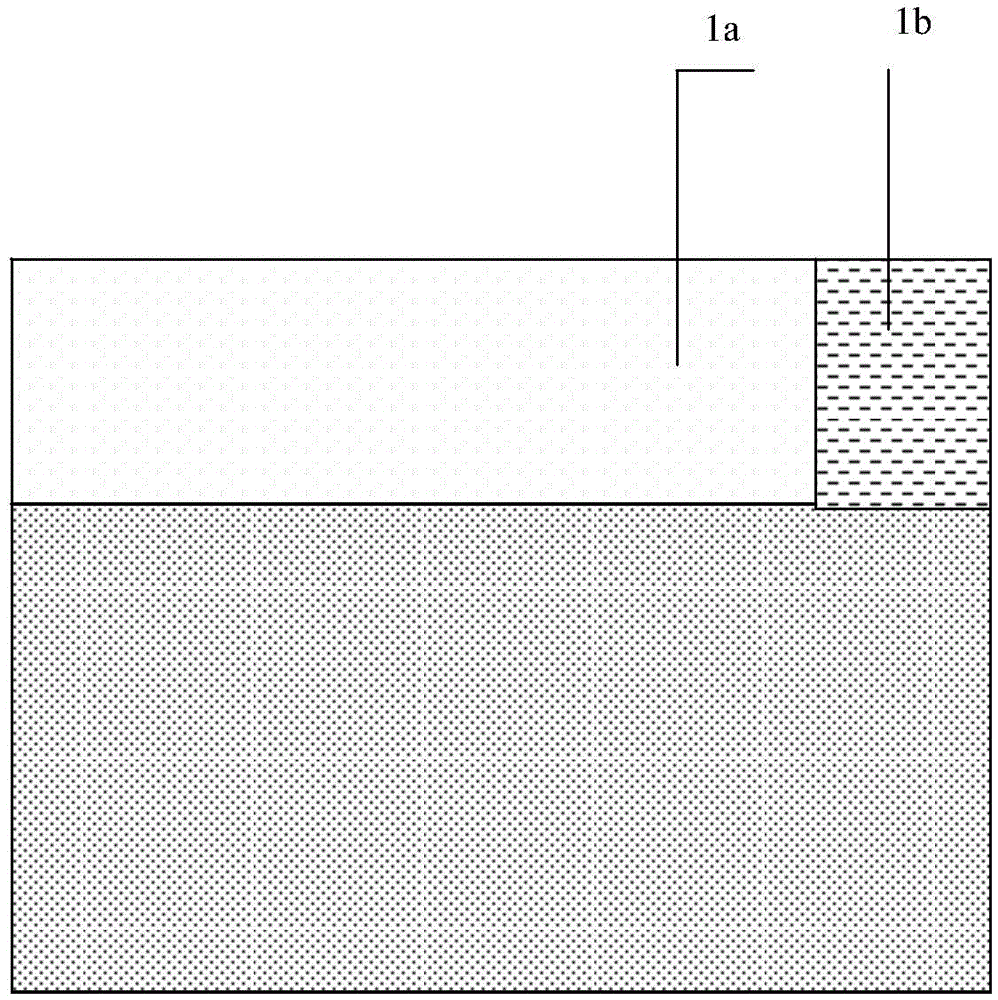

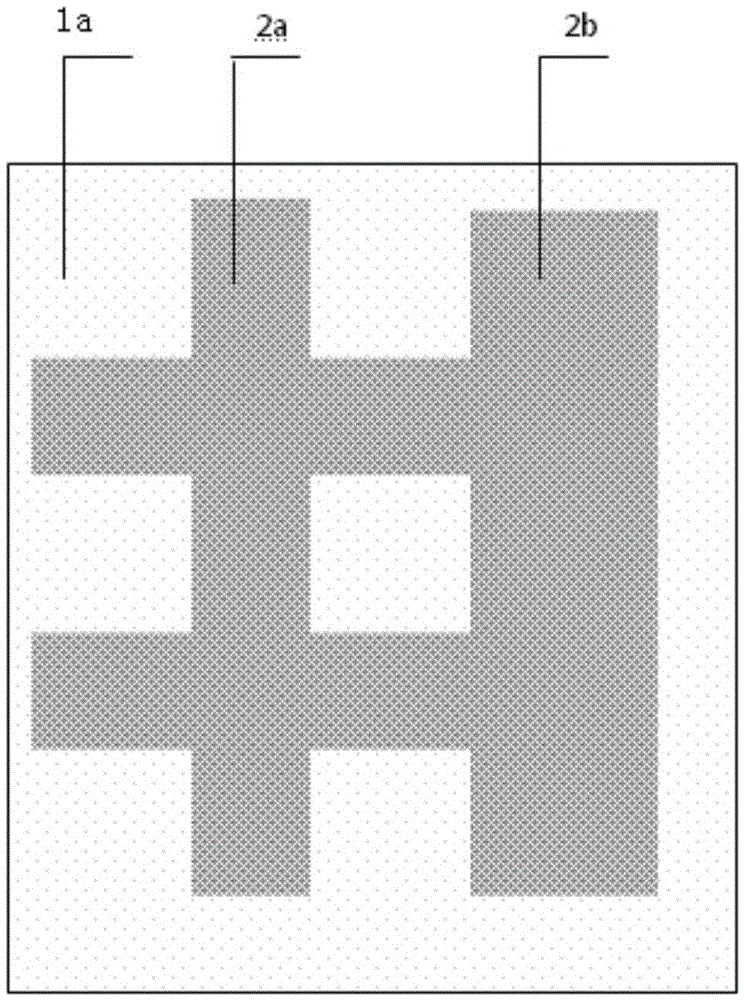

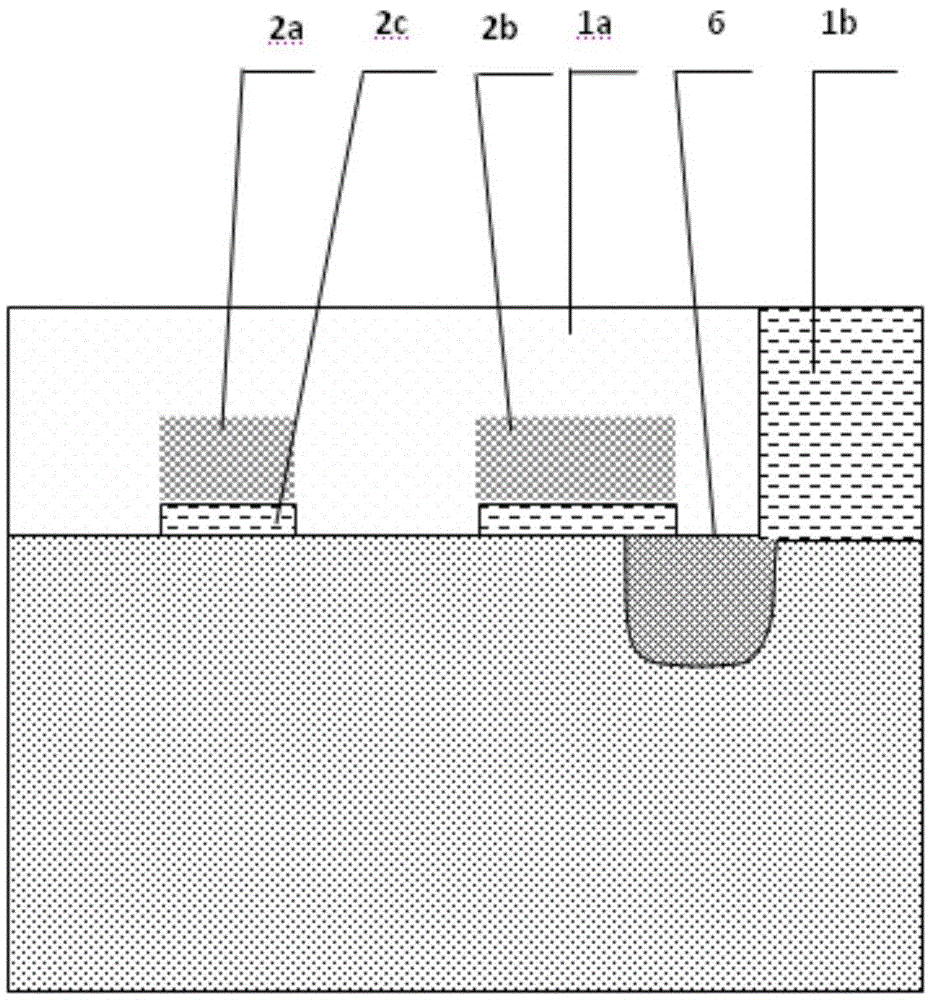

Method for saving area of medium- and low-voltage VDMOSFET chip

ActiveCN103745930AReduce chip areaIncrease the number of chips producedSolid-state devicesSemiconductor/solid-state device manufacturingCorrosionPolycrystalline silicon

The invention discloses a method for saving the area of a medium- and low-voltage VDMOSFET chip. Electrical properties of a VDMOS device can be guaranteed, and manufacturing cost is minimized. The method comprises the following steps: firstly, an active region (1a) and a non-corrosive region (1b) are formed on polycrystalline silicon through corrosion; a polycrystalline silicon region (2) is formed on the active region (1a) through deposition, and the polycrystalline silicon region (2) contains a polycrystalline silicon lead region (2a) and a polycrystalline silicon terminal structural region (2b); N+source regions (3) are formed below the polycrystalline silicon lead region (2a) and below the space between the polycrystalline silicon lead region (2a) and the polycrystalline silicon terminal structural region (2b) through diffusion; contact holes (4) are formed on the polycrystalline silicon region; a metal electrode (5) is formed on the active region (1a); the metal electrode (5) extends to cover all the contact holes (4); the contact holes (4) are connected to the N+source regions (3) through the metal electrode (5); and the metal electrode (5) and part of the polycrystalline silicon terminal structural region (2b) are overlapped.

Owner:BEIJING MXTRONICS CORP +1

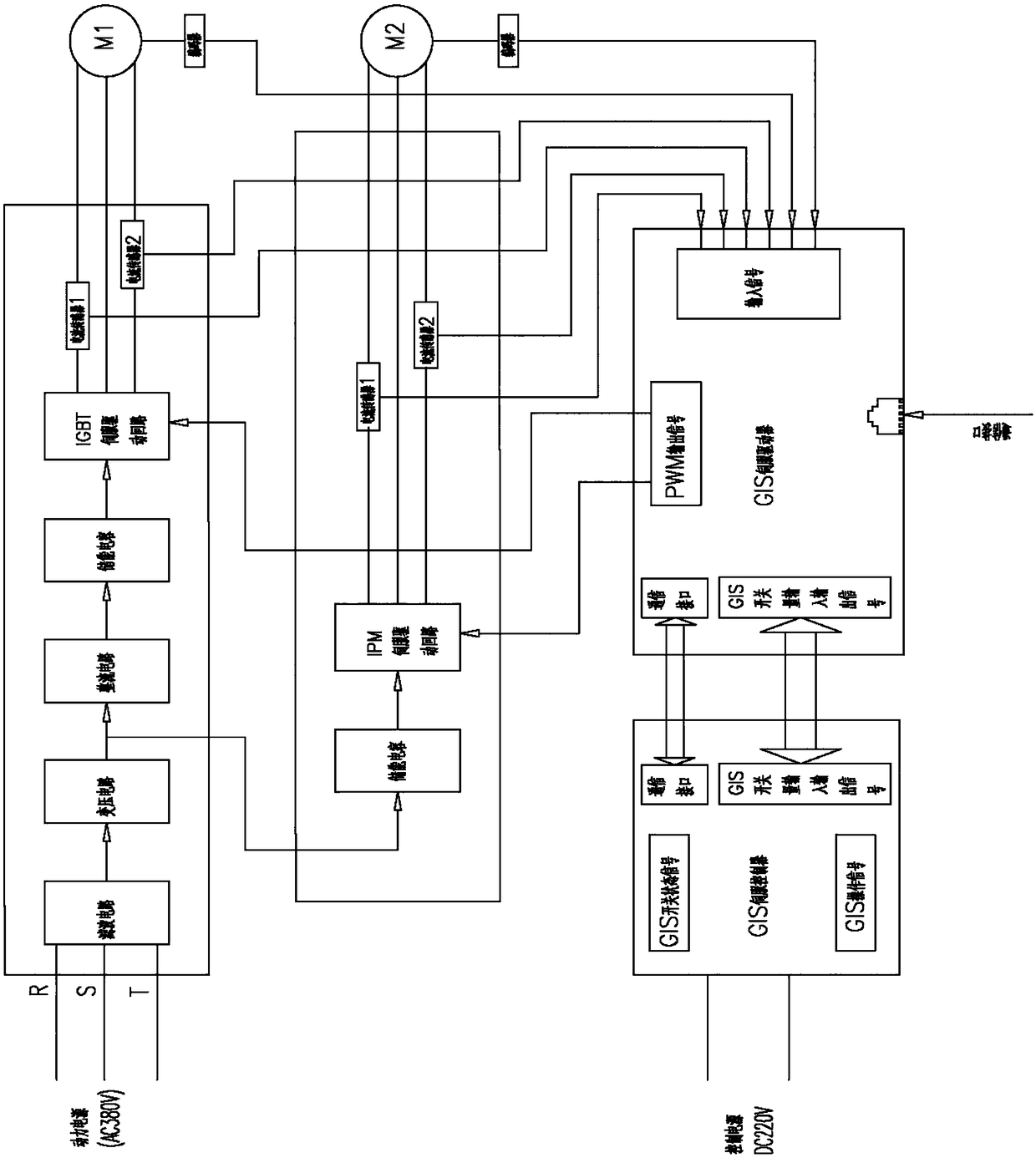

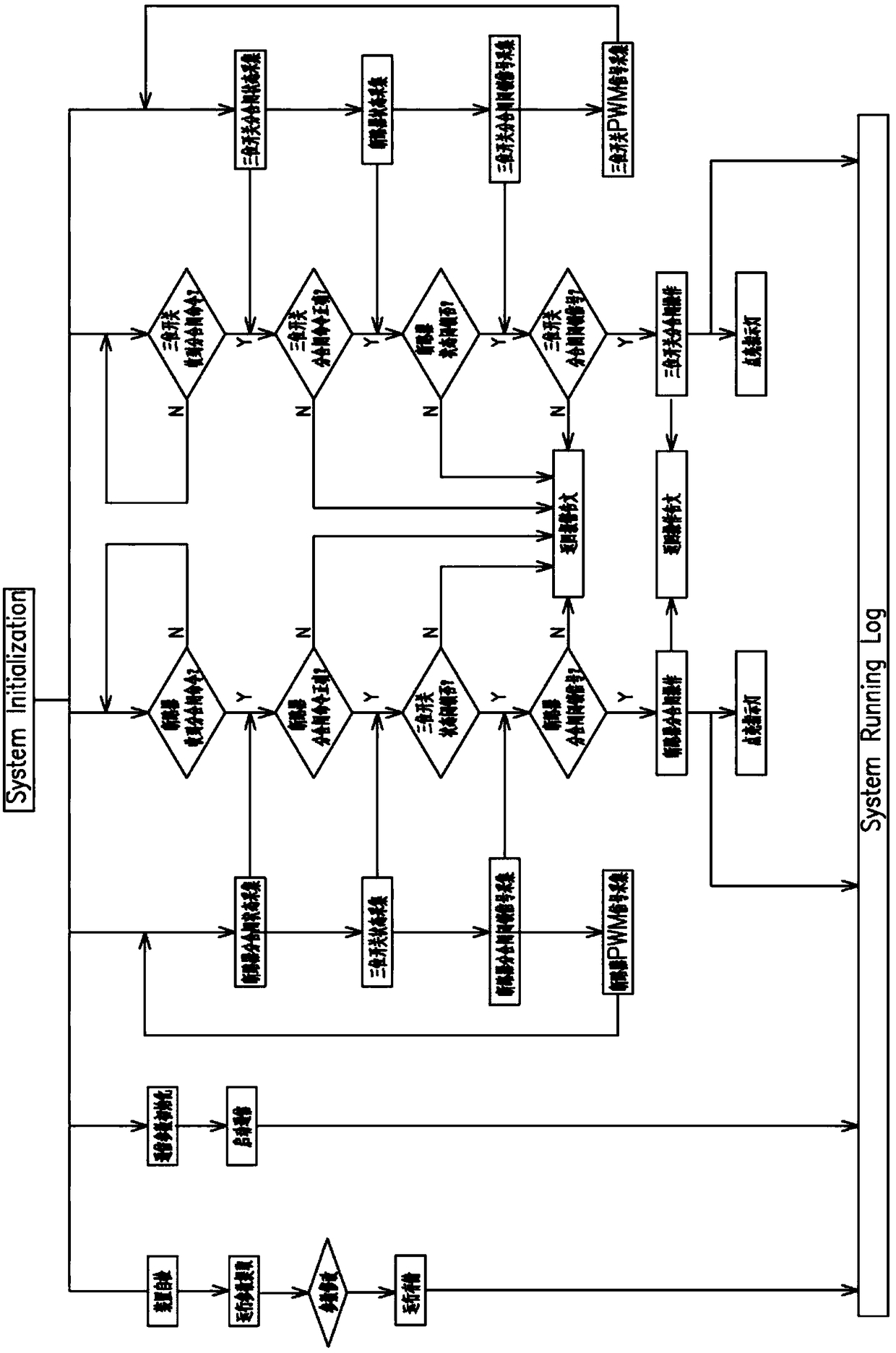

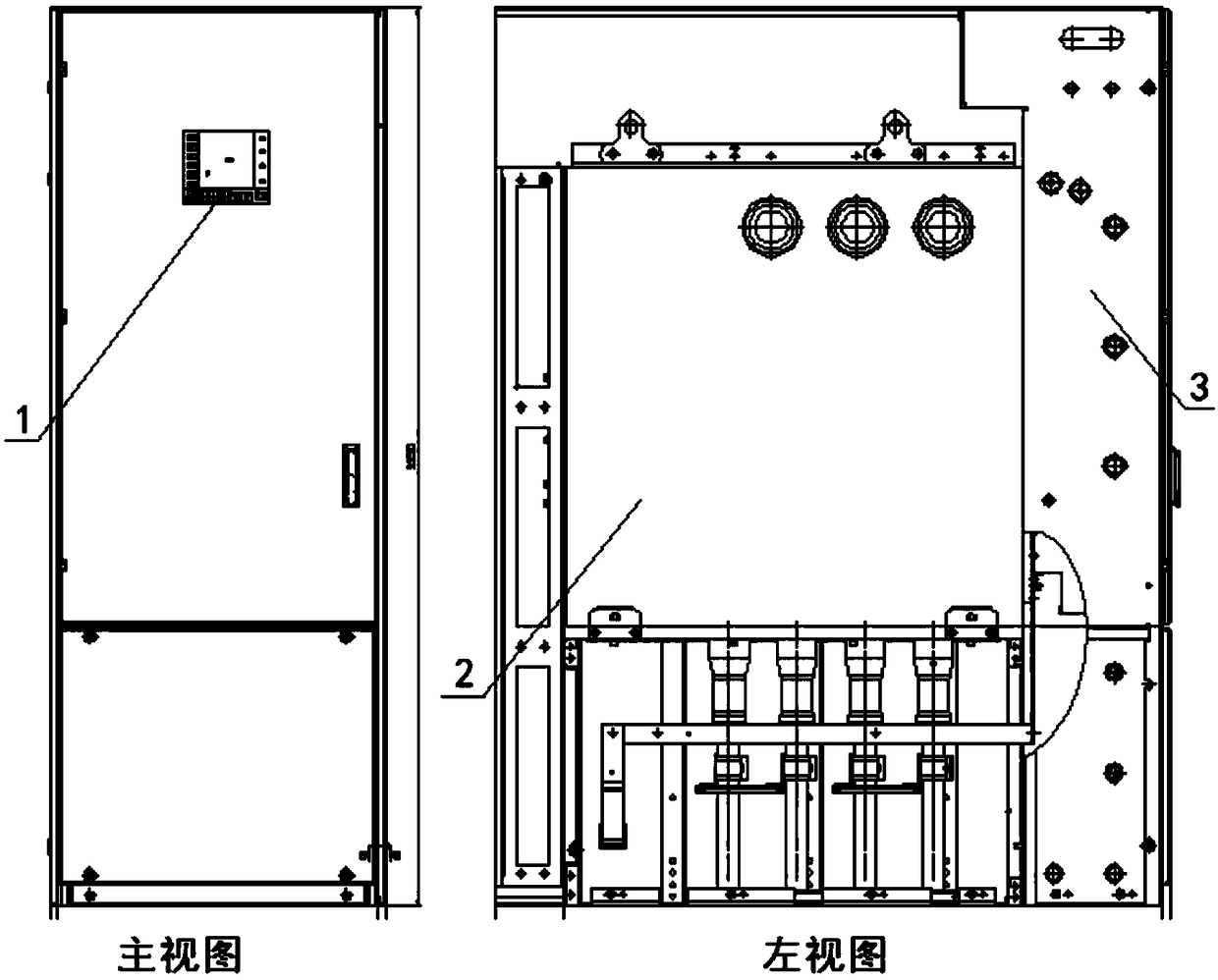

Medium-low voltage switch cabinet and servomotor drive mechanism thereof

InactiveCN108736324AAvoid failures such as heating and burning switchesSave the process of debugging and testingBoards/switchyards circuit arrangementsAC motor controlLow voltageEngineering

The invention relates to a medium-low voltage switch cabinet and a servomotor drive mechanism thereof. The medium-low voltage switch cabinet specifically comprises a circuit breaker servomotor, a three-position switch servomotor and a PWM driver, wherein each moving contact of a circuit breaker is connected with a main shaft of the circuit breaker servomotor through a circuit breaker drive mechanism; the moving contact of a three-position switch is connected with the main shaft of the three-position switch servomotor through a three-position switch drive mechanism; and the PWM driver is in control connection with the circuit breaker servomotor and the three-position switch servomotor. According to the medium-low voltage switch cabinet, a motor mechanism is applied to a C-GIS product to replace a spring mechanism of a traditional circuit breaker, so that mechanical movement faults, such as incomplete closing and excessive closing force of traditional equipment are avoided; the faults, such as switch burnout caused by heating of the contacts of a conductive system are avoided; and meanwhile, the time-consuming and labor-intensive debugging and testing processes of the traditional equipment are also saved.

Owner:PINGGAO GRP +1

Flexible anti-aging shielding twisted pair cable and preparation method thereof

PendingCN110853827ASuppress interferenceContainment leakNon-insulated conductorsFlexible cablesElectrical conductorHigh density

The invention discloses a flexible anti-aging shielding twisted pair cable and a preparation method thereof. The cable is characterized in that four twisted-pair wire cores and a cross-shaped fillingcore material are twisted together to form a cable core, the exterior of the cable core is coated with a fluororesin wrapping tape layer, an aluminum-plastic composite tape wrapping layer, a copper wire shielding winding layer and a silane grafted crosslinked high-density polyethylene insulating layer, the pair-twisted wire core is formed by pair twisting of two insulating wire cores, each insulating wire core comprises an inner conductor and a silane grafted crosslinked low-density polyethylene insulating layer, a nickel copper damage prevention coating and a zinc oxide barrier layer are sequentially sprayed outside the inner conductor and the copper wire shielding winding layer, the cross-shaped filling core material comprises a cross-shaped resin matrix and an aluminum foil layer, an aluminum-plastic composite belt wrapping layer is of an aluminum-plastic composite belt gap wrapping structure, and the aluminum-plastic composite belt comprises an aluminum foil belt outer layer and aPET resin belt inner layer. The cable is advantaged in that the cable effectively suppresses signal interference caused by crosstalk between the pair-twisted wire cores, can effectively suppress a copper damage phenomenon of an insulating layer, and has better mechanical strength, flexibility and electrical characteristics.

Owner:浙江元通线缆制造有限公司

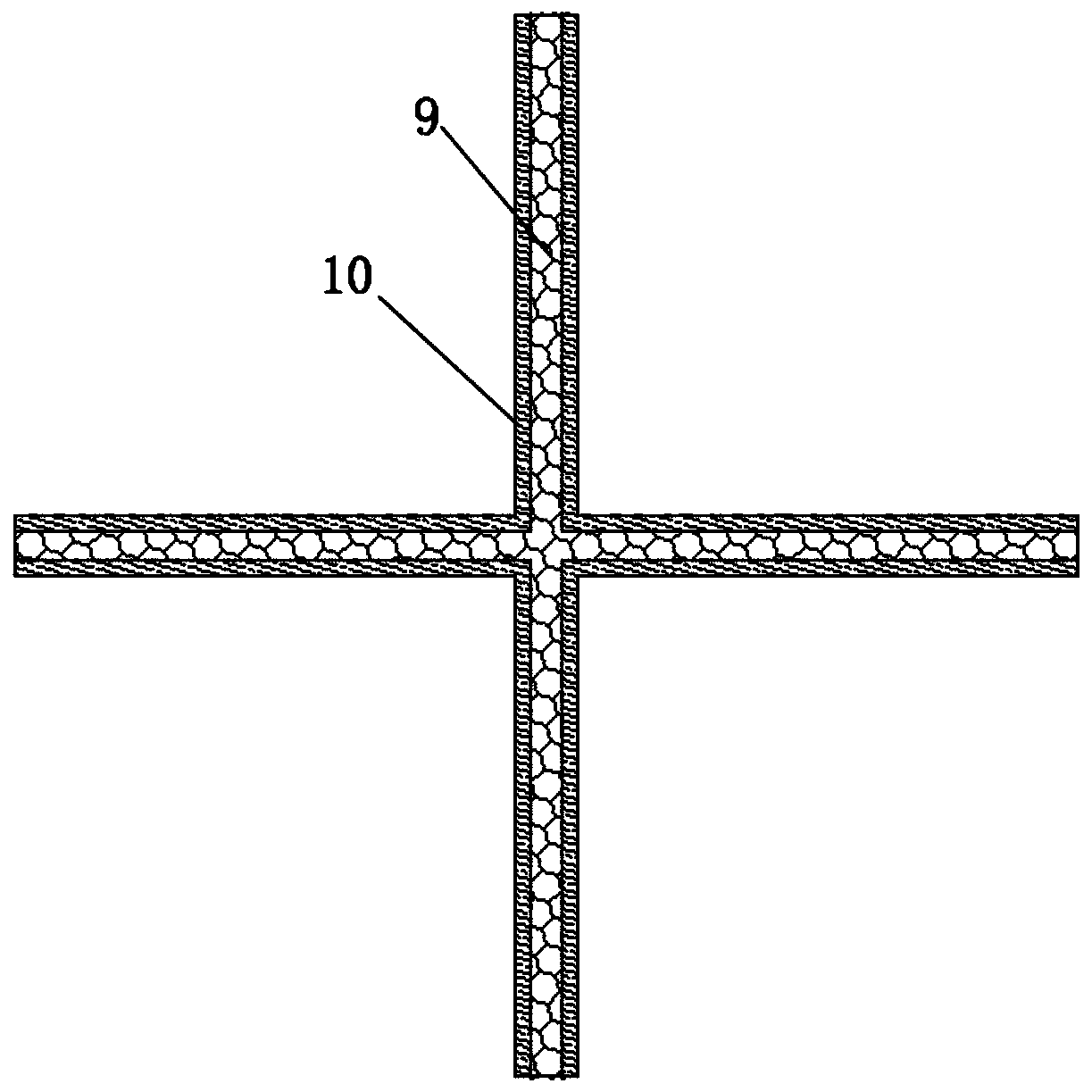

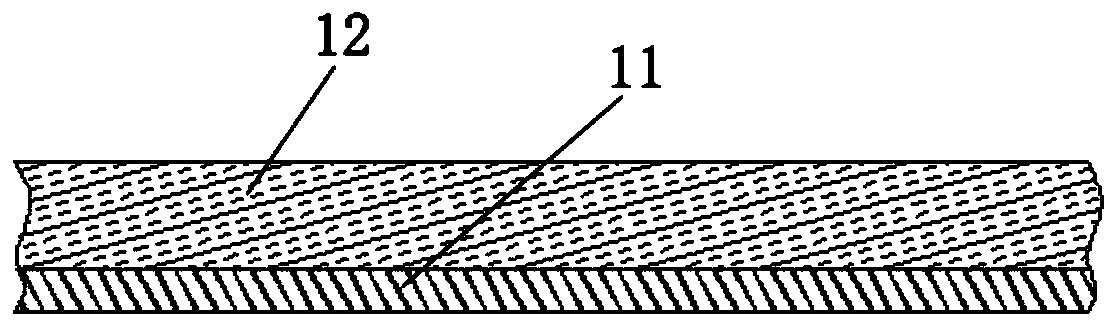

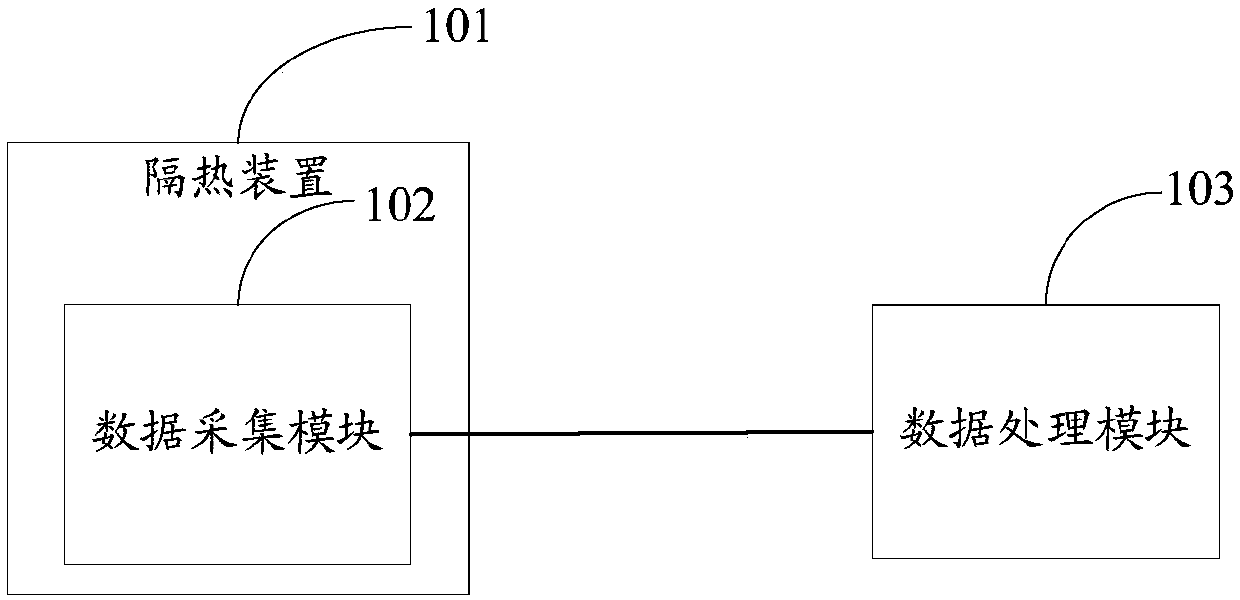

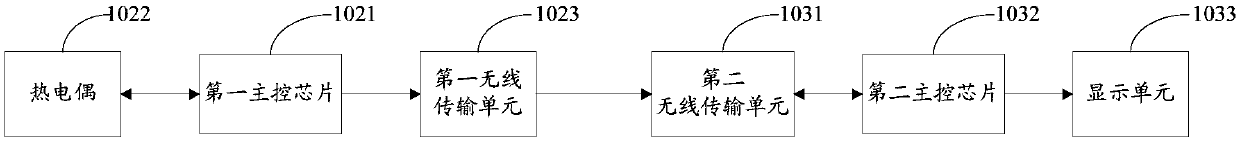

Temperature monitoring device

PendingCN109580022AGuaranteed Electrical CharacteristicsRealize monitoringThermometer detailsThermometers using electric/magnetic elementsTest objectCollections data

The invention discloses a temperature monitoring device, which comprises a heat isolation device, a data collection module and a data processing module, wherein a tested object is arranged outside theheat isolation device; the data collection module is arranged inside the heat isolation device and is used for collecting temperature signals of the tested object and converting the temperature signals into thermoelectromotive force signals; and the data processing module is connected with the data collection module and is used for converting the thermoelectromotive force signals into the temperature value. The temperature monitoring device has the advantages that through the arrangement of the heat isolation device, the temperature of the data collection module is kept below 60 DEG C, so that the electric characteristics of the data collection module are ensured; and the monitoring on the temperature in various high-temperature environment can be realized.

Owner:中国船舶工业综合技术经济研究院

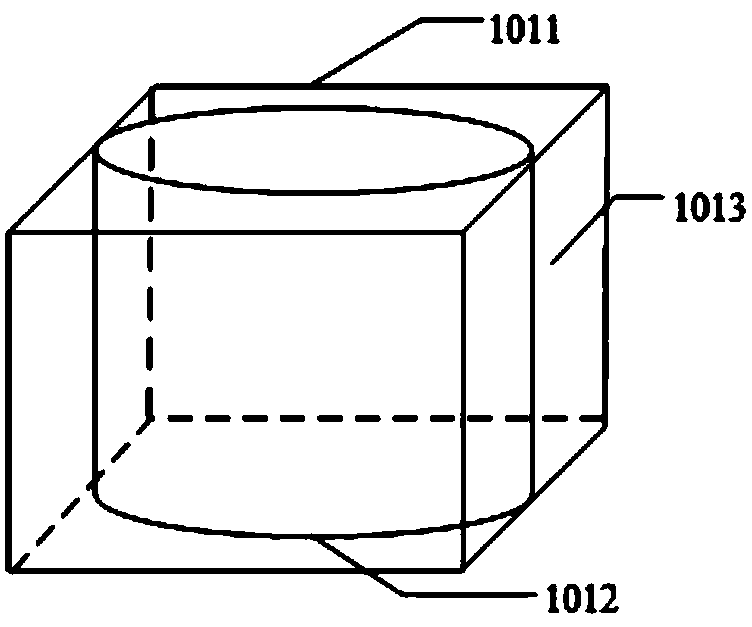

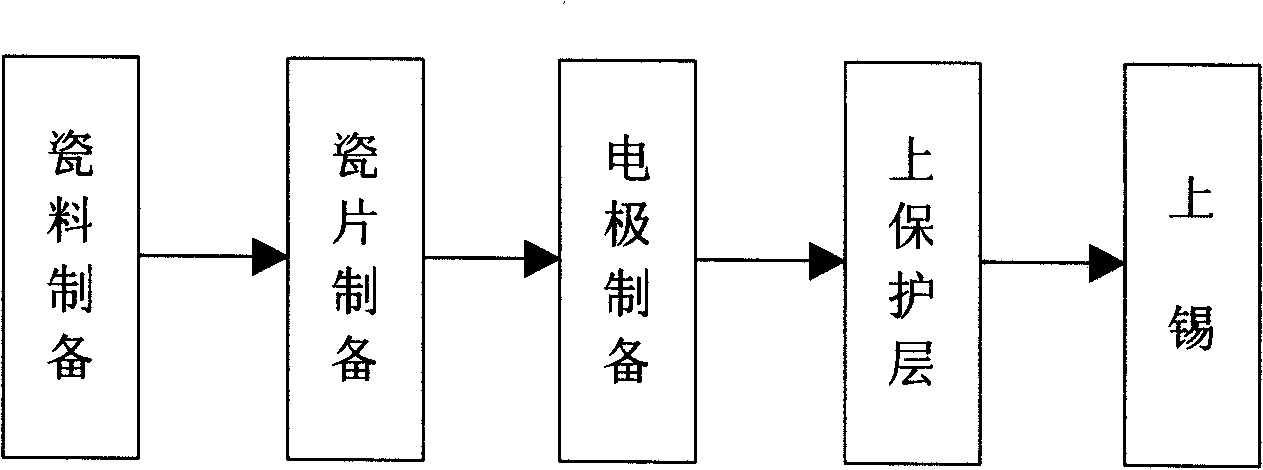

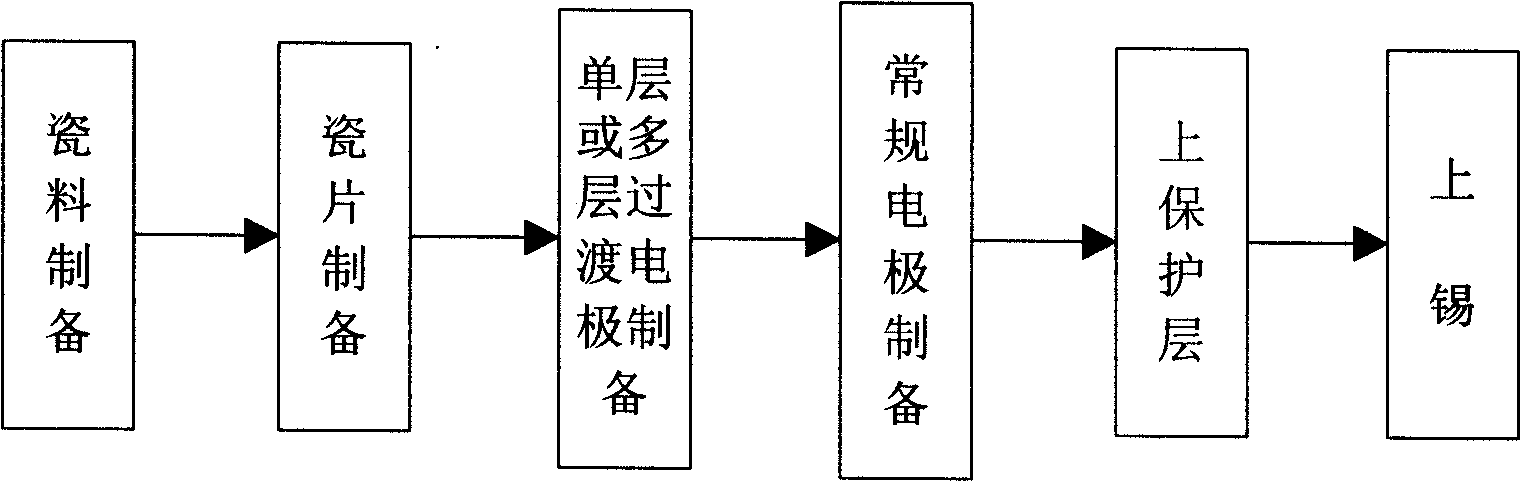

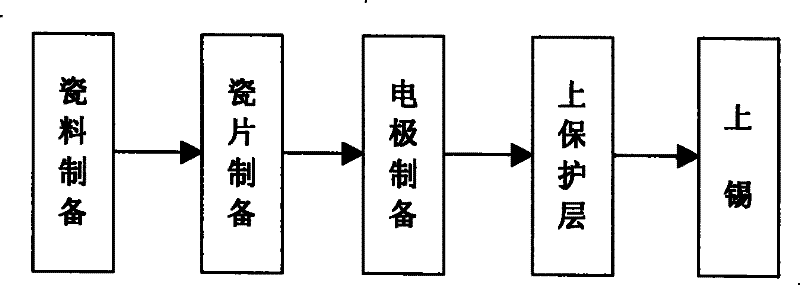

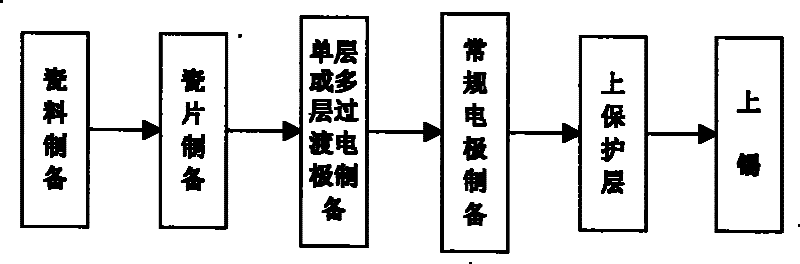

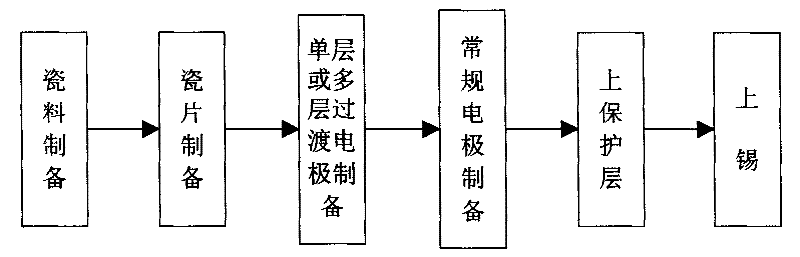

Method for preparing heat impact resisting ceramic capacitor

ActiveCN101494116AImproved thermal shock resistanceSolve thermal stressFixed capacitor electrodesThermal conductivityMetallurgy

The invention discloses a preparation method of a heat shock-resistant ceramic capacitor and pertains to the field of electric elements and material technology, in particular to a preparation method of a ceramic capacitor; the preparation method comprises the steps: the preparation of transition electrodes is added into the conventional ceramic-capacitor preparation engineering; single-layer or multi-layer transition electrodes with different silver contents are prepared at two sides of a ceramic chip; due to the different silver contents in the transition electrodes and electrode materials, the thermal conductivities of the transition electrodes and electrode materials are different; therefore, thermal gradient exists between the transition electrodes, which can relieve the thermal stress produced by the synergy of the ceramic capacitor in an environment in which the temperature changes dramatically. On the basis of ensuring electrical characteristics of the ceramic capacitor, the preparation method significantly improves the heat shock resistance of the ceramic capacitor so that the ceramic capacitor can adapt to the environment in which the temperature changes between minus 55 DEG C to 125 DEG C and particularly meets the performance requirements of a special ceramic capacitor in automotive electronics.

Owner:CHENGDU HONGMING & UESTC NEW MATERIALS

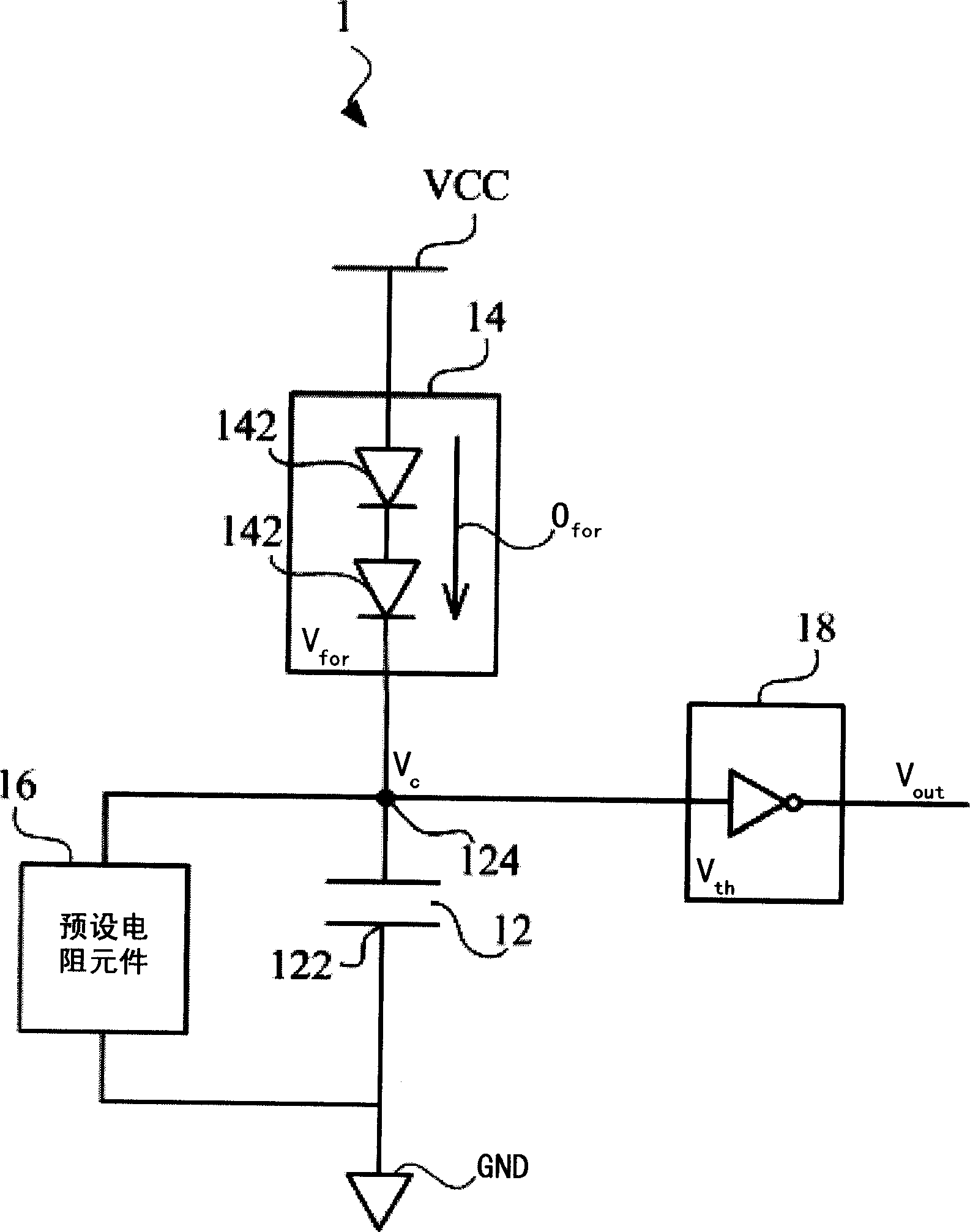

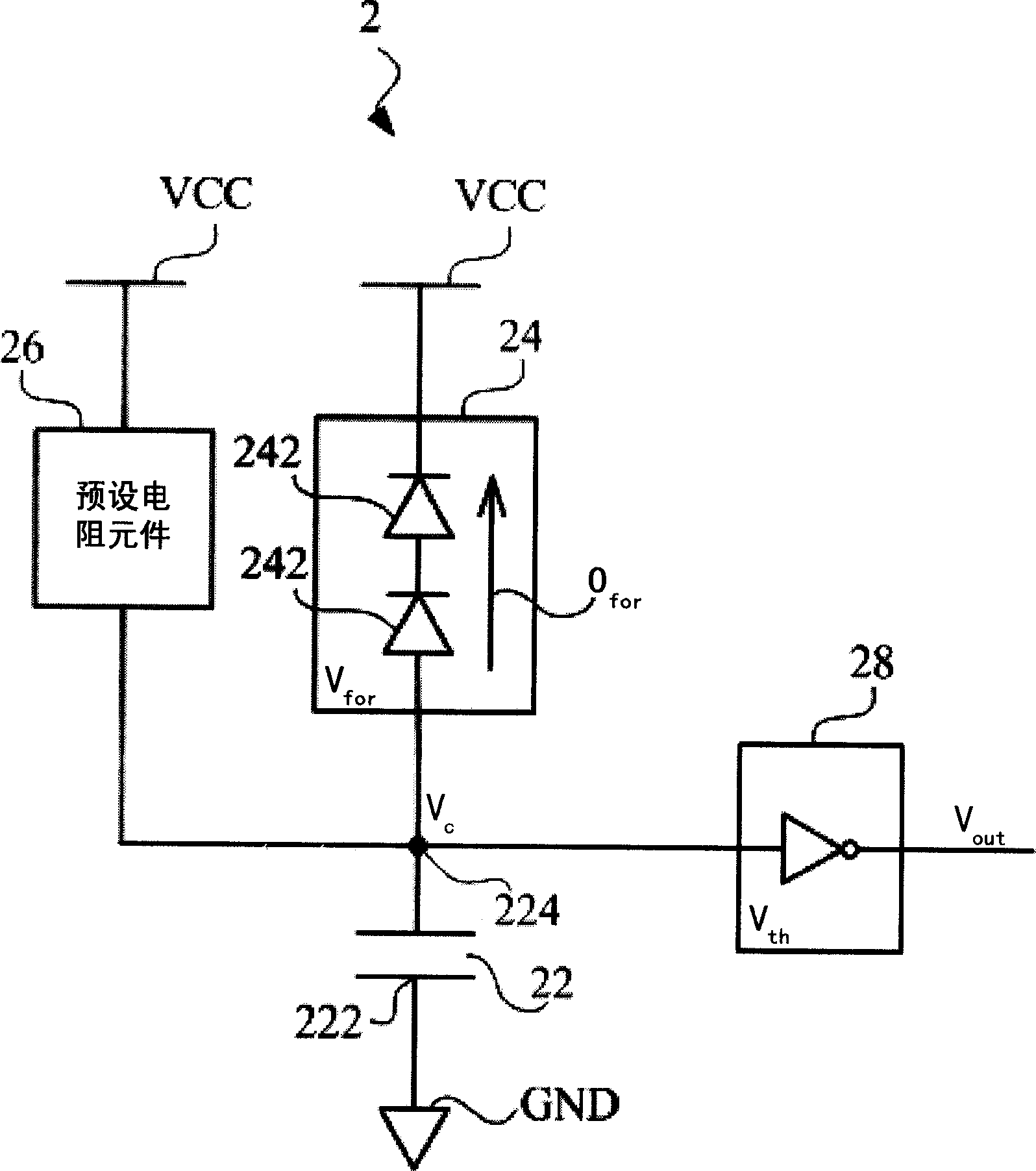

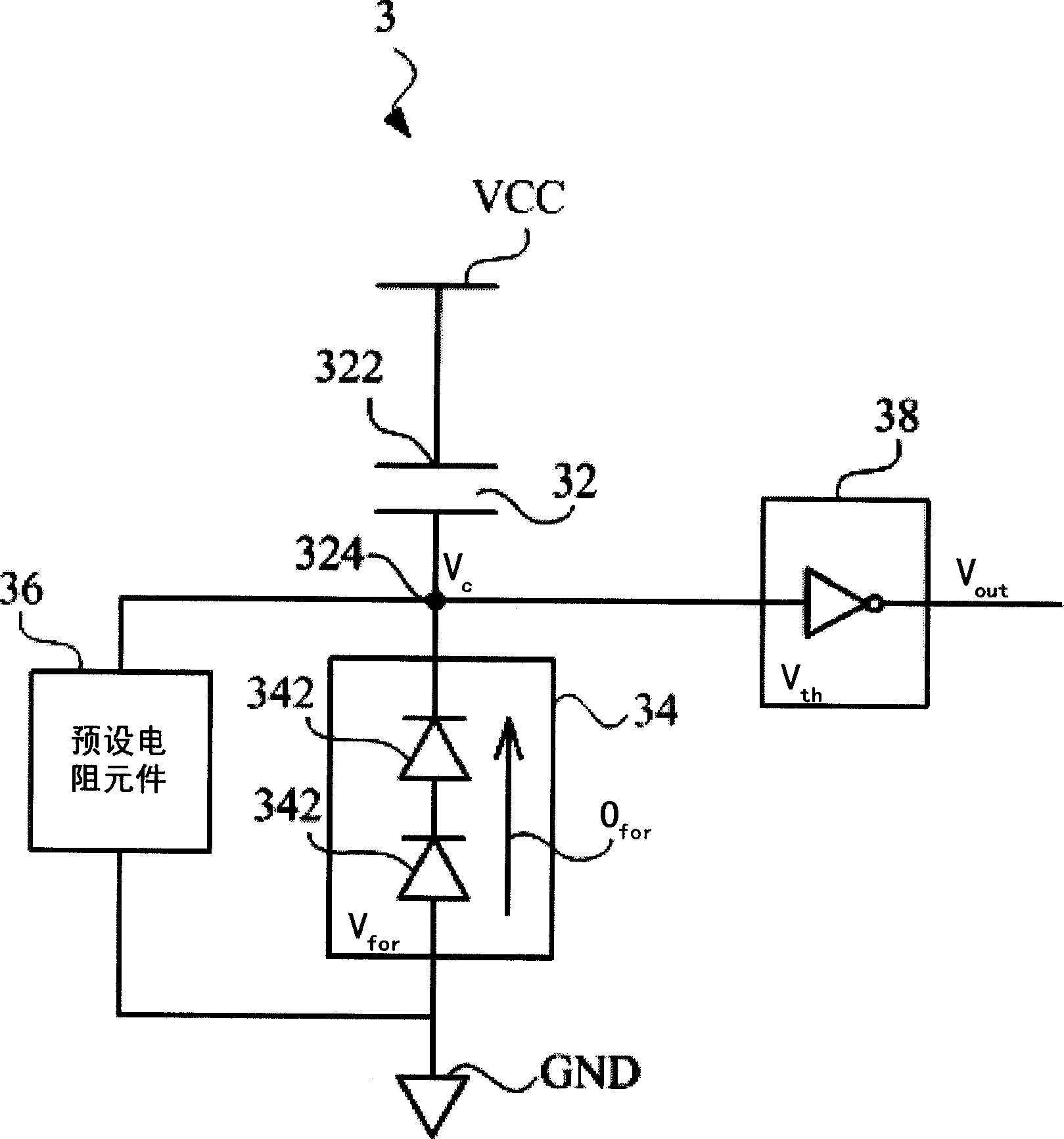

Instantaneous voltage detetion circuit

InactiveCN1743852AQuick checkAccurate detectionCurrent/voltage measurementEmergency protective arrangements for limiting excess voltage/currentCapacitanceElectrical resistance and conductance

This invention provides a instantaneous voltage detection circuit for electronic system containing power supply and grounding socket, said circuit containing a capacitance device, a rectification component, a preset resistance element and a detection element, wherein the capacitance device containing a first end coupling to a grounding socket of an electronic system and a second end series coupling to power supply socket through rectification component whose positive operation direction pointed to said capacitance device. When the instantaneous voltage occurs in power supply socket and the voltage in second end of said capacitance device is higher than threshold voltage, the detection element outputting a voltage to represent the generation of said instantaneous voltage.

Owner:NOVATEK MICROELECTRONICS CORP

Display backplane, manufacturing method thereof, and display device

ActiveCN109148482BImprove work performanceImprove cooling efficiencySemiconductor/solid-state device detailsSolid-state devicesDisplay deviceThin membrane

Embodiments of the present invention provide a display backplane, a manufacturing method thereof, and a display device. The display backplane includes: a base, a transparent heat conduction layer disposed on the base, and an array structure layer disposed on the heat conduction layer; the array structure layer includes a light-shielding layer, a first thin film transistor, and a second thin film transistor, so The light-shielding layer is arranged between the transparent thermal conduction layer and the first thin film transistor. The transparent heat conduction layer includes a transparent conductive layer, a transparent semiconductor layer, or a transparent conductive layer and a transparent semiconductor layer. The present invention can effectively solve the problem of separation of characteristics of the driving thin film transistor and the switching thin film transistor existing in the existing OLED display device by disposing the transparent heat conduction layer between the base and the array structure layer.

Owner:BOE TECH GRP CO LTD +1

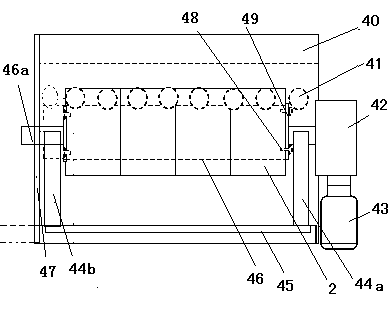

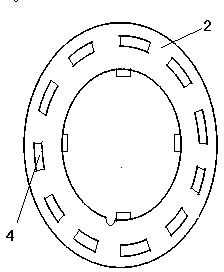

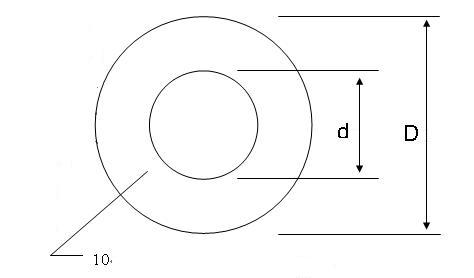

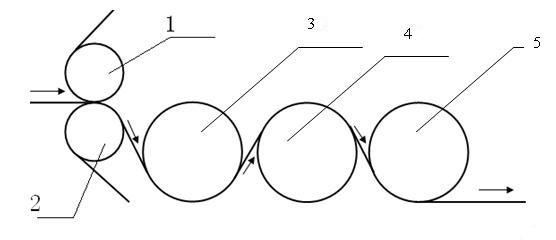

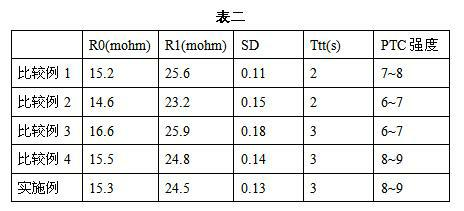

PTC (positive temperature coefficient) ring production method

InactiveCN102522171AGuaranteed Electrical CharacteristicsIncrease productivityCurrent responsive resistorsPositive temperature coefficient thermistorsCross-linkMetal foil

The invention provides a PTC (positive temperature coefficient) ring production method. A PTC ring is a circular plate in a dimension of the outer diameter D, the inner diameter d and the thickness and comprises two metal foils and a PTC material layer. The PTC material layer is positioned between the two metal foils, and the upper metal foil, the lower metal foil, an upper metal nickel and a lower metal nickel are assembled into a battery cap to form a component which is connected with a power source to form a conductive loop. The production method includes steps: firstly, using macromolecule-based PTC as the PTC ring, using a twin-screw extruder for extruding and pelleting, and using a single-screw extruder to extrude the generated pellets into a laminated core; secondly, compositing the laminated core with the conductive metal foils, and cooling, thirdly, using gamma-ray (Co60) or electron beams to irradiate the composite plate; fourthly, stamping the irradiated cross-linked composite plate into a circular chip in a target dimension; and fifthly, subjecting the circular chip to thermal shock to obtain the finished PTC ring.

Owner:SHANGHAI CHANGYUAN WAYON CIRCUIT PROTECTION CO LTD

Method of forming replacement gate of semiconductor device and method of manufacturing semiconductor device

ActiveCN103854980BGuaranteed electrical characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricGate stack

The invention provides a method for forming a semiconductor-device replacement gate and a method for manufacturing the semiconductor device. The method includes: providing a semiconductor substrate which includes an N-type area and a P-type area; forming a sacrifice-gate stack on each of the N-type area and the P-type area respectively, wherein each sacrifice-gate stack includes a sacrifice-gate dielectric and a sacrifice-gate electrode, the sacrifice-gate electrode is located on the sacrifice-gate dielectric and the sacrifice-gate electrode in the N-type area is higher than the gate electrode of the P-type area; forming a side wall around each sacrifice-gate stack; forming source-drain areas on the semiconductor substrate at the two sides of the sacrifice-gate stacks; removing the sacrifice-gate stack in the N-type area so as to form a first opening in the side wall; and forming an N-type replacement-gate stack in the first opening; removing the sacrifice-gate stack in the P-type area so as to form a second opening; forming a P-type replacement-gate stack in the second opening; and performing planarization until the N-type replacement-gate stack is exposed. The method is simple in process.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

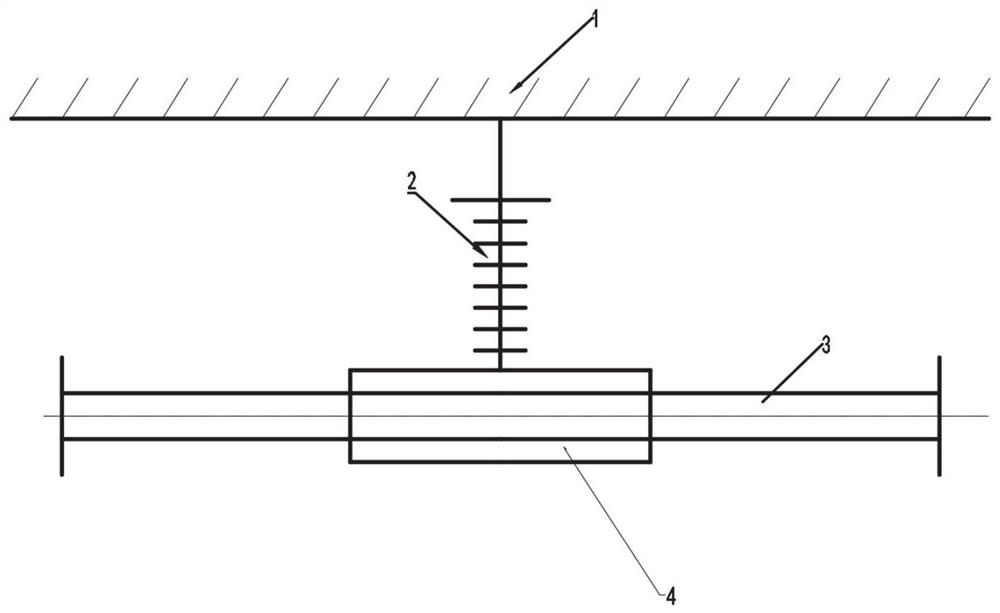

Pipe gallery type jumper supporting structure and power transmission system and method

ActiveCN112886511AGuaranteed Electrical CharacteristicsReduce discharge and other phenomenaOverhead installationElectrical performanceFastener

The invention provides a pipe gallery type jumper supporting structure, which comprises a sleeve and a plurality of wire supports connected with the sleeve, wherein the wire support is used for fixing a plurality of wires of the jumper in the sleeve; during installation, the wires are fixed on a wire clamp of the wire support, and the wire clamp holds the wires under the action of a built-in spring; and the sleeve of the pipe gallery type jumper supporting mechanism is arranged on the outer side of the wire in a sleeving mode and fixed to a fixing support of a hanging support through a fastener, and finally a sealing end cover is covered and fastened through the fastener. The electrical characteristics of the jumper can be stably and effectively ensured, the phenomena of discharge and the like caused by irregularity of the jumper are reduced, and the electrical performance of the jumper is improved.

Owner:EAST INNER MONGOLIA ELECTRIC POWER COMPANY +4

Method for preparing heat impact resisting ceramic capacitor

ActiveCN101494116BAvoid heat stressGuaranteed electrical characteristicsFixed capacitor electrodesMetallurgyCeramic capacitor

The invention discloses a preparation method of a heat shock-resistant ceramic capacitor and pertains to the field of electric elements and material technology, in particular to a preparation method of a ceramic capacitor; the preparation method comprises the steps: the preparation of transition electrodes is added into the conventional ceramic-capacitor preparation engineering; single-layer or multi-layer transition electrodes with different silver contents are prepared at two sides of a ceramic chip; due to the different silver contents in the transition electrodes and electrode materials, the thermal conductivities of the transition electrodes and electrode materials are different; therefore, thermal gradient exists between the transition electrodes, which can relieve the thermal stress produced by the synergy of the ceramic capacitor in an environment in which the temperature changes dramatically. On the basis of ensuring electrical characteristics of the ceramic capacitor, the preparation method significantly improves the heat shock resistance of the ceramic capacitor so that the ceramic capacitor can adapt to the environment in which the temperature changes between minus 55 DEG C to 125 DEG C and particularly meets the performance requirements of a special ceramic capacitor in automotive electronics.

Owner:CHENGDU HONGMING & UESTC NEW MATERIALS

A Method of Saving Vdmosfet Chip Area in Low and Medium Voltage

ActiveCN103745930BGuaranteed electrical characteristicsReduce areaSolid-state devicesSemiconductor/solid-state device manufacturingLow voltageOptoelectronics

The invention discloses a method for saving the area of a medium- and low-voltage VDMOSFET chip. Electrical properties of a VDMOS device can be guaranteed, and manufacturing cost is minimized. The method comprises the following steps: firstly, an active region (1a) and a non-corrosive region (1b) are formed on polycrystalline silicon through corrosion; a polycrystalline silicon region (2) is formed on the active region (1a) through deposition, and the polycrystalline silicon region (2) contains a polycrystalline silicon lead region (2a) and a polycrystalline silicon terminal structural region (2b); N+source regions (3) are formed below the polycrystalline silicon lead region (2a) and below the space between the polycrystalline silicon lead region (2a) and the polycrystalline silicon terminal structural region (2b) through diffusion; contact holes (4) are formed on the polycrystalline silicon region; a metal electrode (5) is formed on the active region (1a); the metal electrode (5) extends to cover all the contact holes (4); the contact holes (4) are connected to the N+source regions (3) through the metal electrode (5); and the metal electrode (5) and part of the polycrystalline silicon terminal structural region (2b) are overlapped.

Owner:BEIJING MXTRONICS CORP +1