A kind of preparation method of semiconductor device

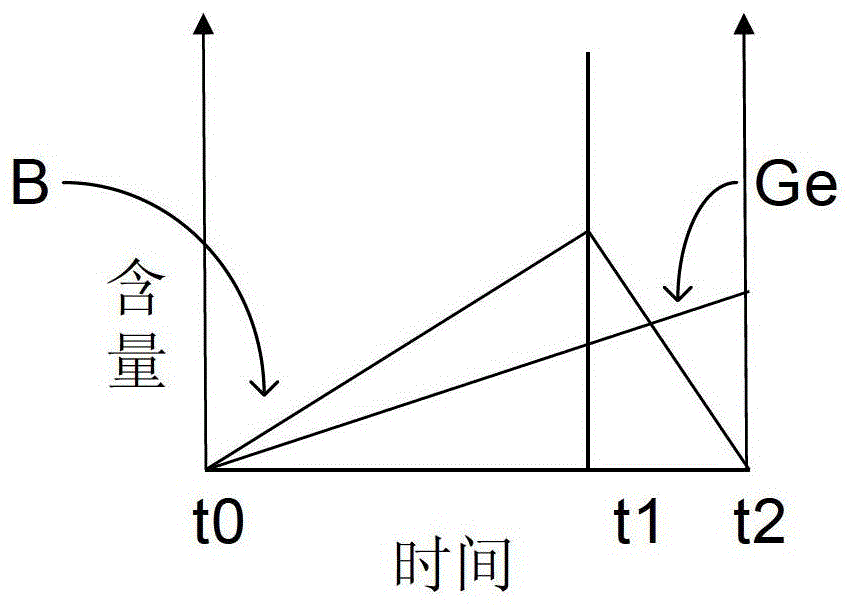

A semiconductor and device technology, applied in the field of semiconductor device preparation, can solve the problems of accelerating short channel effect, device performance degradation, boron diffusion, etc., and achieve the effect of eliminating short channel effect, good performance and reducing junction leakage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

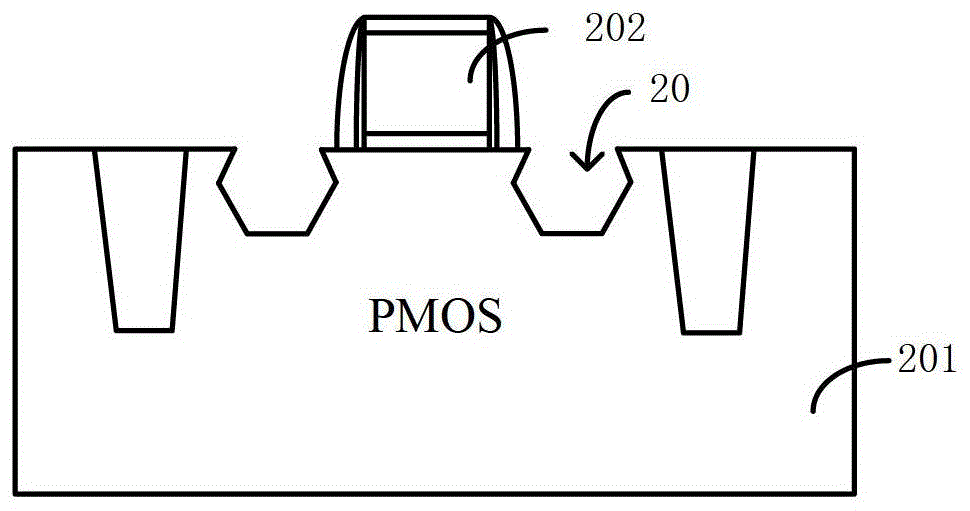

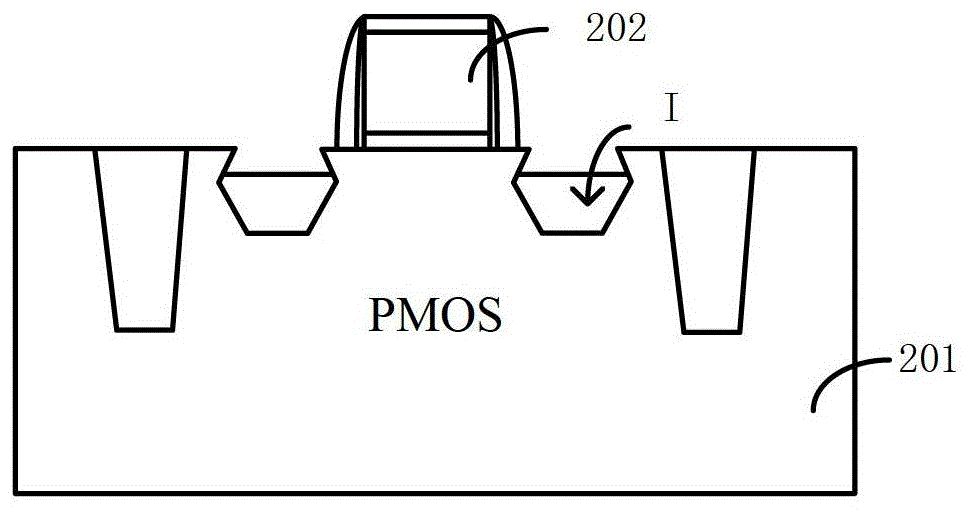

Embodiment Construction

[0036] In the following description, a lot of specific details are given in order to provide a more thorough understanding of the present invention. However, it is obvious to those skilled in the art that the present invention can be implemented without one or more of these details. In other examples, in order to avoid confusion with the present invention, some technical features known in the art are not described.

[0037] In order to thoroughly understand the present invention, a detailed description will be provided in the following description to illustrate the manufacturing method of the semiconductor device of the present invention. Obviously, the implementation of the present invention is not limited to the specific details familiar to those skilled in the semiconductor field. The preferred embodiments of the present invention are described in detail as follows. However, in addition to these detailed descriptions, the present invention may also have other embodiments.

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More