Method for manufacturing MOS grid device

A manufacturing method and gate technology, which are used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of increasing manufacturing difficulty and cost, inability to achieve current density, and many steps, and reduce etching. Process difficulty, ensuring uniformity and consistency, and reducing the effect of area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

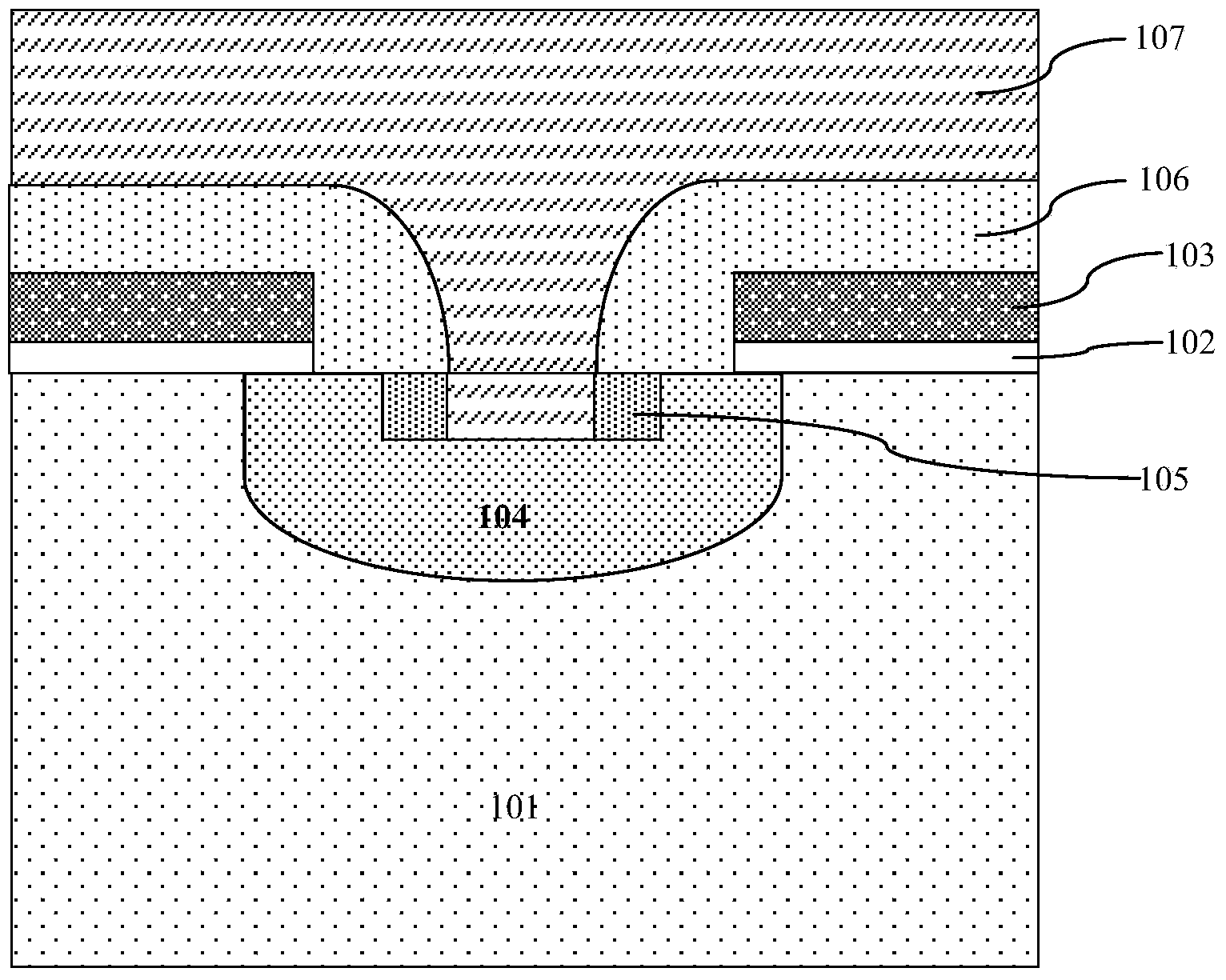

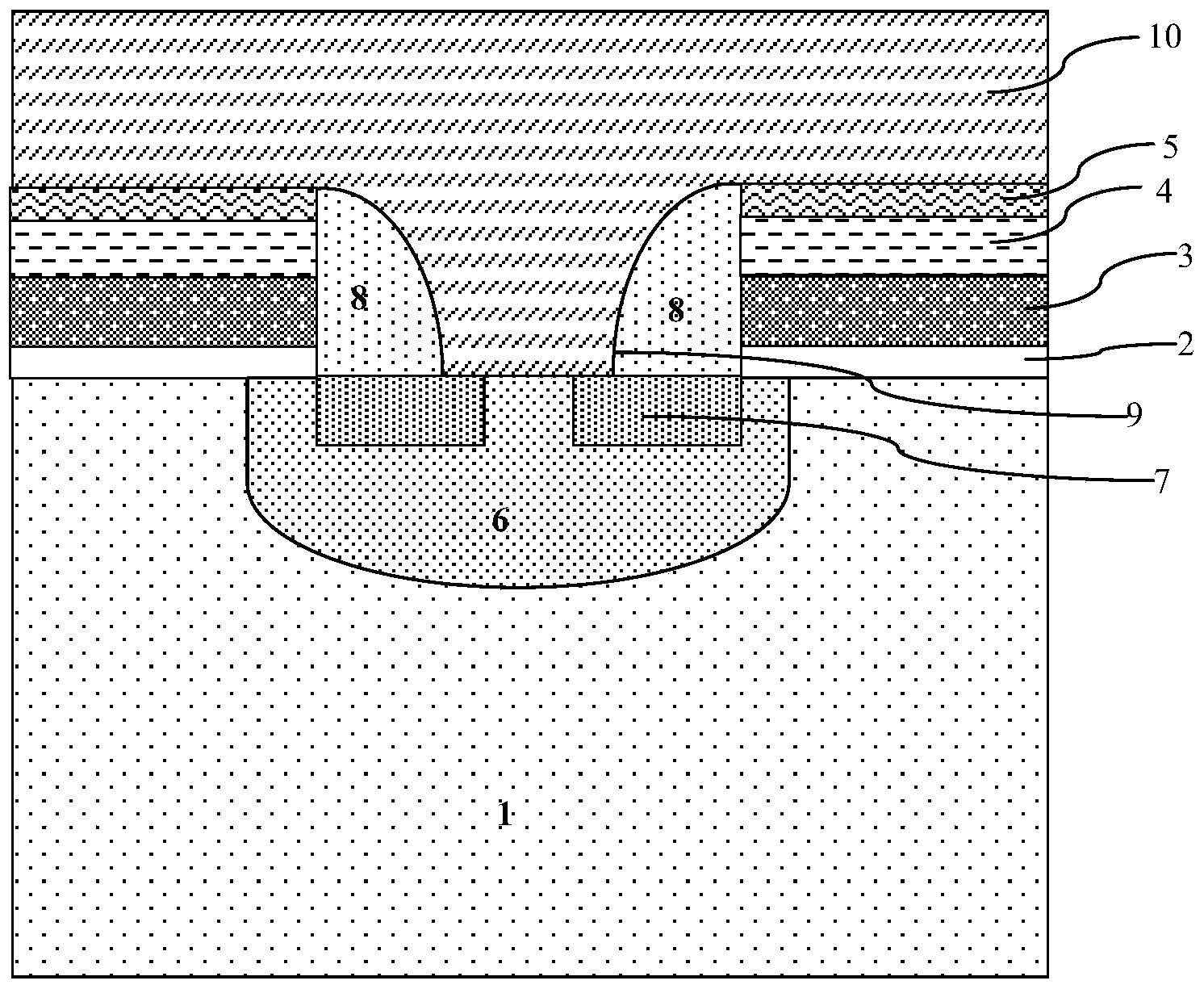

[0032] Such as figure 2 Shown is a structural diagram of the MOS gate device formed by the method of the embodiment of the present invention. The MOS gate device in the embodiment of the present invention includes a power MOSFET, a MOS gate thyristor, an insulated gate bipolar transistor, and a gate turn-off device. The manufacturing method of the MOS gate device in the embodiment of the present invention includes steps:

[0033] Step 1: Provide a semiconductor substrate 1 , and sequentially form a gate dielectric layer 2 , a gate layer 3 , a gate booster layer 4 and an etch stop layer 5 on the surface of the semiconductor substrate 1 . Preferably, the semiconductor substrate 1 is a silicon substrate, the gate dielectric layer 2 is an oxide layer, the gate layer 3 is a polysilicon layer, and the gate booster layer 4 is an oxide layer.

[0034] Step 2, using a photolithographic etching process to form a gate pattern structure, the gate is composed of the etched gate dielectri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More