Quick counting and monitoring method of silicon substrate chip dislocation defects

A chip, silicon-based technology, applied in the field of rapid statistical monitoring of dislocation defects in silicon-based chips, can solve the problems of long time consumption, small observable area, low overall efficiency, etc. The effect of reducing labor costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

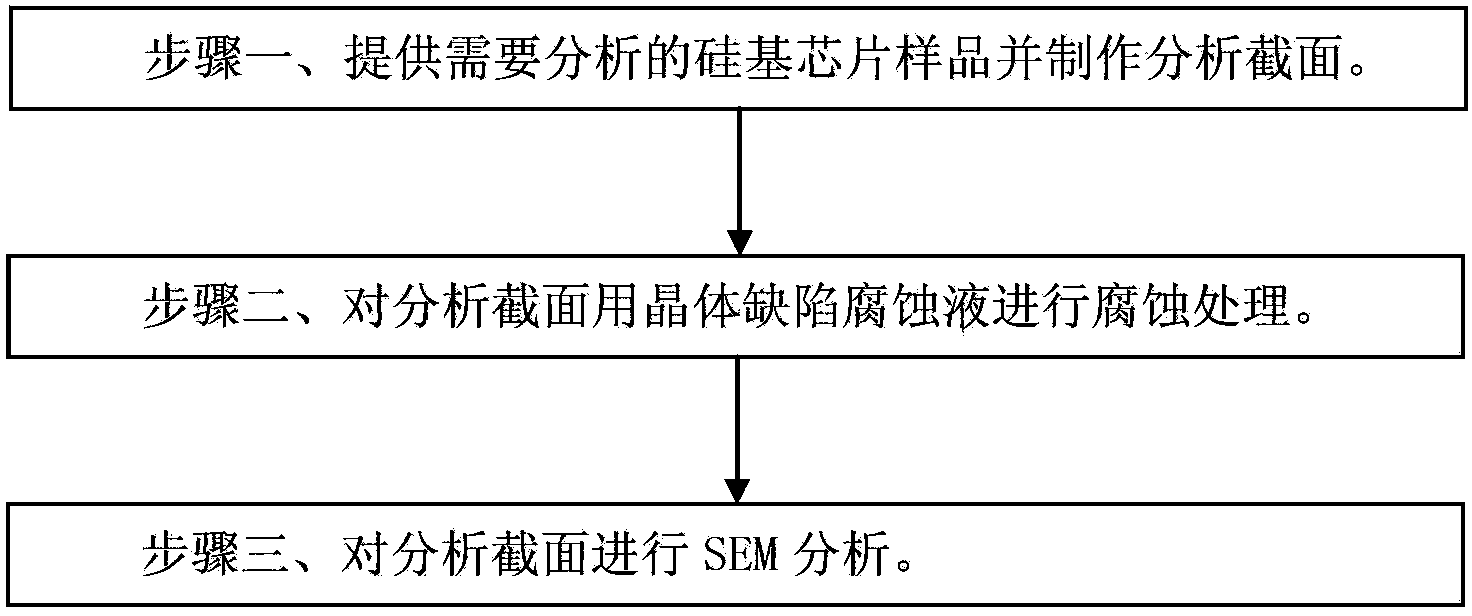

[0042] Such as figure 1 As shown, it is a flow chart of the method of the embodiment of the present invention; the rapid statistical monitoring method of the silicon-based chip dislocation defect in the embodiment of the present invention includes the following steps:

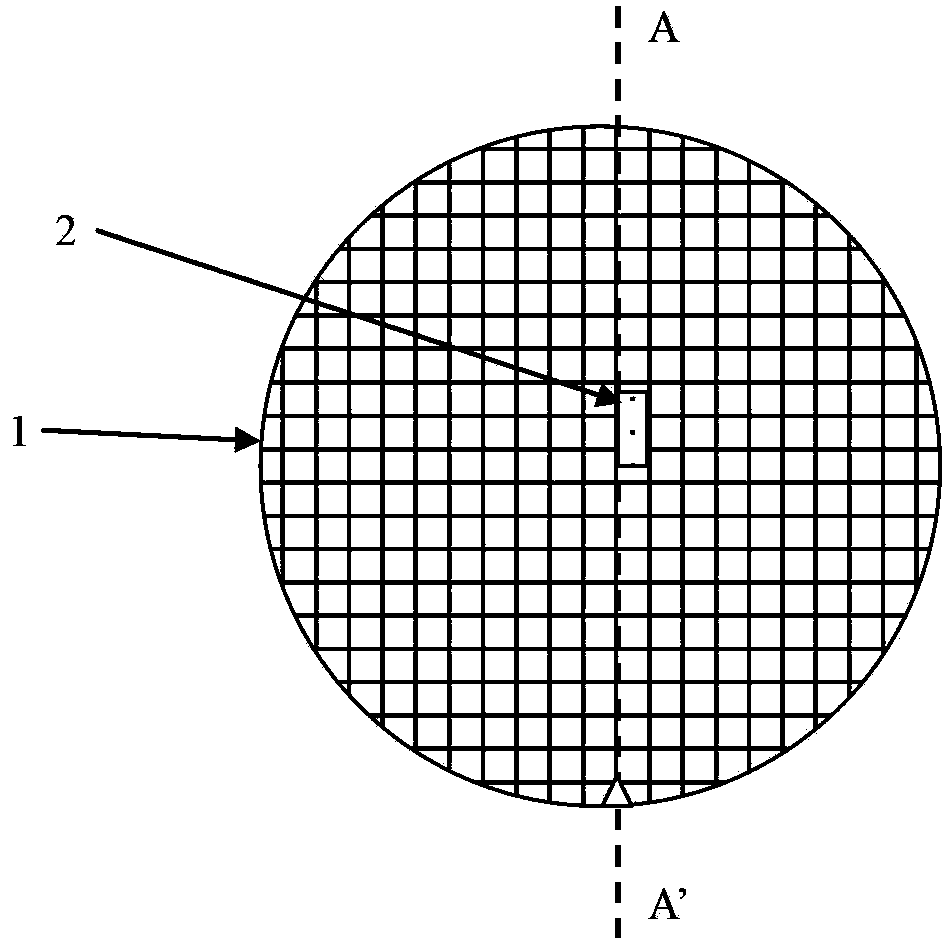

[0043] Step 1. Provide a silicon-based chip sample to be analyzed, and make an analysis section of the silicon-based chip sample that needs to be analyzed. The crystal plane index of the analysis section belongs to the {110} crystal plane family.

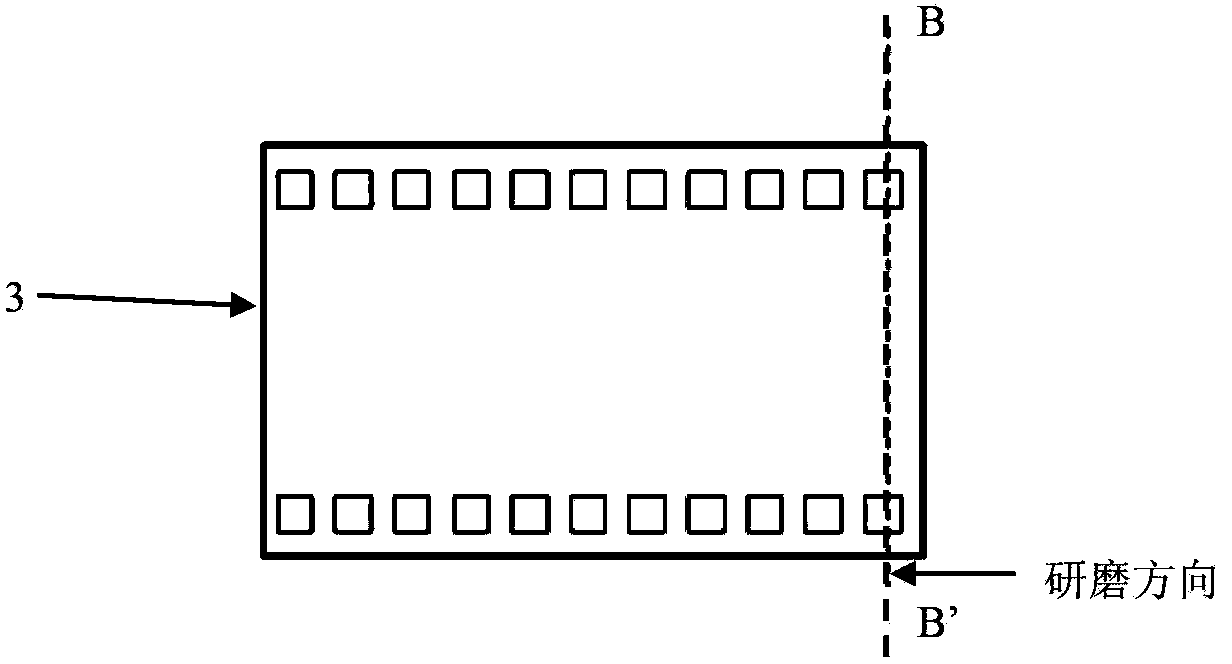

[0044] Such as figure 2 As shown, it is a schematic diagram of the preparation of the analysis section of the wafer-level sample in the method of the embodiment of the present invention; for silicon wafers. The crystal plane index of the profile of the dotted line AA’ belongs to the {110} crystal plane family, so it is only necessary to follow figure 2 The analysis section can be formed by manually splitting in the direction of the dotted line AA' in .

[0045]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More