Storage cell, formation method of storage cell and reading method of storage cell

A memory unit and special zone technology, applied in static memory, read-only memory, information storage, etc., can solve the problems of limited drive capacity, large chip area, and high process cost, and achieve the goal of reducing drive capacity, improving integration, and reducing costs Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] As mentioned in the background, the process cost of the memory needs to be further reduced.

[0026] Research has found that the process cost of memory is affected by the degree of memory integration. The higher the degree of memory integration, the greater the number of memories that can be formed on a single wafer, and the lower the memory process cost. In the prior art, the chip area occupied by the selection transistor connected to the source terminal of the memory unit is generally large, so that the selection transistor has a relatively large driving capability and meets the requirements of the read operation of the memory, but the volume of the selection transistor If it is large, the integration degree of the memory will be reduced, which is not conducive to the reduction of the process cost of the memory.

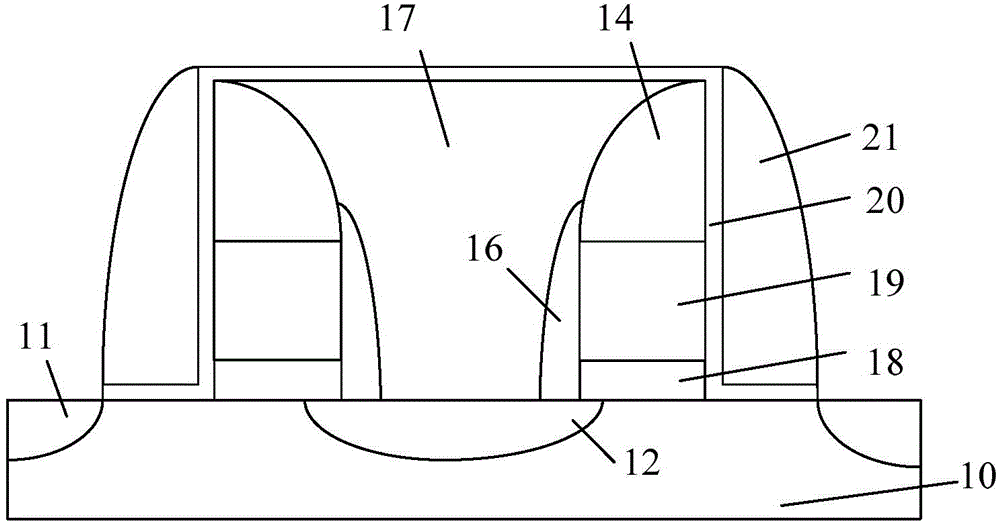

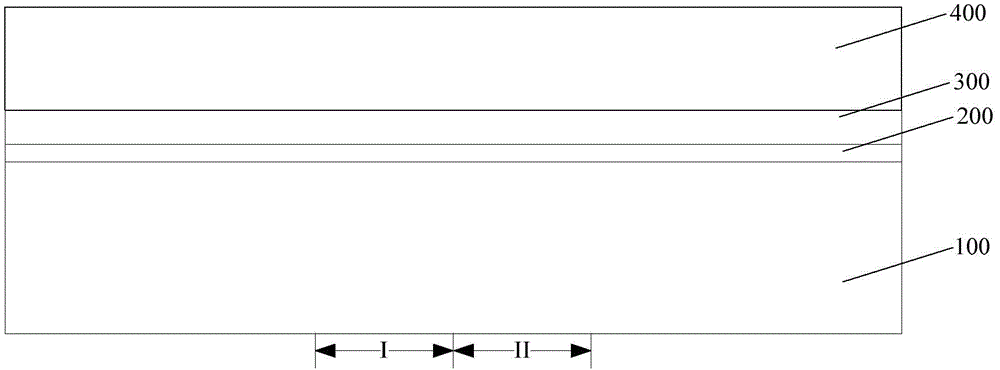

[0027] In order to reduce and solve the above problems, an embodiment of the present invention provides a memory cell and its forming method and driving met...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More