A lateral trench insulated gate bipolar transistor and its preparation method

A technology of bipolar transistors and lateral trenches, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of large turn-off loss, limited application, low electron mobility, etc., to reduce the forward guide The effect of reducing the voltage drop, improving the current drive capability, and increasing the layout area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

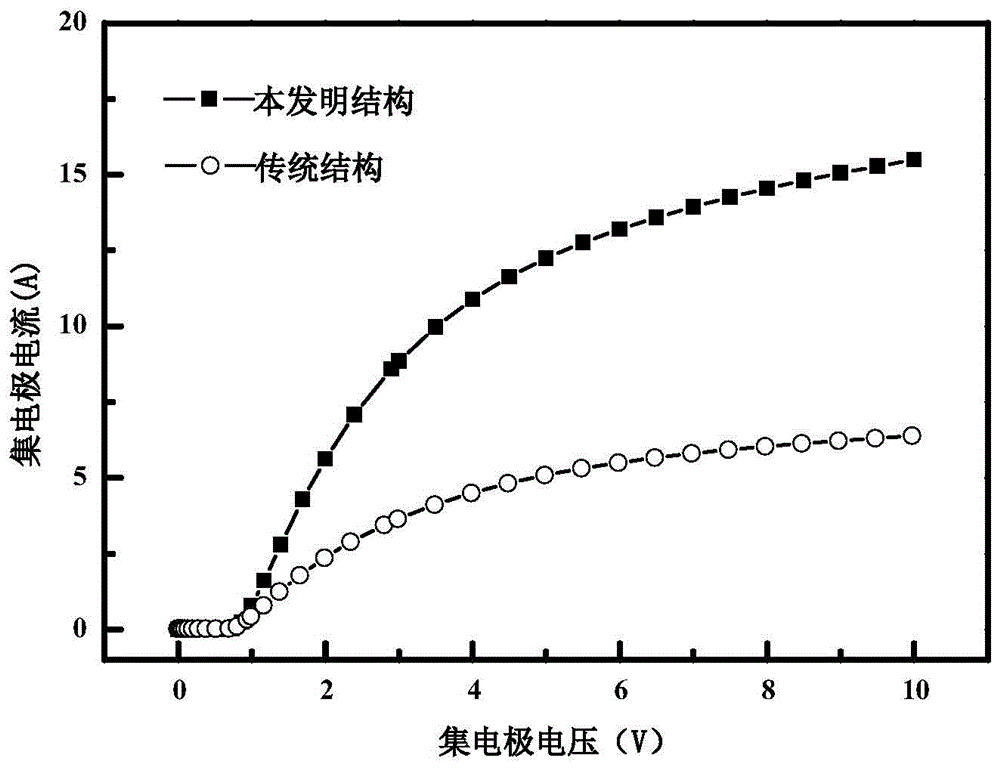

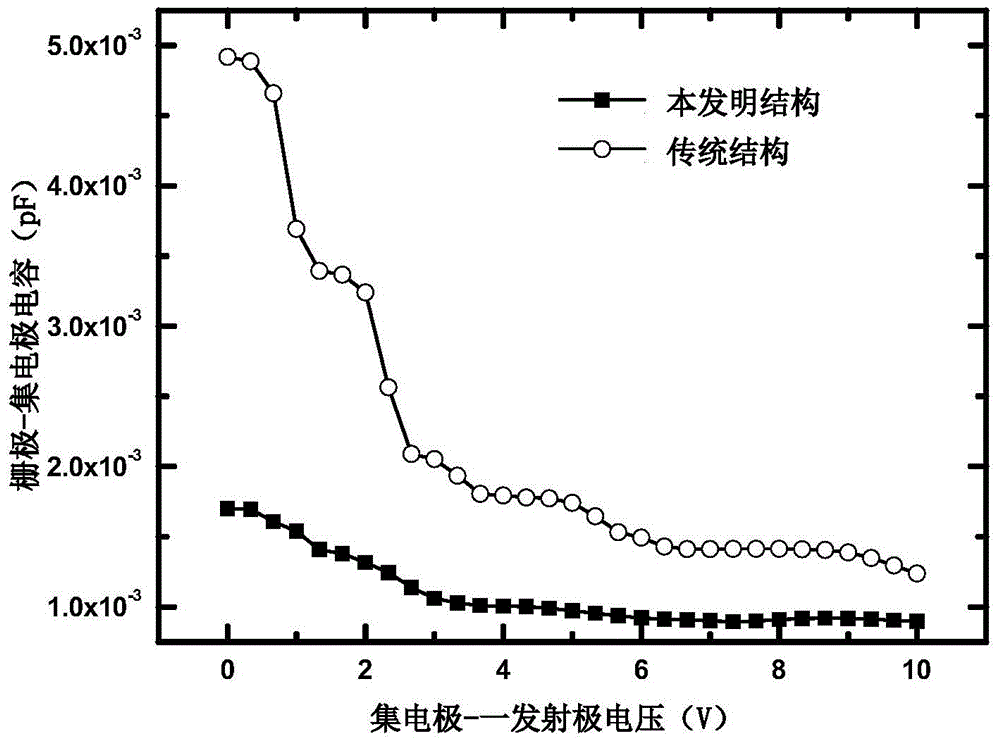

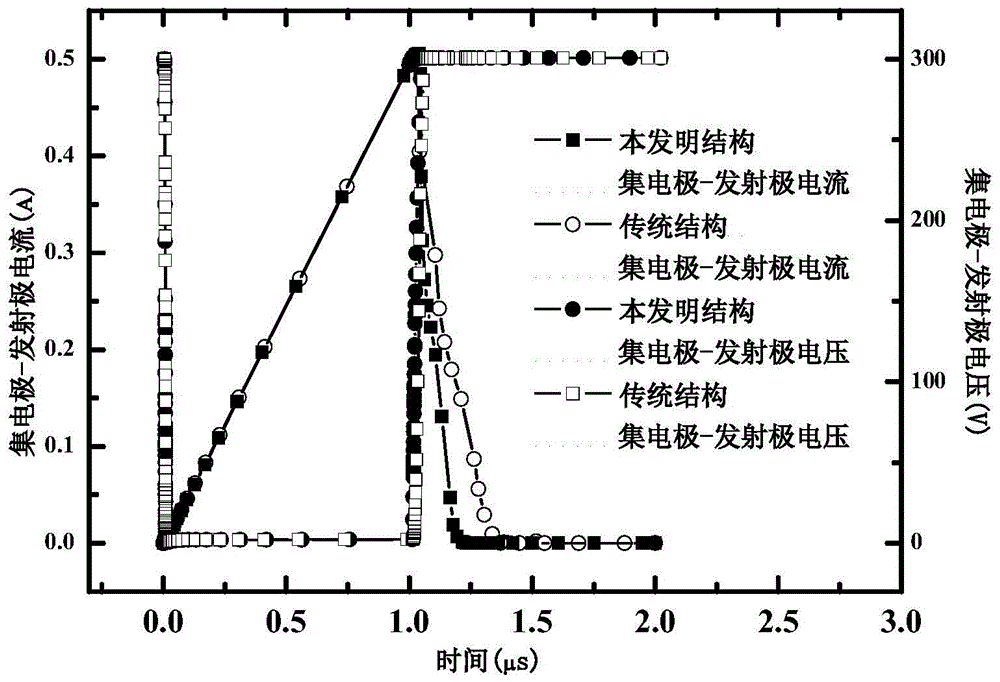

[0021] Combine below figure 2 , the present invention is described in detail, a lateral trench insulated gate bipolar transistor, comprising: a P-type substrate 1, a buried oxide layer 2 is arranged on the P-type substrate 1, and a N type drift region 3, an oxide layer 9 is provided above the upper surface of the N-type drift region 3, and a polysilicon gate 4, a P-type body region 8 and an N-type buffer layer 12 are provided below the upper surface of the N-type drift region 3, and An emitter region is provided in the P-type body region 8, an emitter aluminum electrode 7 is arranged on the emitter region, a P-type collector region 11 is arranged in the N-type buffer layer 12, and a P-type collector region 11 is arranged on the P-type collector region 11. There is a collector aluminum electrode 10, and the N-type buffer layer 12 and the P-type collector region 11 are located at one side of the N-type drift region 3, and the P-type body region 8 and the emitter region are loca...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More