Phase change memory gate tube and storage unit of phase change memory gate tube

A phase-change memory and strobe technology, which is applied in electrical components, semiconductor devices, electric solid-state devices, etc., can solve the problems of increasing storage unit area, reducing storage density and integration, and increasing power consumption.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

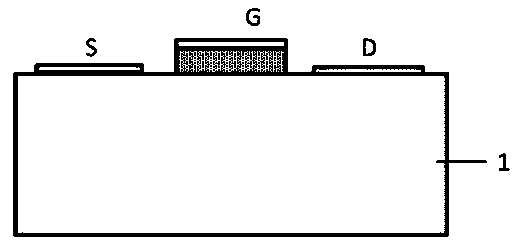

[0037] 1. Using photolithography method on MoS 2 MoS-based 2 MOSFETs;

[0038] 2. In MoS 2 Preparation of 50~300nm thick SiO on MOSFET 2 medium layer;

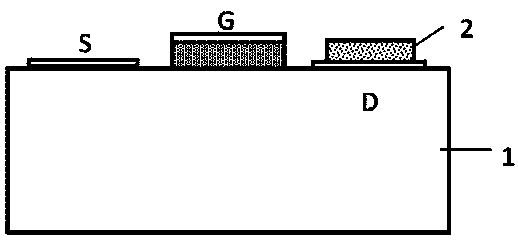

[0039] 3. Using photolithography method on MoS 2 SiO with a diameter of 100nm~1000nm is prepared at the drain end (D end) of the MOSFET 2 media layer graphics;

[0040] 4. Using electron beam lithography and etching technology on the above D-terminal SiO 2 A hole with a diameter of 50nm~500nm is prepared in the dielectric layer, and the bottom end of the hole is connected to the MoS 2 The D terminal of the MOSFET is connected;

[0041] 5. Use ALD technology to fill W in the above hole, after the hole is filled, use CMP to remove the W material outside the hole mouth to form a columnar W pattern;

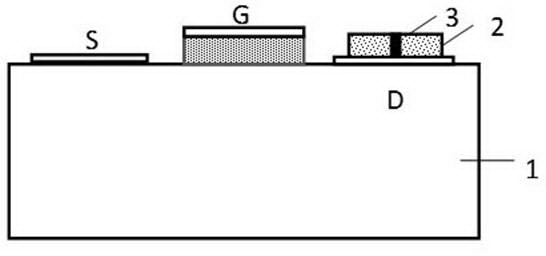

[0042] 6. Use magnetron sputtering to deposit the phase change material GeSbTe and the buffer layer TiN, the thickness of the phase change material is 50~200 nm, and the thickness of TiN is 10~50 nm;

[0043] 7. Using Ph...

Embodiment 2

[0046] 1. Using photolithography method on MoS 2 MoS-based 2 MOSFETs;

[0047] 2. In MoS 2 Preparation of 50~300nm thick SiO on MOSFET 2 medium layer;

[0048] 3. Using photolithography method on MoS 2 SiO with a diameter of 100nm~1000nm is prepared at the drain end (D end) of the MOSFET 2 media layer graphics;

[0049] 4. Using electron beam lithography and etching technology on the above D-terminal SiO 2 A hole with a diameter of 50nm~500nm is prepared in the dielectric layer, and the bottom end of the hole is connected to the MoS 2 The D terminal of the MOSFET is connected;

[0050] 5. Use ALD technology to fill TiN in the above hole. After the hole is filled, use CMP to throw away the TiN material other than the hole mouth to form columnar TiN. Using TiN as the heating electrode can achieve better heating effect and improve the heating electrode. Interface properties with phase change materials;

[0051] 6. Use magnetron sputtering to deposit the phase change ...

Embodiment 3

[0055] 1. Using photolithography method on MoS 2 MoS-based 2 MOSFETs;

[0056] 2. In MoS 2 Preparation of 50~300nm thick SiO on MOSFET 2 medium layer;

[0057] 3. Using photolithography method on MoS 2 SiO with a diameter of 100nm-1000nm is prepared at the drain end (D end) of the MOSFET 2 media layer graphics;

[0058] 4. Using electron beam lithography and etching technology on the above D-terminal SiO 2 A hole with a diameter of 50nm~500nm is prepared in the dielectric layer, and the bottom end of the hole is connected to the MoS 2 The D terminal of the MOSFET is connected;

[0059] 5. Use ALD technology to fill W in the above holes. After the holes are filled, use CMP to remove the W material outside the hole mouth to form a columnar W pattern;

[0060] 6. Use magnetron sputtering to deposit phase change material TiSbTe and buffer layer TiN. The thickness of the phase change material is 50-200 nm, and the thickness of TiN is 10-50 nm; using TiSbTe material can ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Diameter | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More