Transistor forming method

一种晶体管、工艺的技术,应用在半导体制造领域,能够解决晶体管抑制漏电流的能力有限等问题,达到提高载流子迁移率、减少漏电流、厚度均匀的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] As mentioned in the background, in the existing transistors with the stress layer, the carrier mobility in the channel region is limited to increase, so the ability of the transistor to suppress the leakage current is limited.

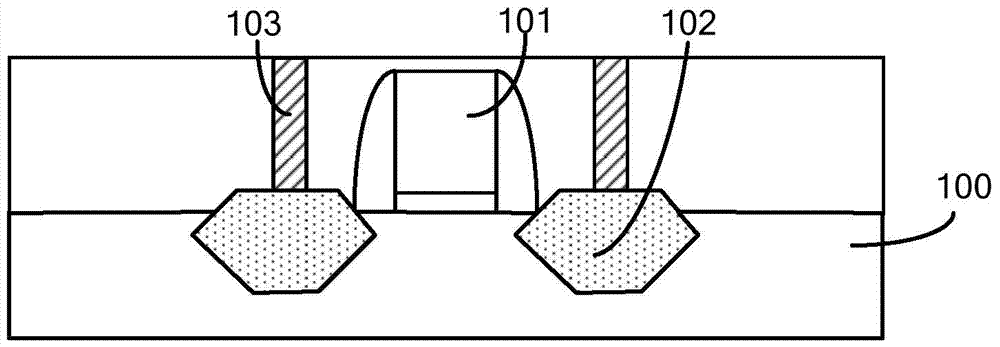

[0033] After research, please continue to refer to figure 1 , the material of the stress layer 102 has a lattice structure, so there are lattice gaps in the stress layer 102 . Especially for NMOS transistors, the material of the stress layer 102 is silicon carbide, and the lattice constant of the silicon carbide is small, that is, the stress layer 102 has a small lattice size and a large lattice gap. The larger lattice gap will trap N-type or P-type dopant ions in the source region or the drain region, resulting in a reduction in the activation amount of the dopant ions after the dopant ions in the source region and the drain region are activated. When the doping ions activated by the source region or the drain region decrease, the resistance of ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| energy | aaaaa | aaaaa |

| doping level | aaaaa | aaaaa |

| energy | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com