Nanowire high-electron-mobility transistor integrating nonpolar GaN and preparation method thereof

A technology with high electron mobility and nanowires, which is applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve problems such as uneven arrangement of nanowires, low yield, and disorder, and achieve uncontrollability and disorder, optimize the process method, and simplify the effect of process steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

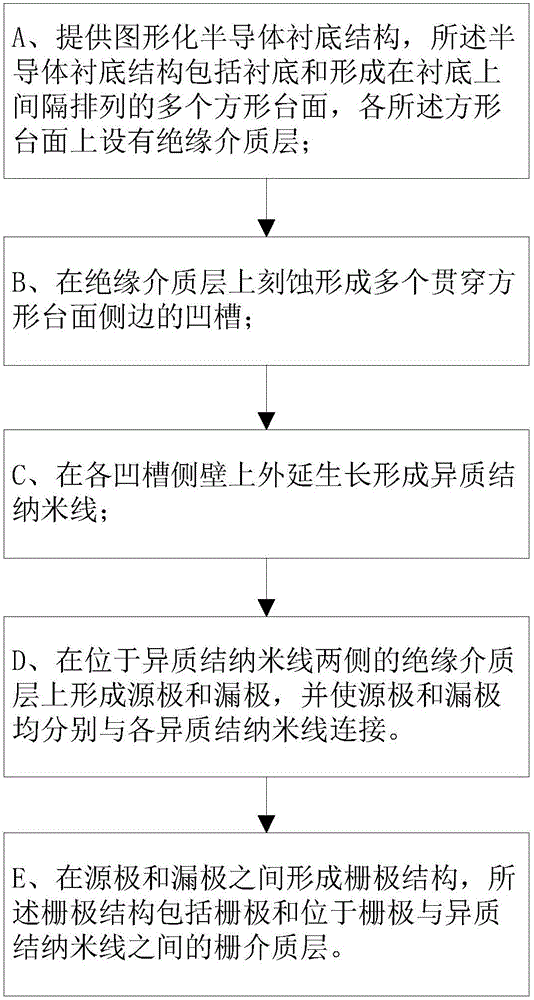

[0042] reference image 3 , The preparation method of integrated non-polar GaN nanowire high electron mobility transistor includes the following steps:

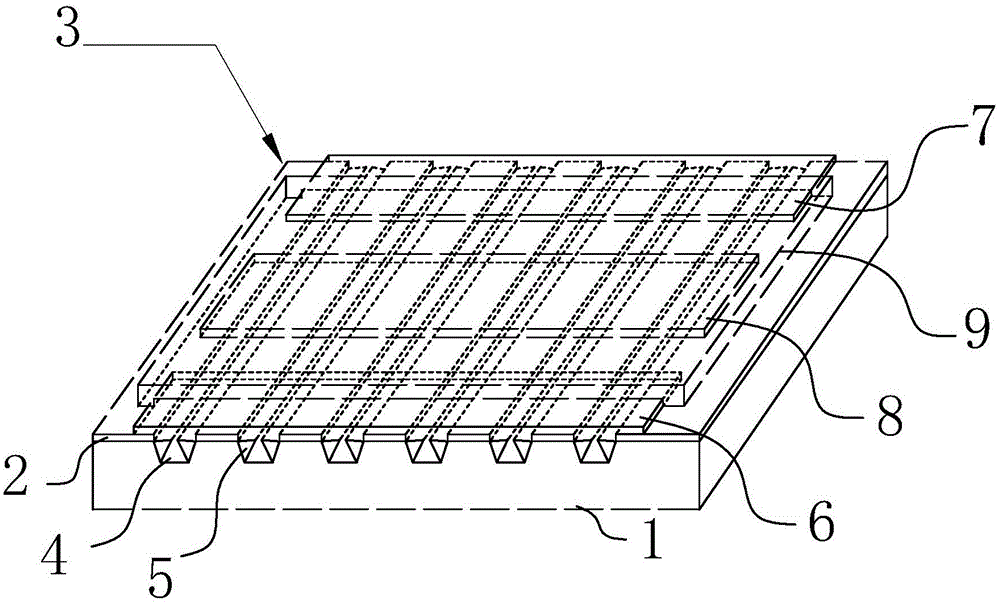

[0043] A. Provide a patterned semiconductor substrate 1 structure. The semiconductor substrate 1 structure includes a substrate 1 and a plurality of square mesa 3 arranged on the substrate 1 at intervals, and each square mesa 3 is provided with an insulating dielectric layer 2;

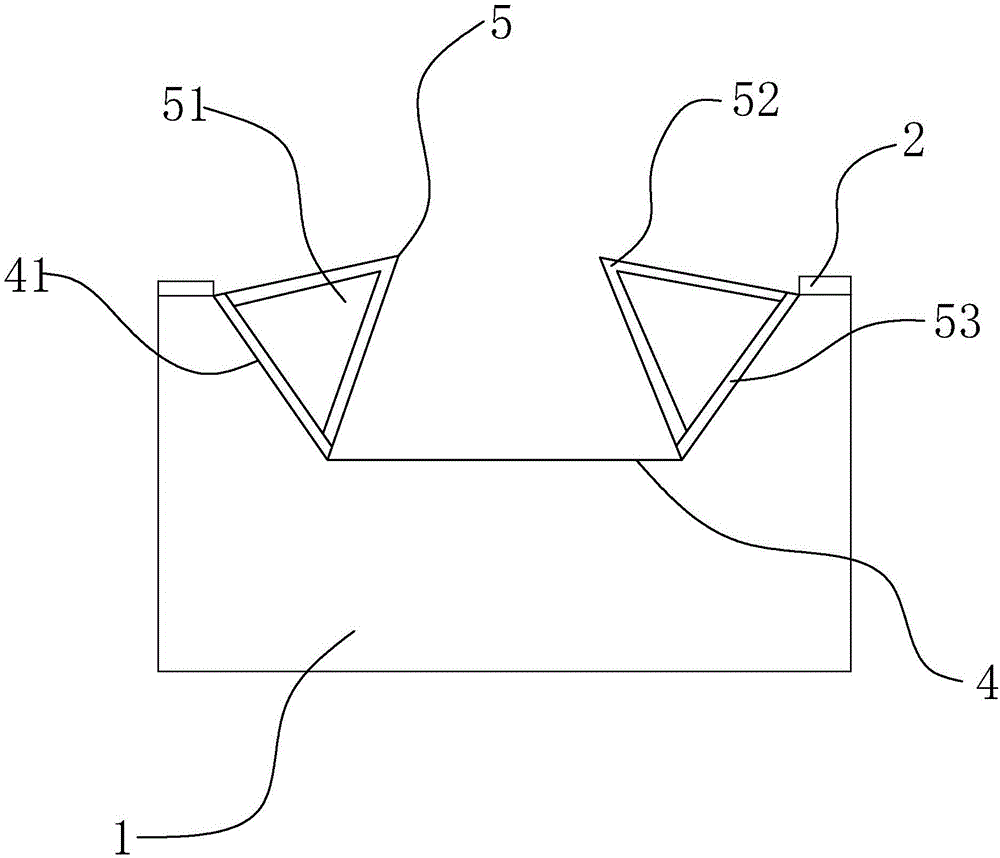

[0044] B. Etching on the insulating dielectric layer 2 to form a plurality of grooves 4 penetrating the sides of the square mesa 3;

[0045] C. Epitaxially grow heterojunction nanowires 5 on the sidewalls 41 of each groove 4;

[0046] D. A source 6 and a drain 7 are formed on the insulating dielectric layer 2 located on both sides of the heterojunction nanowire 5, and the source 6 and the drain 7 are respectively connected to each heterojunction nanowire 5;

[0047] E. A gate 8 structure is formed between the source 6 and the drain 7. The gate 8 structure inc...

Embodiment 1

[0056] Example 1, combined reference Figure 1 ~ Figure 3 Step A is performed to provide a structure of a semiconductor substrate 1. The structure of the semiconductor substrate 1 includes a substrate 1 and a plurality of square mesa 3 arranged on the substrate 1 at intervals, and each square mesa 3 is provided with an insulating medium Layer 2. The material of the substrate 1 is monocrystalline silicon; the material of the insulating dielectric layer 2 on the substrate 1 is a silicon dioxide layer or silicon nitride, but it is not limited to these two dielectric layers, and may be well-known to those skilled in the art Other dielectric layers. A square mesa 3 is formed on the surface of the semiconductor substrate 1. The square mesa 3 has a length of 100um and a height of 3um. The semiconductor substrate 1 is patterned, and an array of rectangular grooves 4 are formed on the square mesa 3. The rectangular grooves 4 forming the array include: coating a photoresist layer on t...

Embodiment 2

[0060] Example 2, combined reference Figure 1 ~ Figure 3 , A structure of a semiconductor substrate 1 is provided. The structure of the semiconductor substrate 1 includes a substrate 1 and a plurality of square mesa 3 formed on the substrate 1 arranged at intervals, and each square mesa 3 is provided with an insulating dielectric layer 2. The material of the substrate 1 is monocrystalline silicon, and the material of the insulating dielectric layer 2 on the substrate 1 is silicon dioxide layer or silicon nitride, but it is not limited to these two dielectric layers, and can be those skilled in the art. Other known dielectric layers. The square mesa 3 on the surface of the semiconductor substrate 1 has a length of 150um and a height of 3um. The semiconductor substrate 1 is patterned to form an array of rectangular grooves 4. The rectangular grooves 4 forming the array include: coating a photoresist layer on the surface of the silicon dioxide layer; defining the pattern of the...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Horizontal size | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More