A 3D memory chip

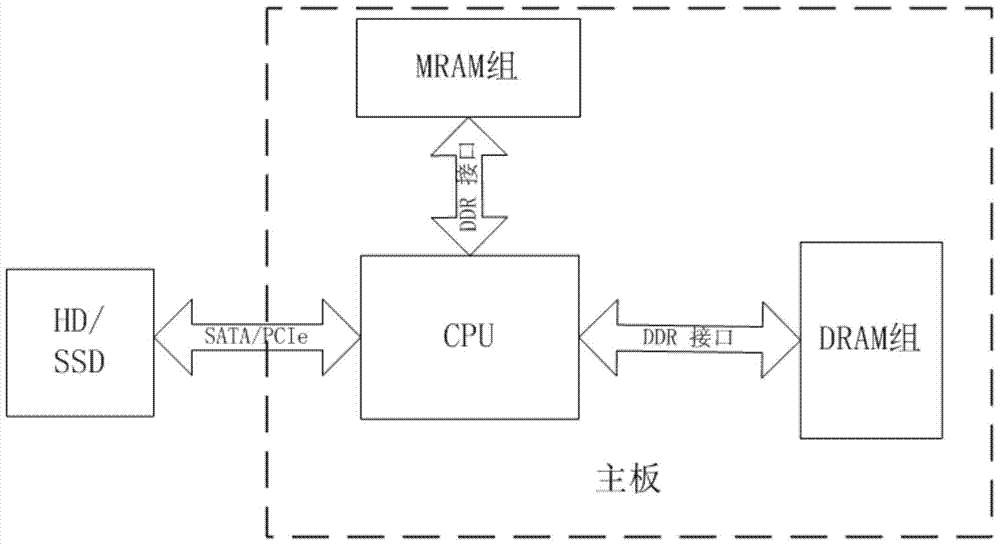

A memory chip and chip technology, applied in information storage, static memory, digital memory information, etc., can solve the problems that hinder the development of portability and miniaturization of smart devices, do not support memory interface protocols, and increase the difficulty of motherboard design. Achieve the effect of saving motherboard area, simplifying motherboard design, and simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

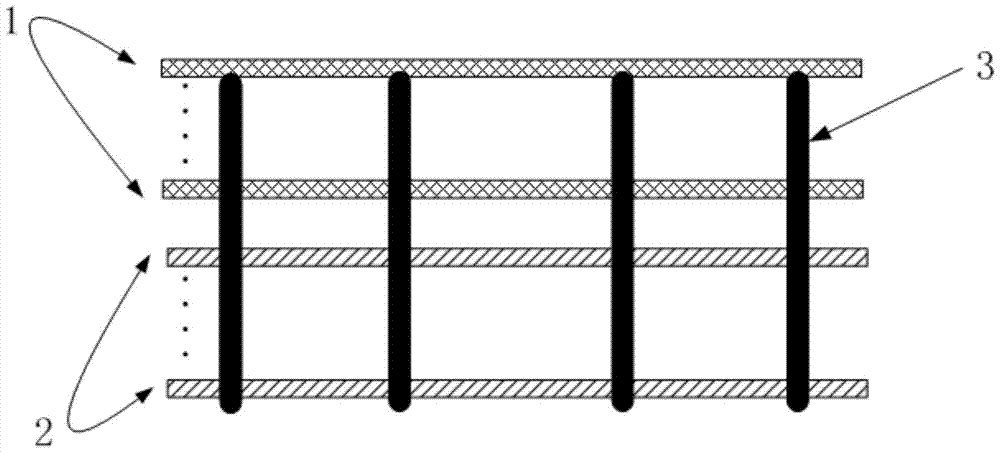

[0033] The design idea of the present invention is based on 3D-SIC technology to use MRAM and DRAM in combination to form a memory chip with a 3D structure. In this embodiment, the combination of a 32-layer MRAM chip and a 32-layer DRAM chip is used as an example to illustrate the present invention. Detailed description.

[0034] The combined structure of MRAM and DRAM such as figure 2 As shown, the 32-layer MRAM chip 1 (2 layers are shown in the figure, and the dotted lines indicate the remaining unshown layers) and the 32-layer DRAM chip 2 (the 2 layers are shown in the figure, and the dotted lines indicate the remaining unshown layers) Each layer) is vertically stacked, and the DRAM chip 2 is located below the MRAM chip 1 . Each MRAM chip 1 and DRAM chip 2 adopts the DDR DRAM interface standard, and through silicon vias 3, the same defined lead pins in each MRAM chip 1 and DRAM chip 2 are connected in series to their corresponding package pins (not shown in the figure)....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More