Radiation-resistant double interlock memory cell for dynamic voltage adjustment system

A dynamic voltage adjustment, storage unit technology, applied in static memory, information storage, digital memory information, etc., can solve the problems of DICE type storage unit limitation, data loss, voltage increase, etc., to optimize delay and power consumption, reduce Soft error rate, the effect of enhancing stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

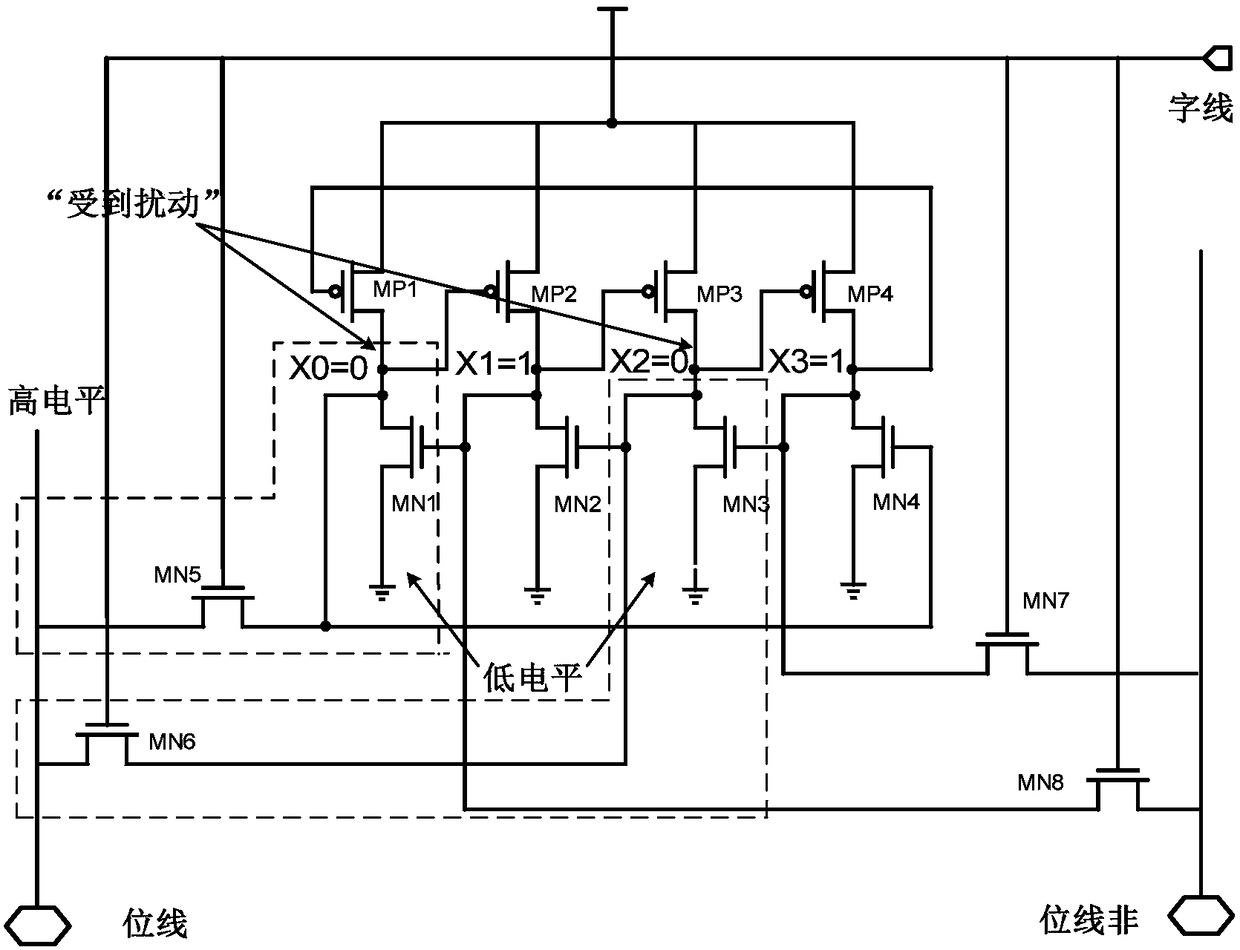

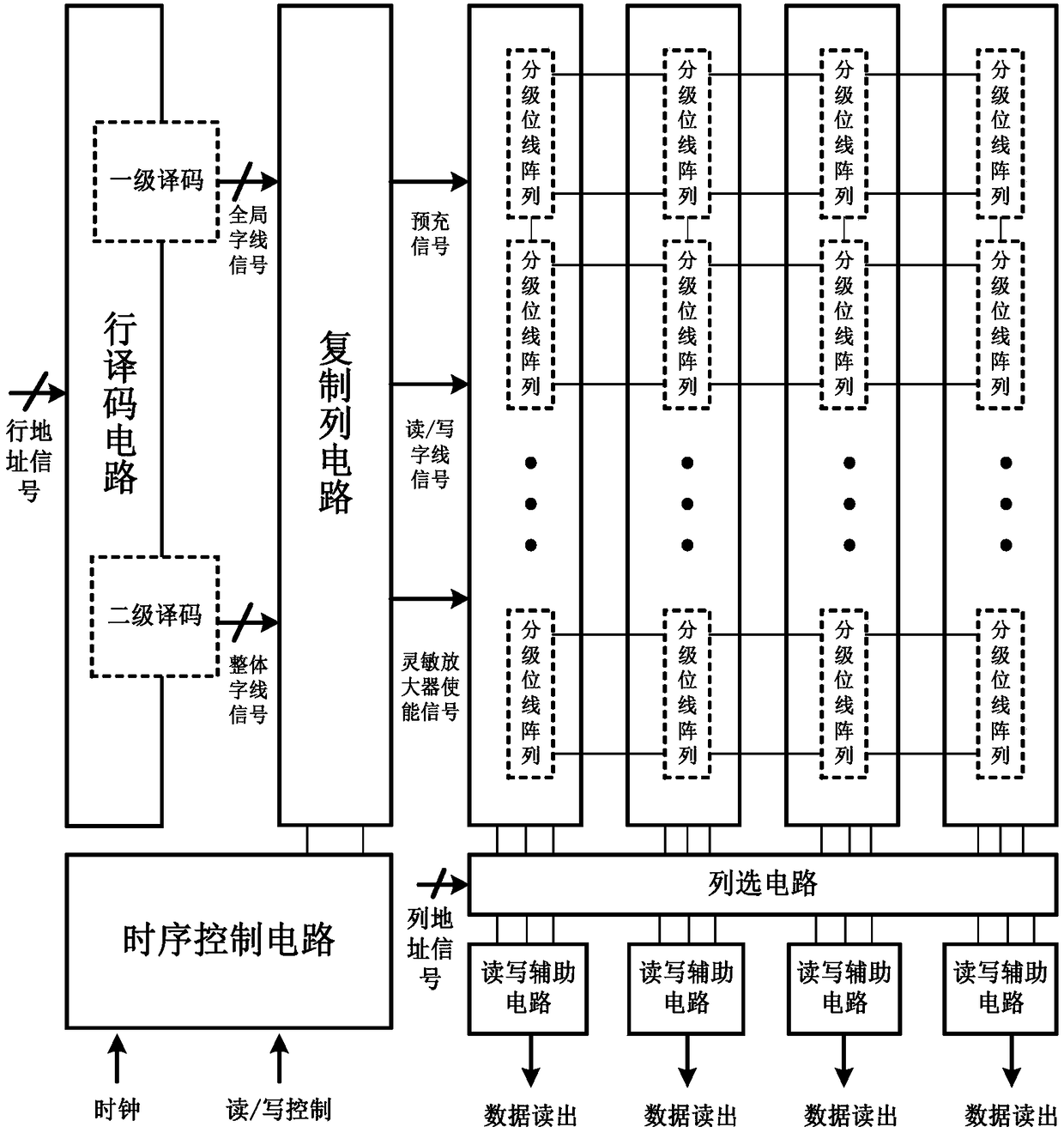

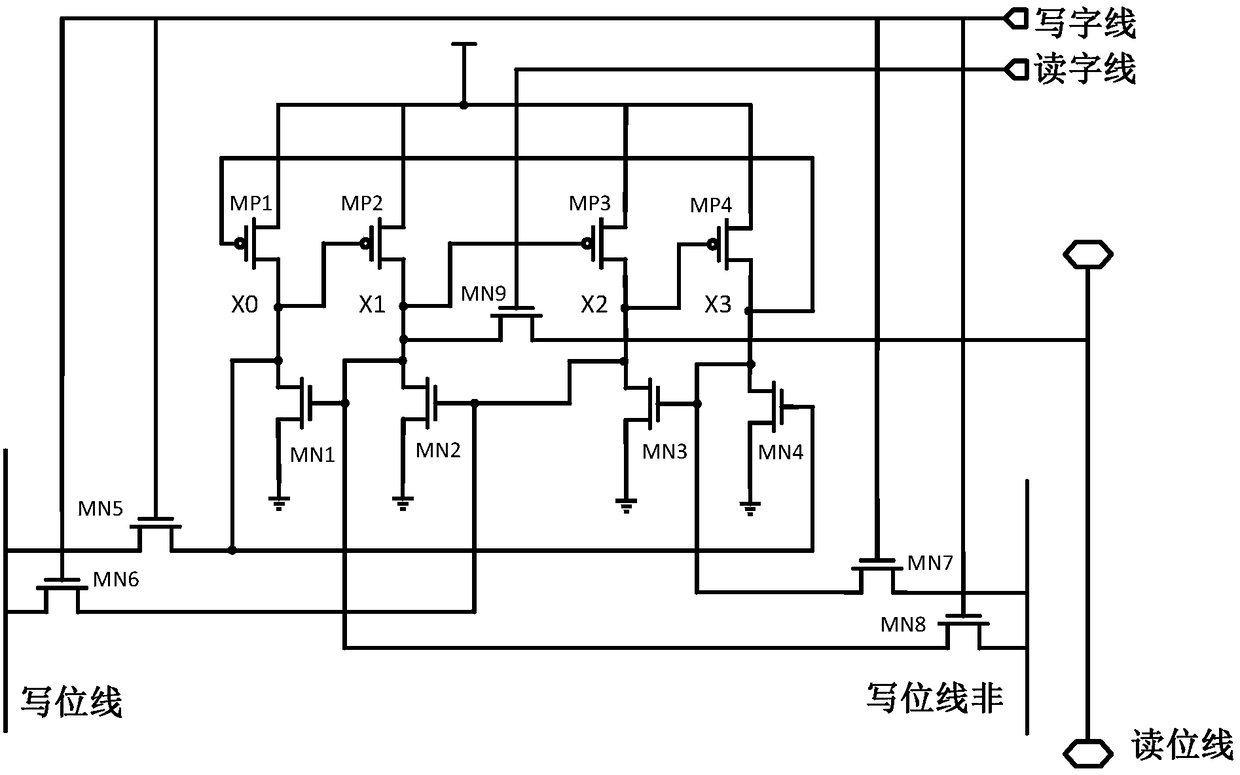

[0025] see figure 2 As shown, the overall circuit structure diagram of the SRAM of the embodiment of the present invention includes: row / column decoding circuit; SRAM storage cell array; read and write auxiliary circuit; copy column circuit; timing control circuit; wherein, row / column decoding The circuit selects the corresponding memory cell through the address signal, and at the same time, the timing control circuit starts to perform virtual read / write operations on the replicated column, generates a pre-fill signal and a word line pulse signal of a suitable width, and a sense amplifier turn-on signal, and These signals are sent to the SRAM memory array for actual read / write operations. Take the read operation as an example, assuming that the stored data of the selected cell is 0 at this time, the read word line signal comes, the read word line of the selected cell becomes high level, and the read bit line starts to discharge. Usually, the sensitive amplifier in the read-w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More