Passivation method of semiconductor device and semiconductor device

A semiconductor and device technology, applied in the field of semiconductor devices, can solve problems such as catastrophic failure and electrical characteristic degradation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

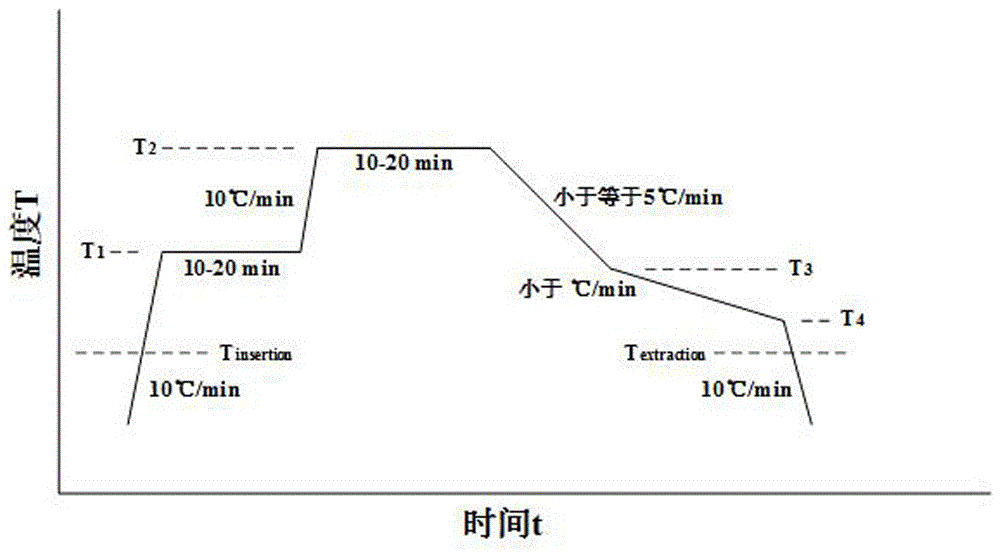

[0019] figure 1 It is the temperature-time curve diagram of typical glass passivation layer formation in the prior art, for example: the patent CN1183582C of the People's Republic of China on January 5, 2005, for a specific glass component, the DTA melting curve of glass. It can be seen that from the temperature T after the melting (glass forming) step 2 To the starting point temperature T of the annealing step 3 , the cooling rate (temperature-time gradient) is 5°C / min, the cooling rate of the annealing step is 2˚C / min, followed by the end point temperature T of the annealing step 4 To the end point temperature T of the annealing step 4 Below 25°C, the cooling rate is converted to about 10°C / min.

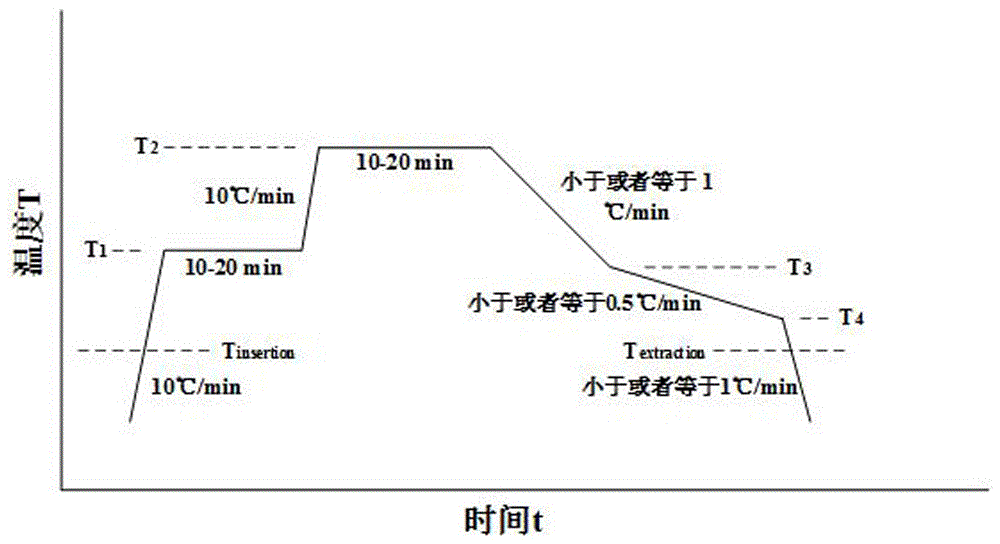

[0020] Regarding the formation of lead oxide silicate passivated glass, the specific implementation of this proposal is as follows: In the glass melting step (in an atmosphere of nitrogen or nitrogen and oxygen at 820˚C, 15-30 minutes) T 2 The subsequent cooling rate is 1°C / min...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More