Radiation-resistant pip type ono antifuse structure and cmos process integration method

An anti-fuse, anti-radiation technology, applied in the direction of semiconductor/solid-state device components, semiconductor devices, electrical components, etc., can solve the problems affecting the integration of the anti-radiation ONO anti-fuse CMOS process, limiting the integration density of the device process, etc. Achieve the effect of optimizing process integration sequence, enhancing total dose resistance, and improving consistency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The embodiments listed in the present invention are only used to help understand the present invention, and should not be interpreted as limiting the protection scope of the present invention. For those of ordinary skill in the art, they can also Improvements and modifications are made to the present invention, and these improvements and modifications also fall within the protection scope of the claims of the present invention.

[0045] The present invention will be further described below in conjunction with specific examples.

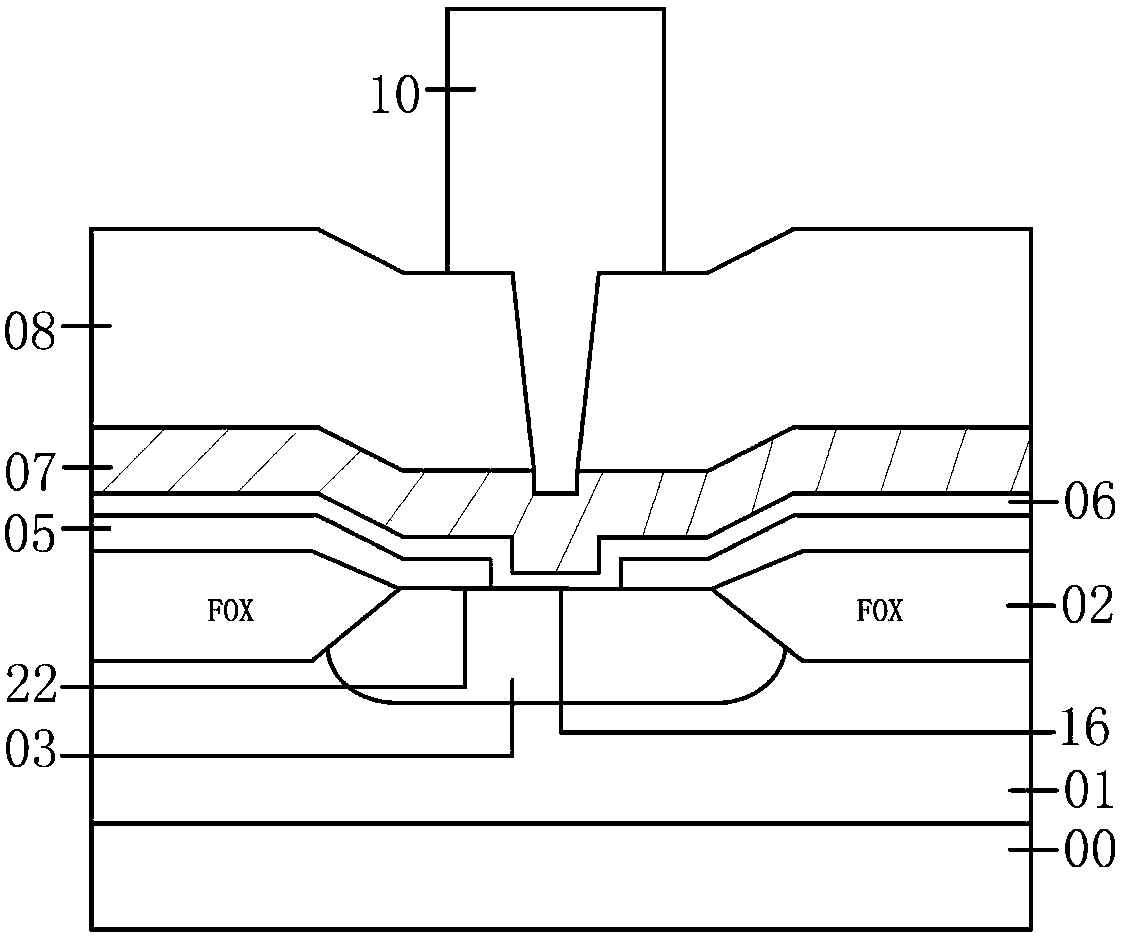

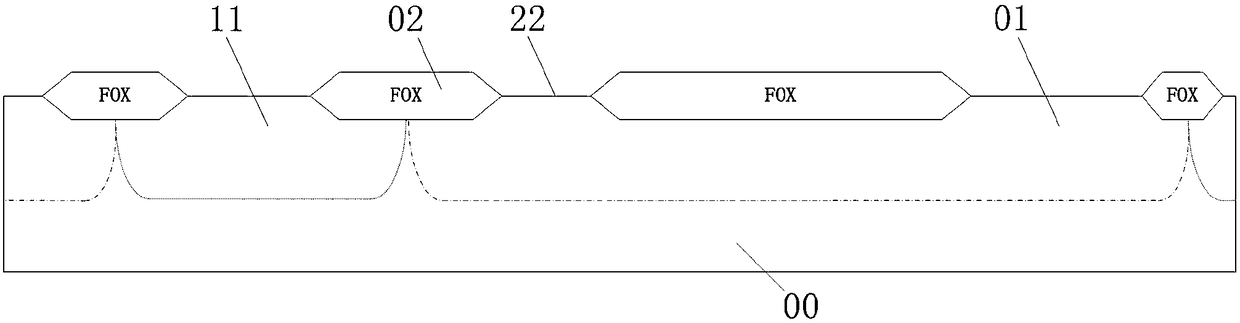

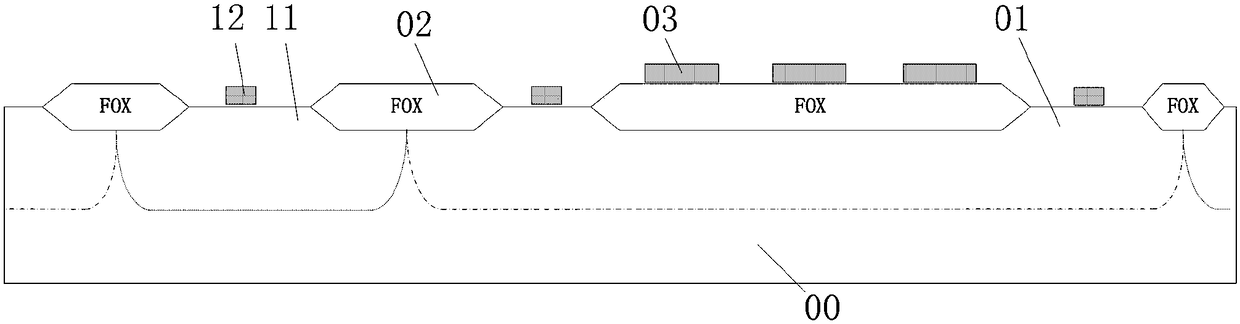

[0046] In order to improve the anti-radiation performance of the unit of the ONO antifuse structure, reduce the area of the integrated unit, optimize the design of the ONO antifuse structure, and improve the integration of the ONO antifuse process, the present invention provides a radiation-resistant PIP type ONO antifuse structure. Such as Figure 11 As shown, the ONO antifuse structure is fabricated on the film layer of the field region 0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More