LDMOS with low conduction resistance and relatively low total gate charge and preparation method for LDMOS

A technology with low on-resistance and preparation process, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve low on-resistance and total gate charge, high LDMOS on-resistance and total gate charge, Low on-resistance and other issues, to achieve low total gate charge, good effect of suppressing high electric field, and low on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

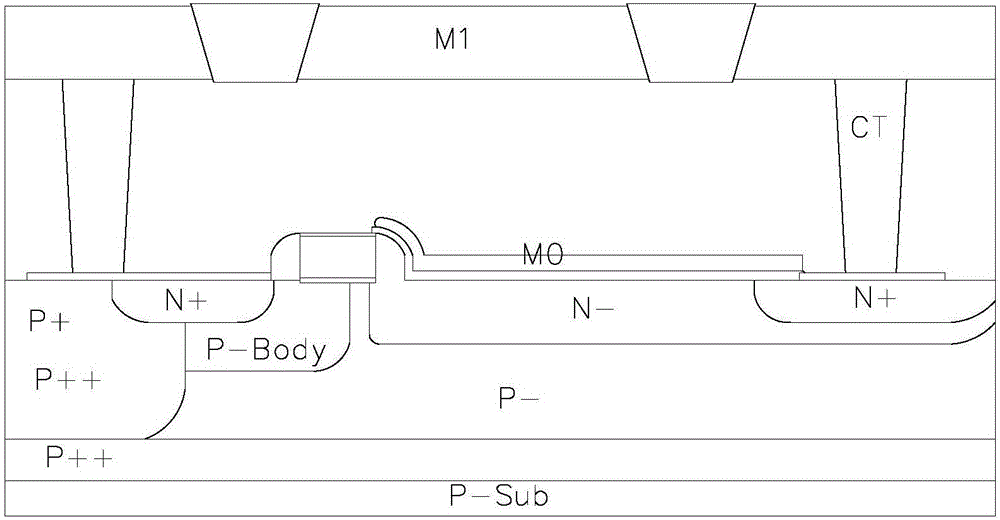

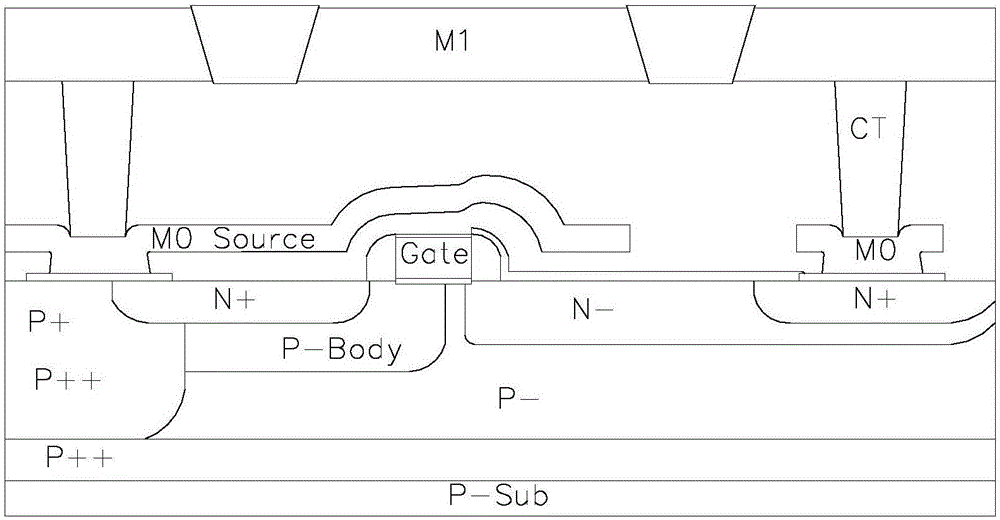

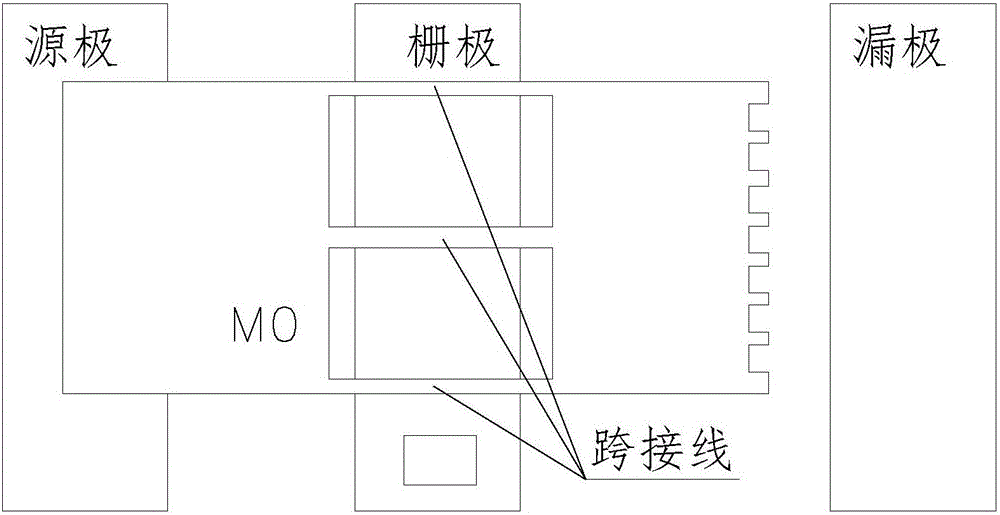

[0034] The present invention resets the layout of the metal shielding layer of the source on the basis of the existing LDMOS structure. join Figure 2 to Figure 7 , the specific structure is as follows:

[0035] The first metal shielding layer M0 of the metal shielding layer spans over the gate, one end of which is connected to the source, and the other end (extended end) extends to the drain but is separated from the drain by a certain distance, so that in the first A coupling capacitance is formed between the metal shielding layer and the oxide or SiN medium of the drain; the thickness of the insulating dielectric layer ILD between the first metal shielding layer and the gate needs to be designed in advance to adjust the size of the coupling capacitance; the metal The distance between the other end of the shielding layer and the gate needs to be designed in advance for adjusting the electric field between the source and drain.

[0036] When necessary, the part of the metal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More