Scalable optical network-on-chip architecture and communication method based on double-layer layout

A network structure and layout technology, applied in the field of communication, can solve the problems of insufficient waveguide layout in the optical switching unit, increase in the average number of communication hops, and large network cross loss, etc., to achieve high bandwidth, high energy utilization, and low network loss Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

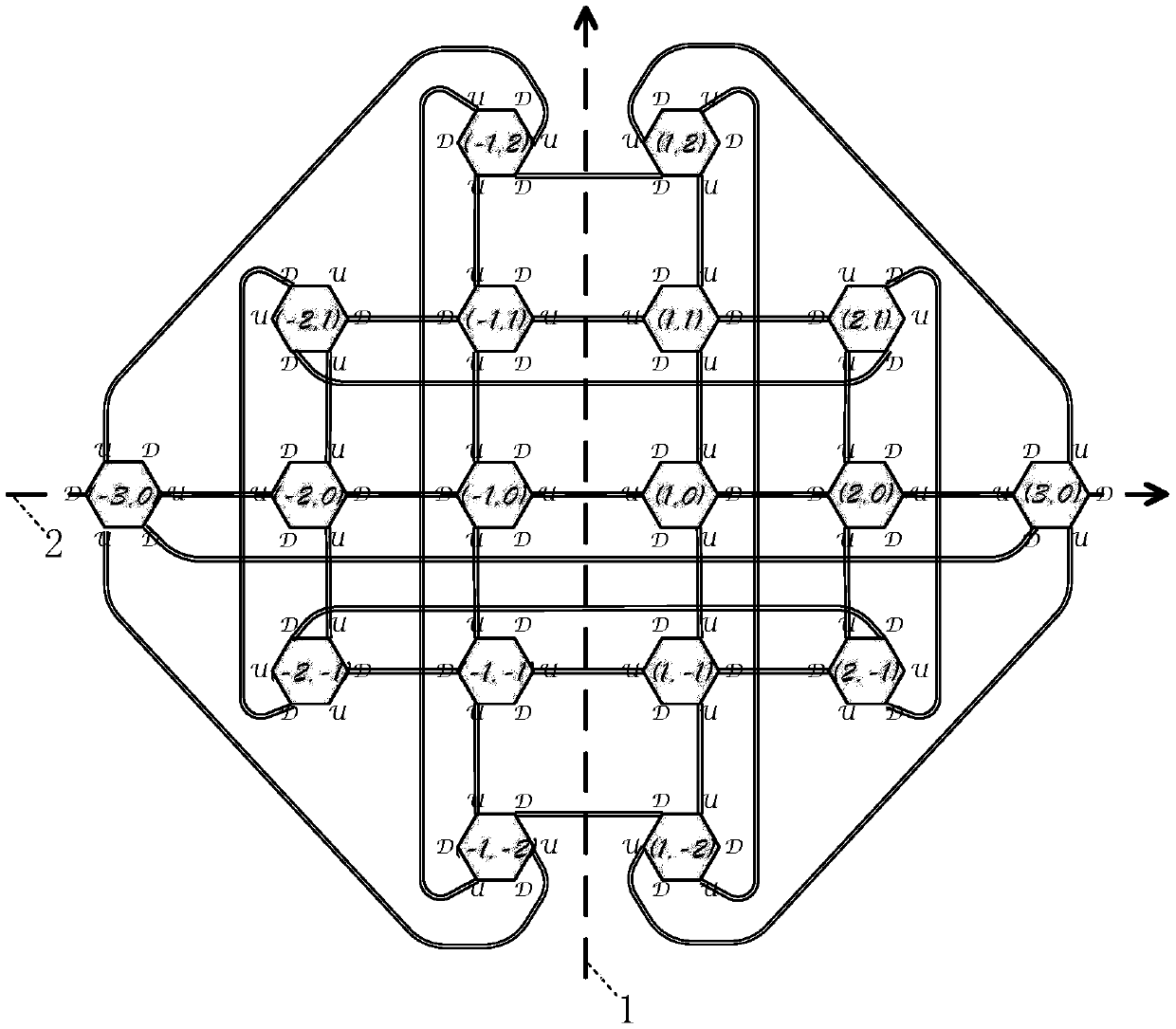

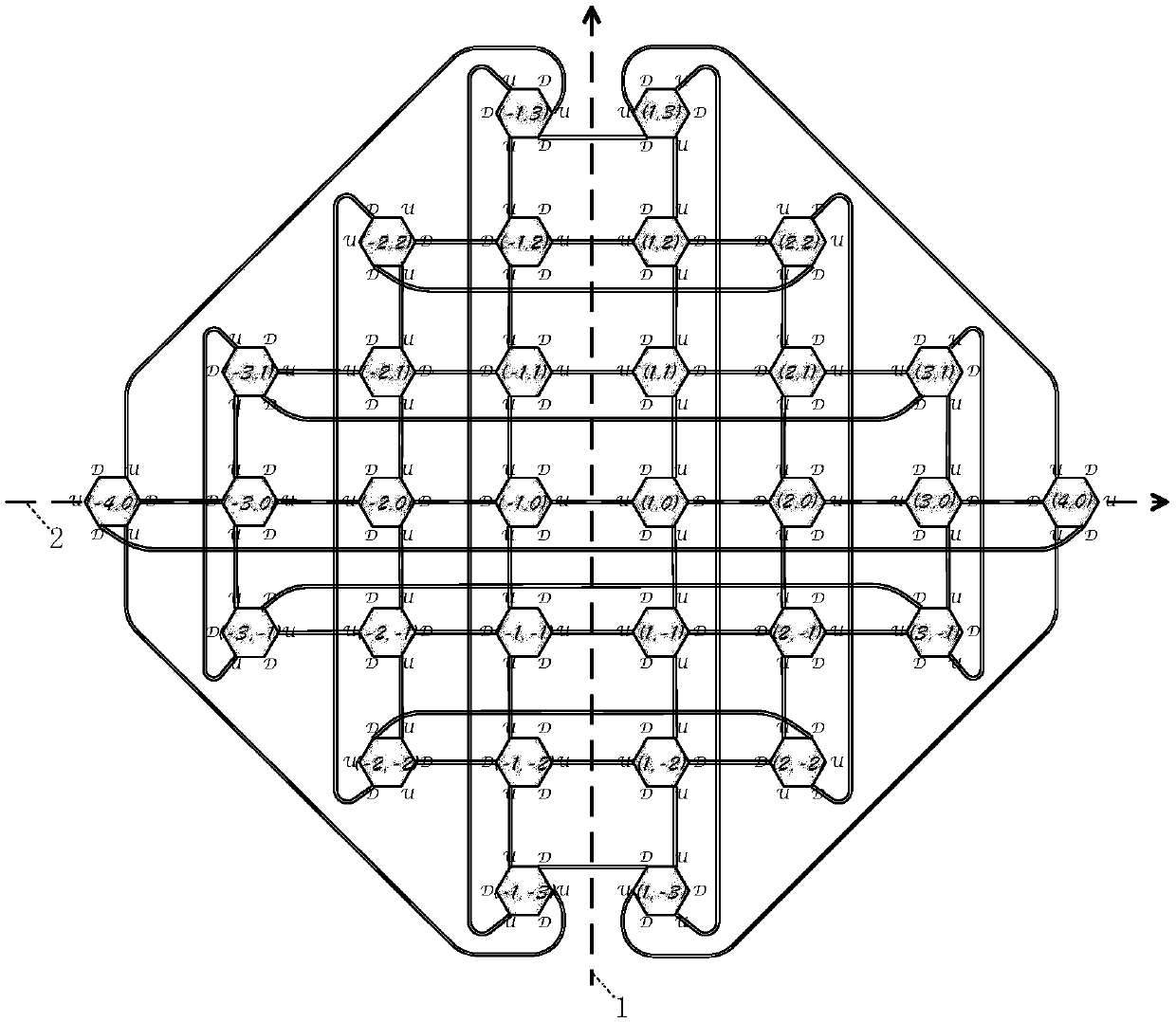

[0039] The present invention will be described in further detail below in conjunction with the accompanying drawings.

[0040] The device of the present invention includes upper and lower silicon substrates and 2N etched on the upper and lower silicon substrates. 2 A six-port optical router, 4N 2 Root optical waveguide, 4N connected by six-port optical router and optical waveguide 2 Intellectual property IP cores, where N is a positive integer greater than or equal to 3.

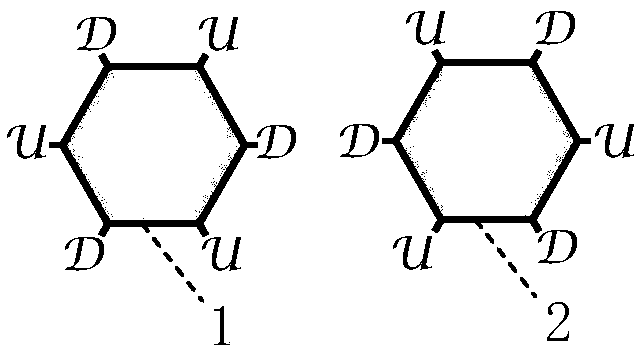

[0041] 2N2 A six-port optical router is composed of two kinds of mirror-symmetrical staggered six-port optical routers arranged alternately. Two local ports in each six-port optical router are respectively connected to two intellectual property IP cores, and the remaining four are interconnected. The connection port is connected with other six-port optical routers through waveguides to realize the reception and forwarding of optical signals in the network.

[0042] Two kinds of staggered-layer six-port op...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More