Grooved gate enhanced GaN transistor device based on nano channel

An enhanced transistor technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of large on-resistance of devices, short gate length, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0028] Embodiment 1: A groove-gate enhanced GaN transistor device based on a single nanochannel.

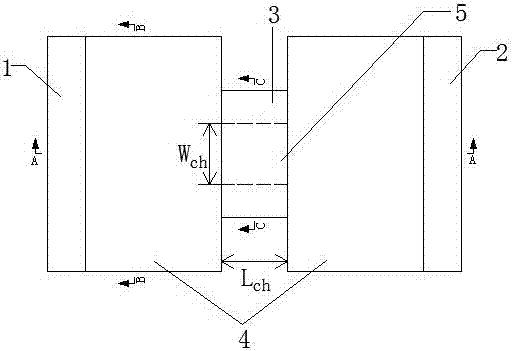

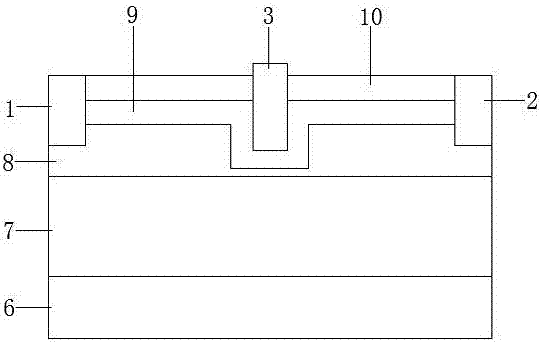

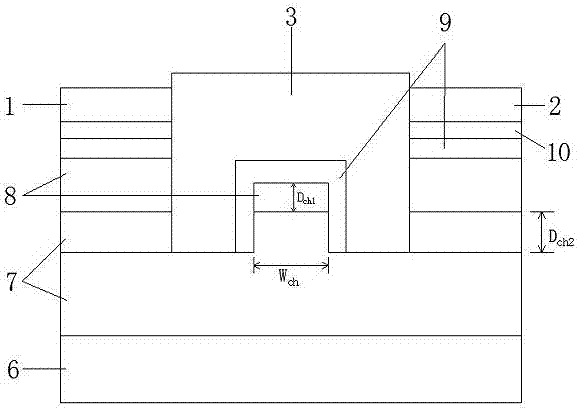

[0029] figure 1 It is a top view of an overall structure of an embodiment of the present invention, figure 2 , image 3 with Figure 4 respectively figure 1 Sectional views of plane A-A, plane B-B and plane C-C. The groove gate enhanced GaN transistor device based on the single nanochannel 5 in this embodiment includes a substrate layer 6, a GaN buffer layer 7, an AlGaN barrier layer 8, a gate dielectric layer 9, a passivation layer 10 and a source electrode from bottom to top 1. Drain electrode 2 and gate electrode 3.

[0030] The material used for the substrate layer 6 is sapphire, SiC or GaN.

[0031] Above the substrate layer 6 is a GaN buffer layer 7 with a thickness of 0.5-2.5 μm.

[0032] Above the buffer layer is an AlGaN barrier layer 8 with a thickness of 10-20 nm and an Al composition of 15%-30%.

[0033] The AlGaN barrier layer 8 and the GaN buffer layer 7 fo...

Embodiment 2

[0039] Embodiment 2: a groove-gate enhanced GaN transistor device based on a single nanochannel.

[0040] Such as Figure 5 As shown, the groove gate enhanced GaN transistor device based on the single nanochannel 5 of this embodiment has the same structure as that of the first embodiment, but the length L of the nanochannel 5 ch for L ch >Gate length L g .

Embodiment 3

[0041] Embodiment 3: Recessed gate enhanced GaN transistor device based on multi-nanometer channels.

[0042] Such as Image 6 As shown, the groove gate enhanced GaN transistor device based on multiple nanochannels in this embodiment has the same structure as that in Embodiment 1, but the number n of the nanochannels 5 is n>1.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More