Array substrate and preparation method thereof, and touch control display panel

A technology of array substrates and touch wires, which is applied in semiconductor/solid-state device manufacturing, instruments, and electrical digital data processing. light area effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

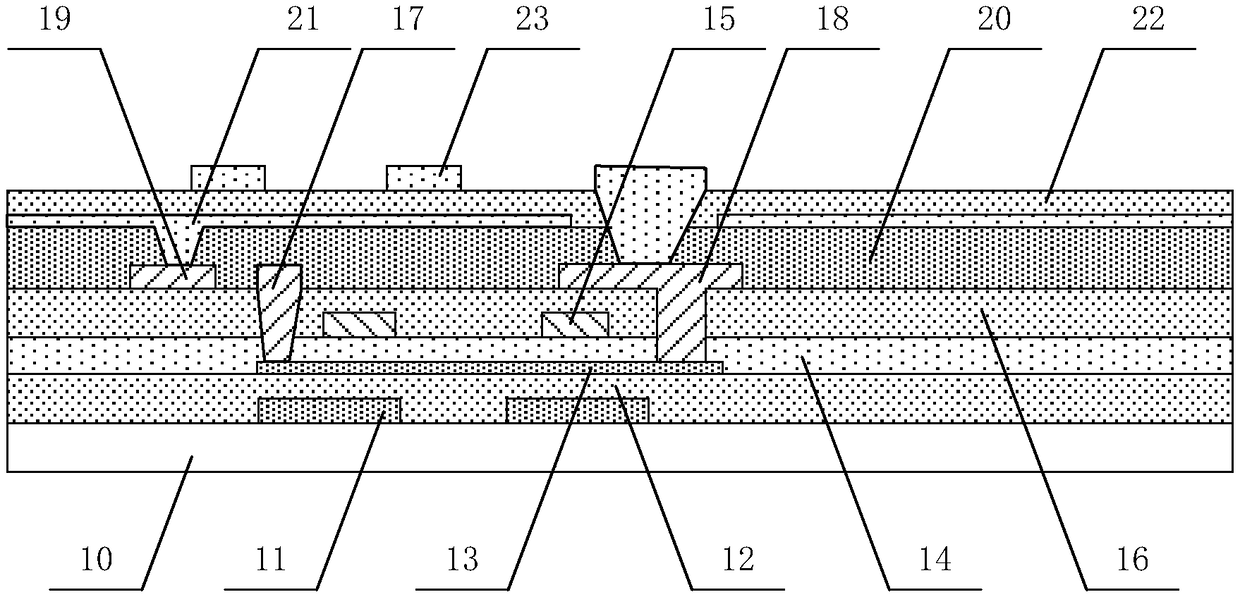

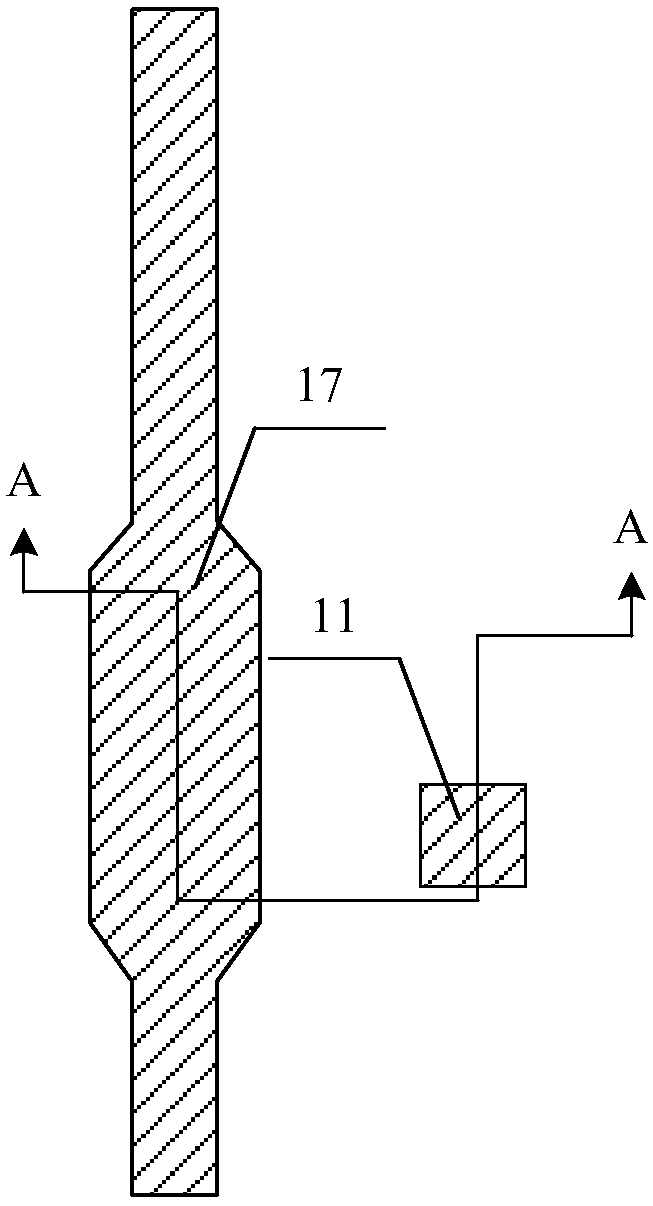

[0073] In this embodiment, an LTPS thin film transistor array substrate with a double gate structure is used to illustrate the technical solution of the embodiment of the present invention. Figure 3-22 It is a schematic diagram of preparing an array substrate according to the first embodiment of the present invention. Among them, the "patterning process" mentioned in this embodiment includes deposition of film layer, coating of photoresist, mask exposure, development, etching, stripping of photoresist, etc., which is an existing mature preparation process. Deposition can use known processes such as sputtering, evaporation, and chemical vapor deposition, coating can use known coating processes, and etching can use known methods, which are not specifically limited here.

[0074] (1) Forming a first electrode and a light-shielding layer pattern on a substrate. Forming the light-shielding layer and the first electrode pattern includes: depositing a first metal film on the substr...

no. 2 example

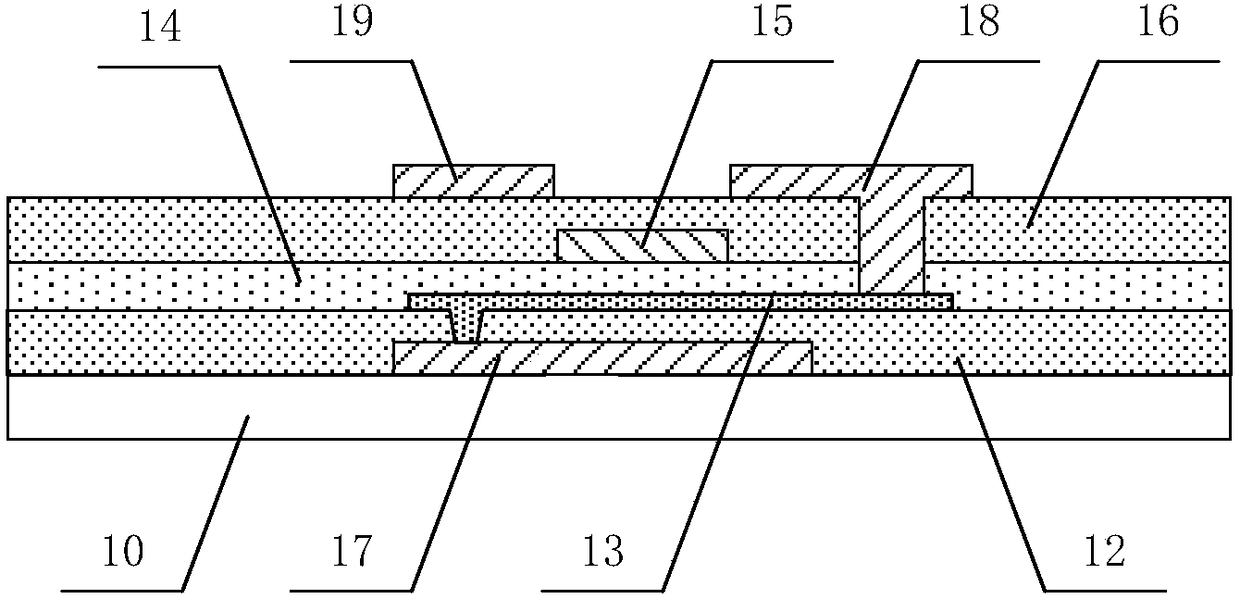

[0101] Figure 23 It is a schematic structural diagram of the second embodiment of the array substrate of the present invention. This embodiment is an extension of the aforementioned first embodiment, and the touch electrodes are disposed above the pixel electrodes. Such as Figure 23 As shown, the array substrate of this embodiment includes: a substrate 10, a light shielding layer 11, a first electrode 17, a buffer layer 12, a U-shaped LTPS active layer 13, a gate insulating layer 14, a gate electrode 15, an interlayer insulating layer 16, The structure of the second electrode 18 and the touch line 19 is the same as that of the aforementioned first embodiment. The fourth via hole connected to the pixel electrode 23, the pixel electrode 23 is arranged on the passivation layer 22, and connected to the second electrode 18 through the fourth via hole, the flat layer 20 covers the pixel electrode 23, and a touch line 19 is opened on it The third via hole connected to the touch ...

no. 3 example

[0104] Although the foregoing embodiments are based on the LTPS thin film transistor array substrate with a double-gate structure, based on the technical concept of the foregoing embodiments, the present invention is also applicable to a single-gate structure. For example, the U-shaped LTPS active layer in the foregoing embodiments can be modified into an L-shaped, the vertical end of the L-shaped active layer is arranged on the source electrode (data line), and forms a cross with the gate electrode (gate line), and The horizontal end is parallel to the gate line without intersecting with the gate line, forming an LTPS thin film transistor array substrate with a single gate structure. In this solution, the source electrode can play a shielding role, so the light shielding layer may not be provided.

[0105] In addition, the embodiments of the present invention are also applicable to array substrates with other structures. The LTPS active layer in the foregoing embodiments can...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More