A kind of manufacturing method of igbt chip with compound gate structure containing dummy gate

A manufacturing method and compound gate technology, which are applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., to achieve the effect of shielding mutual interference, retaining low power consumption, and solving high-voltage state voltage drop

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

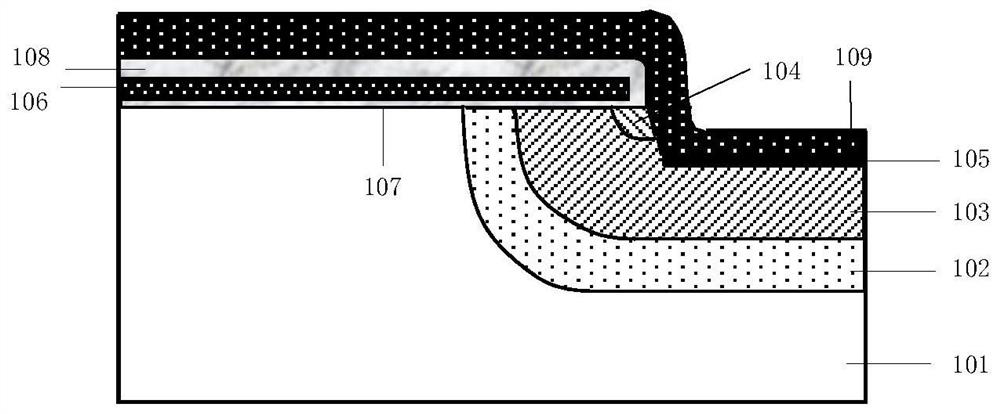

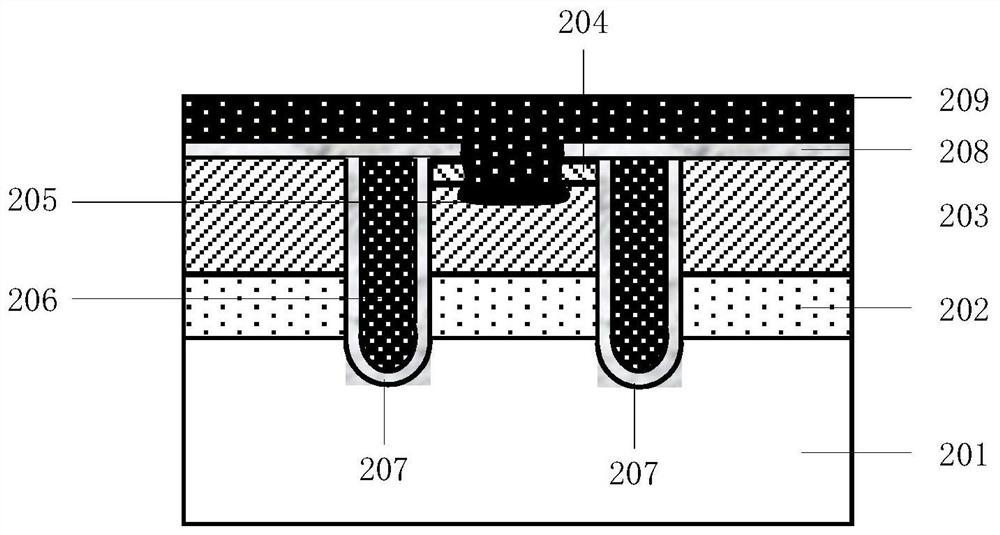

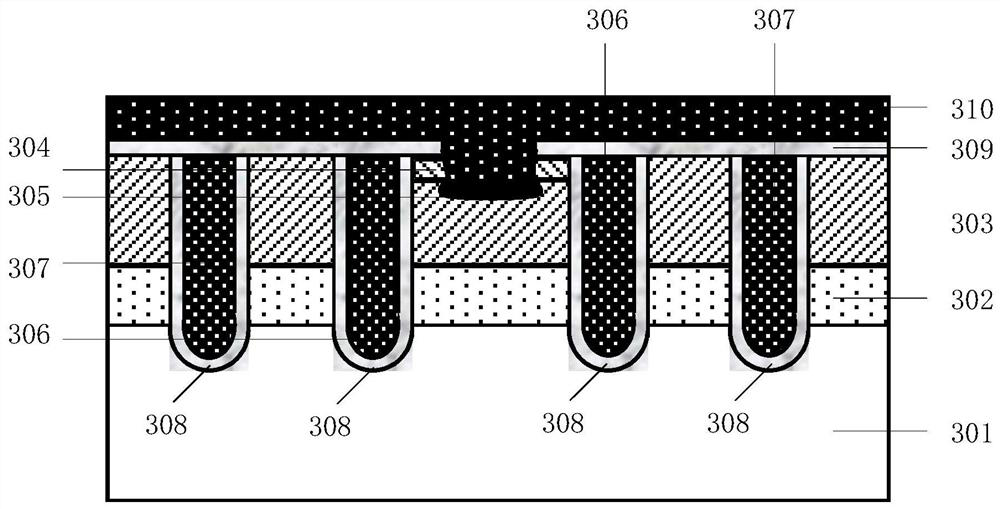

[0048] The implementation of the present invention will be described in detail below in conjunction with the accompanying drawings and examples, so as to fully understand and implement the process of how to apply technical means to solve technical problems and achieve technical effects in the present invention. It should be noted that, as long as there is no conflict, each embodiment and each feature in each embodiment of the present invention can be combined with each other, and the formed technical solutions are all within the protection scope of the present invention.

[0049] In this embodiment, the IGBT chip includes multiple cells, such as Figure 4 As shown, each cell 410 may be a hexagonal cell structure, and a plurality of cells 410 are distributed on the wafer substrate in a honeycomb shape. Moreover, each cell 410 includes a gate region 401 , and trench gate active regions 402 and planar gate active regions 403 located on both sides of the gate region 401 .

[0050...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More