CMOS rear end technology-embedded ferroelectric random memory and preparation method thereof

A technology of random access memory and back-end technology, applied in capacitors, electric solid-state devices, circuits, etc., can solve problems such as difficult to meet, low thermal budget, poor electrical performance of PZT film, etc., achieve low process cost, reduce manufacturing cost, high memory effect of density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0044] Many specific details are set forth in the following description to fully understand the present invention, but based on the current rapid development of CMOS silicon process technology, the present invention can also be implemented in other ways than those described here. The present invention mainly proposes an idea of embedding and integrating a ferroelectric capacitor on a CMOS process line, and its inventive point is not limited to the replacement and change of a certain specific process.

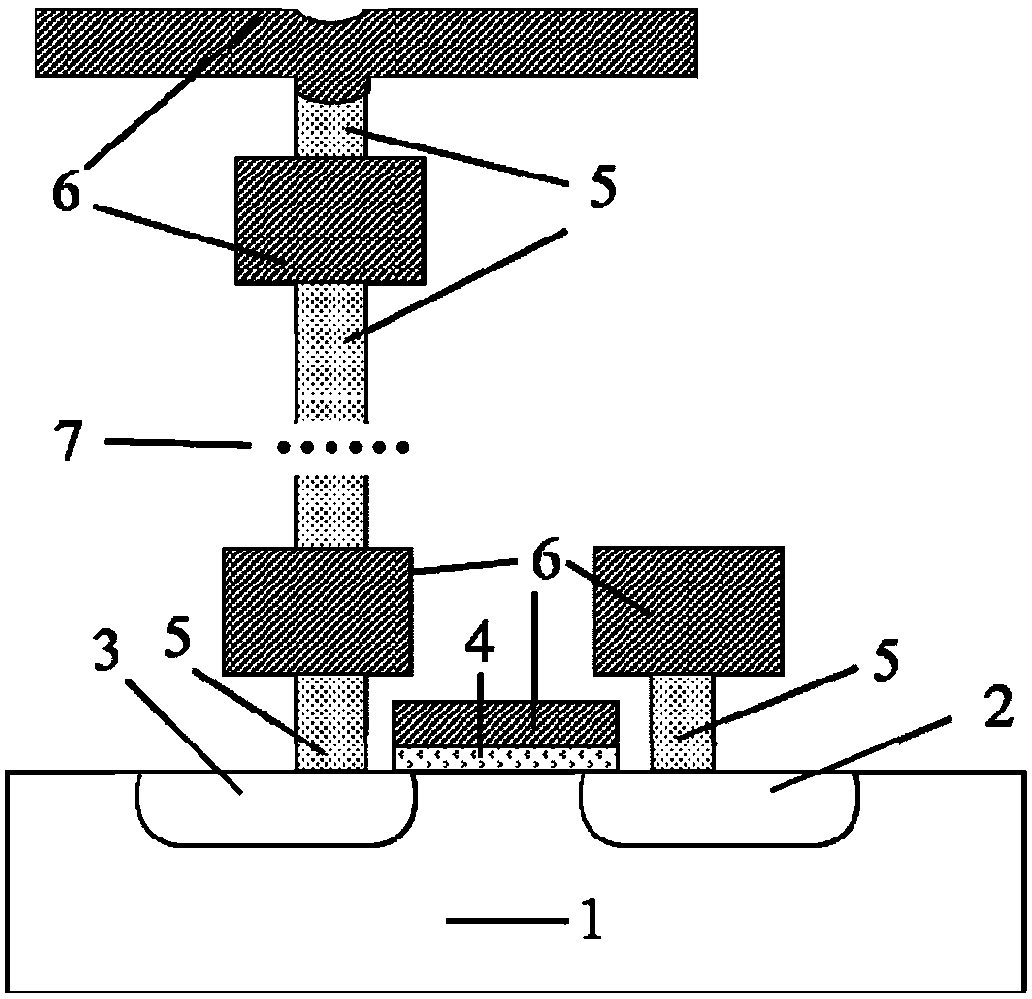

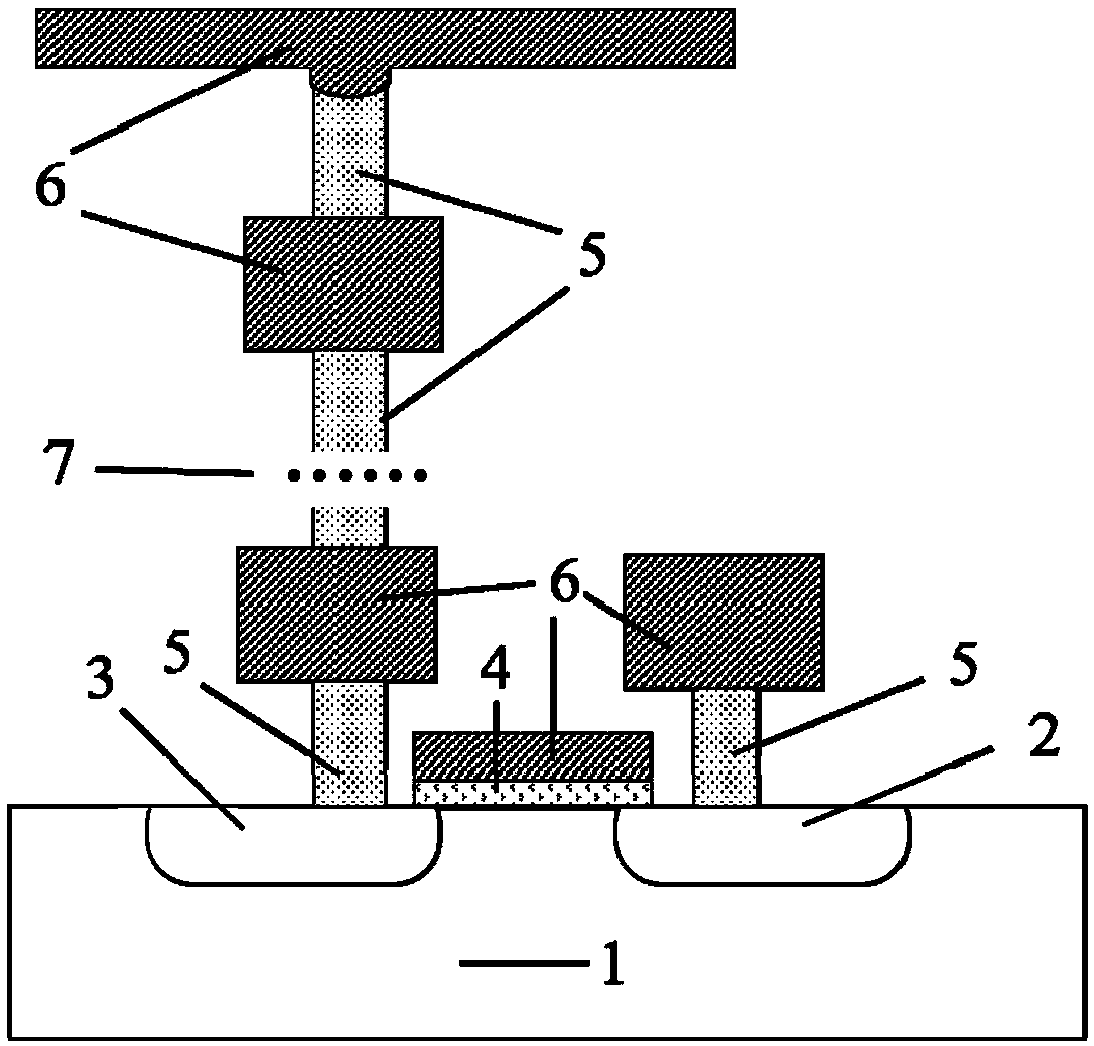

[0045] refer to figure 2 The source region (2), the drain region (3), the gate dielectric layer (4), the through hole (5), and the necessary metal interconnection (6, 7) of the transistor are completed on the traditional CMOS process ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More