Metalized ceramic substrate, substrate manufacturing method and substrate and chip welding method

A technology of metallized ceramics and ceramic substrates, applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve problems such as cracking of chips and metallization layers, failure of power electronic devices, chip shedding, etc., to achieve product Reduced size, high production accuracy, and reduced package thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

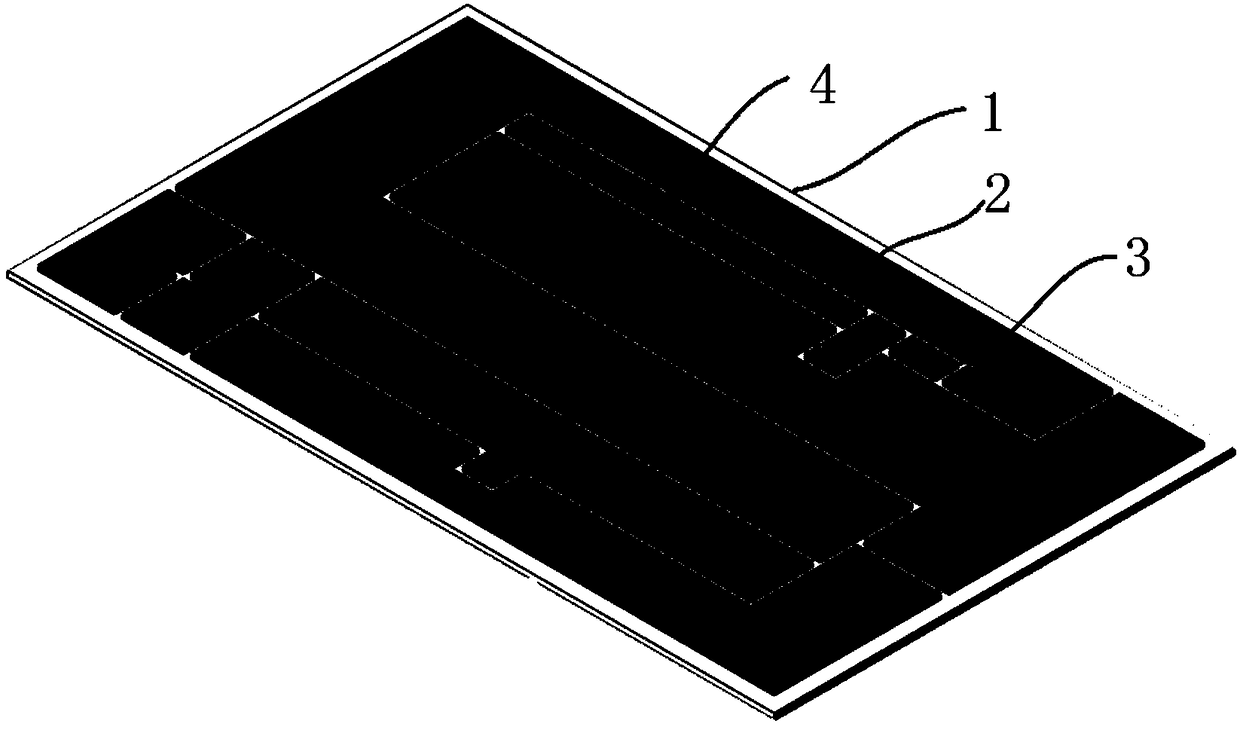

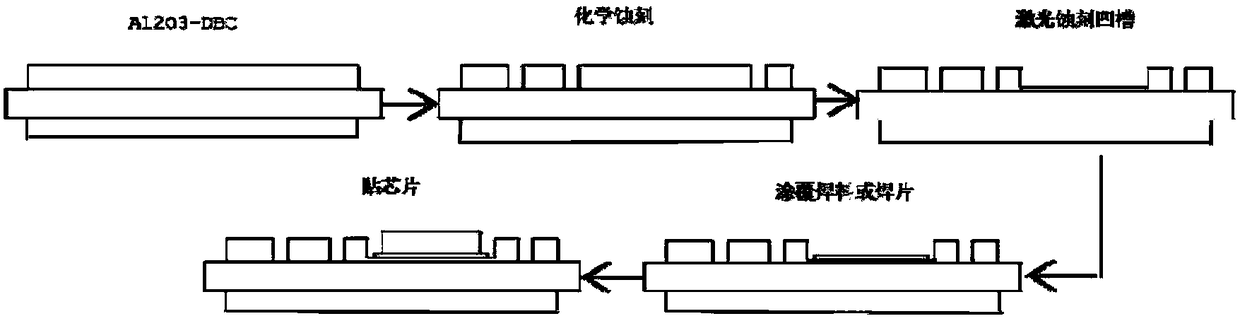

[0048] Such as figure 2 As shown, the Al with chip groove 4 2 O 3 --DBC metallized ceramic substrate and reliable welding method, this method includes the following steps:

[0049] S1, 138mm*190mm*0.38mm (copper sheet specification 134mm*184mm*0.30mm) specification Al 2 O 3 -DBC ceramic substrate, through the traditional chemical etching method to design the pattern on the Al 2 O 3 -The copper surface of DBC is processed.

[0050] S2. Position the chip accurately through the MARK point, and etch the chip groove of 15mm*15mm*0.28mm by laser etching.

[0051] S3. Coat Sn-Ag-Cu solder evenly on the copper surface at the bottom of the chip groove.

[0052] S4. Place the chip in the groove and heat it at 350°C for 20 minutes to complete the brazing. Since the chip groove 4 of the metalized ceramic substrate is small and easy to contact with adjacent circuits, the use of brazing can effectively ensure the accuracy of welding, prevent the solder from covering the circuit, and effectively en...

Embodiment 2

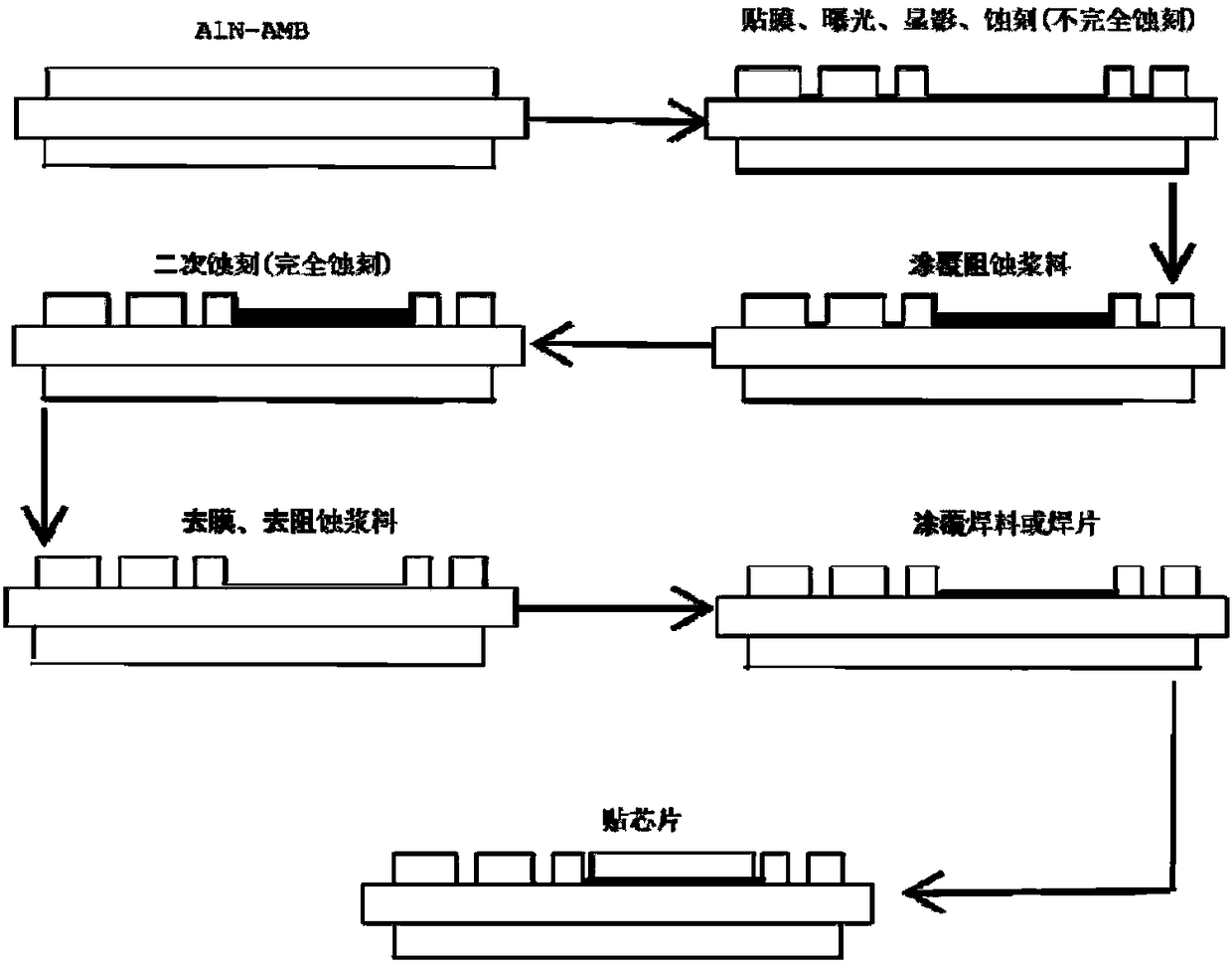

[0055] Such as image 3 As shown, the AlN-AMB metallized ceramic substrate with chip groove 4 and the reliability welding method, the method includes the following steps:

[0056] S1. The AlN-AMB substrate of 127mm*127mm*0.635mm (copper sheet specification 125mm*125mm*0.30mm) specifications is transferred to the copper layer through processes such as filming, exposure, and development.

[0057] S2. The pattern and groove are etched out by chemical etching, the etching depth is about 0.27mm, and the groove specification is 15mm*15mm.

[0058] S3. Cover the entire groove position with green oil, dry and harden.

[0059] S4. The remaining copper is quickly etched through the second chemical etching, the lines and grooves are processed, and then the film and the green oil are removed. At this time, the thickness of the groove metal layer is 0.03mm, which ensures the metal layer The coefficient of thermal expansion is small.

[0060] S5, and then evenly coat Sn-Ag-Cu solder on the copper su...

Embodiment 3

[0064] Such as Figure 4 As shown, the ZTA-DBA (Zirconium Oxide Toughened Alumina) metallized ceramic substrate with the chip groove 4 and the reliable welding method, this solution includes the following steps:

[0065] S1. Transfer the ZTA-DBA substrate of 138mm*190mm*0.32mm (aluminum sheet specification is 134mm*184mm*0.30mm) to the aluminum layer through filming, exposure, and development processes.

[0066] S2. The circuit is processed by chemical etching, and the etching depth is the thickness of the aluminum layer.

[0067] S3. Using mechanical processing, a groove of 15mm*15mm*0.28mm is processed at the chip position.

[0068] S4. Nickel is plated on the ZTA-DBA aluminum layer by electroless plating.

[0069] S5. Then evenly coat Sn-Ag-Cu solder on the bottom aluminum surface of the chip groove 4.

[0070] S6. Place the chip in the chip groove 4 and heat it at 350°C for 20 minutes to complete the brazing.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| etching depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More