Patents

Literature

95results about How to "Fast etch" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

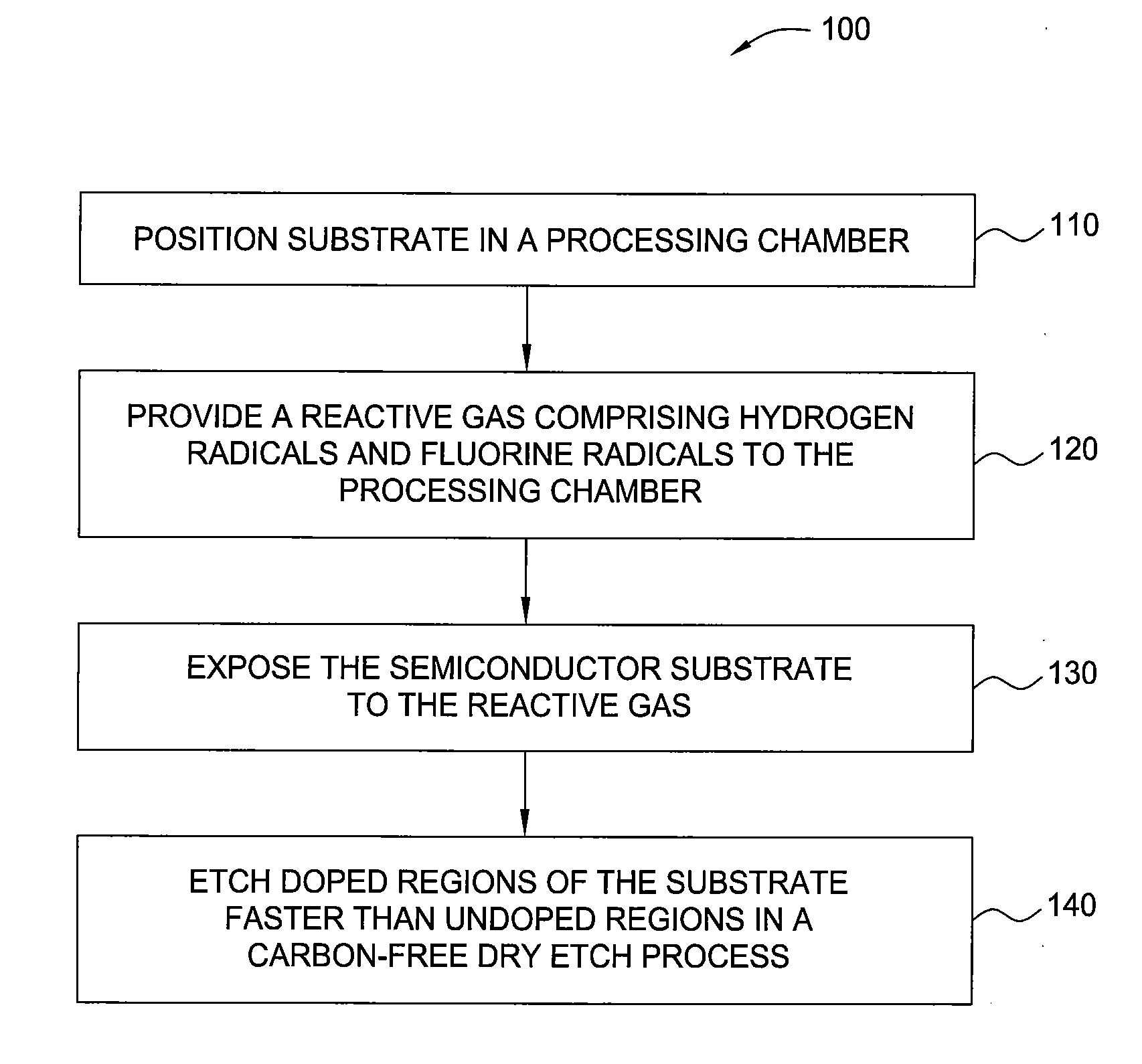

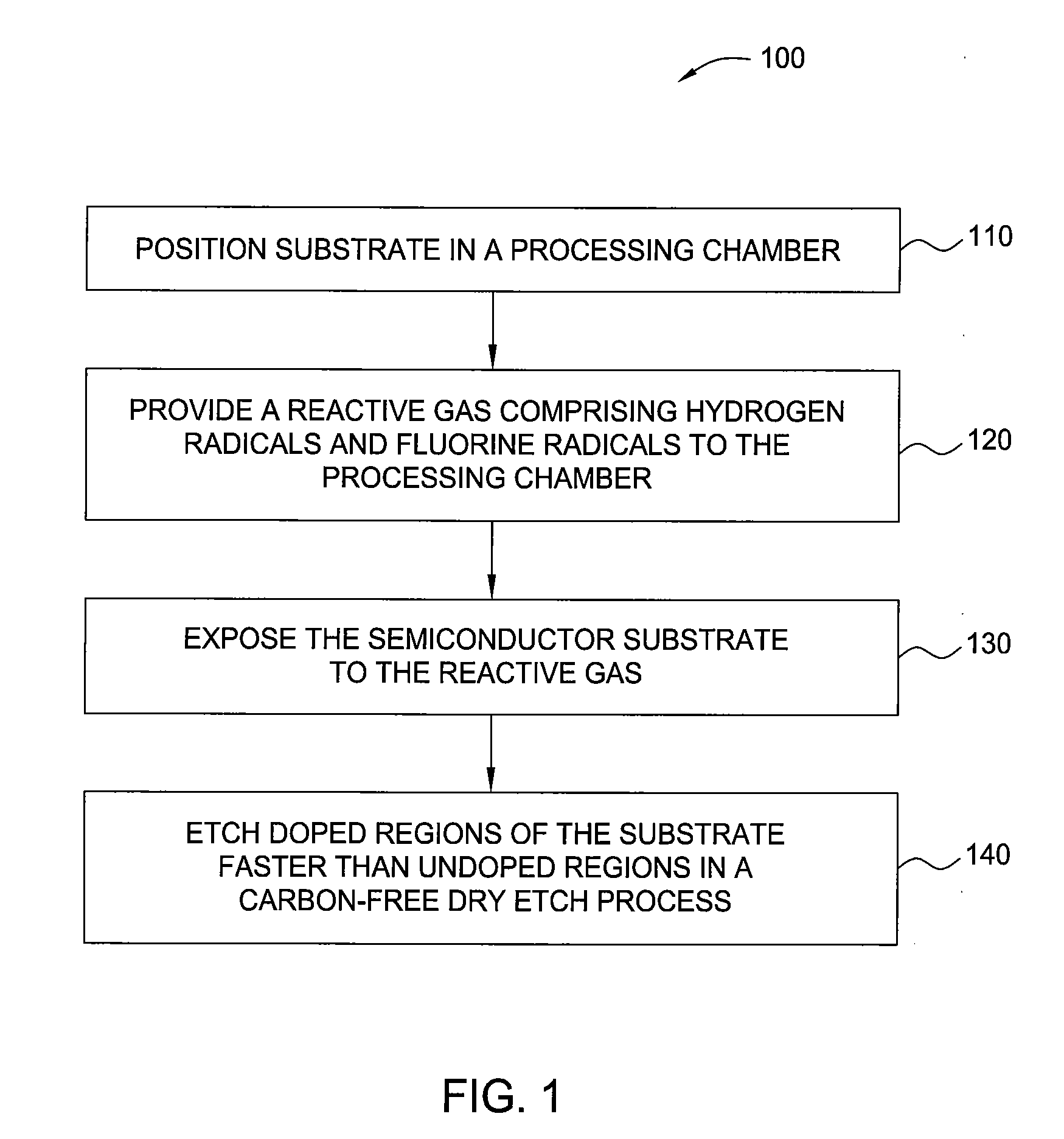

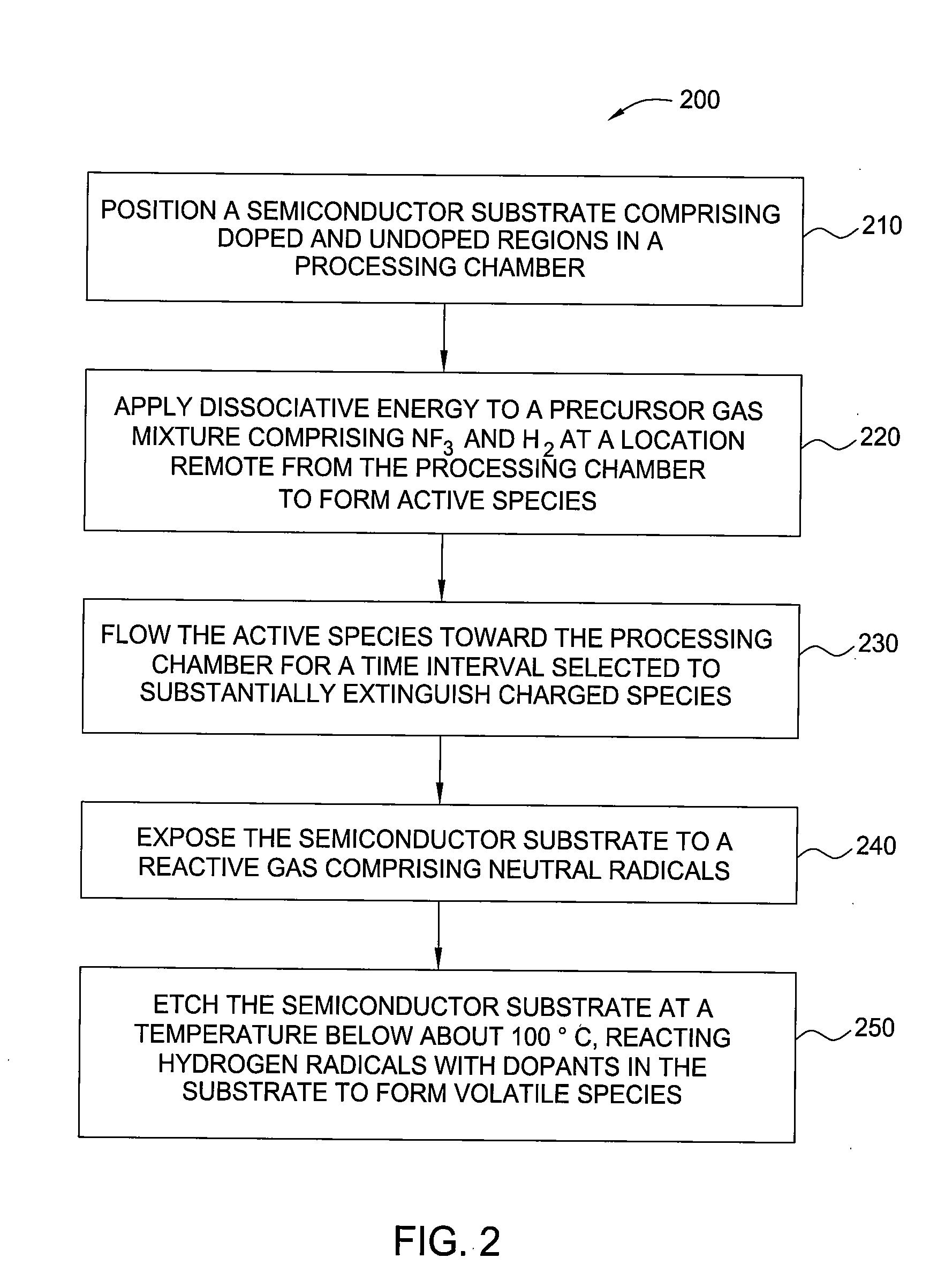

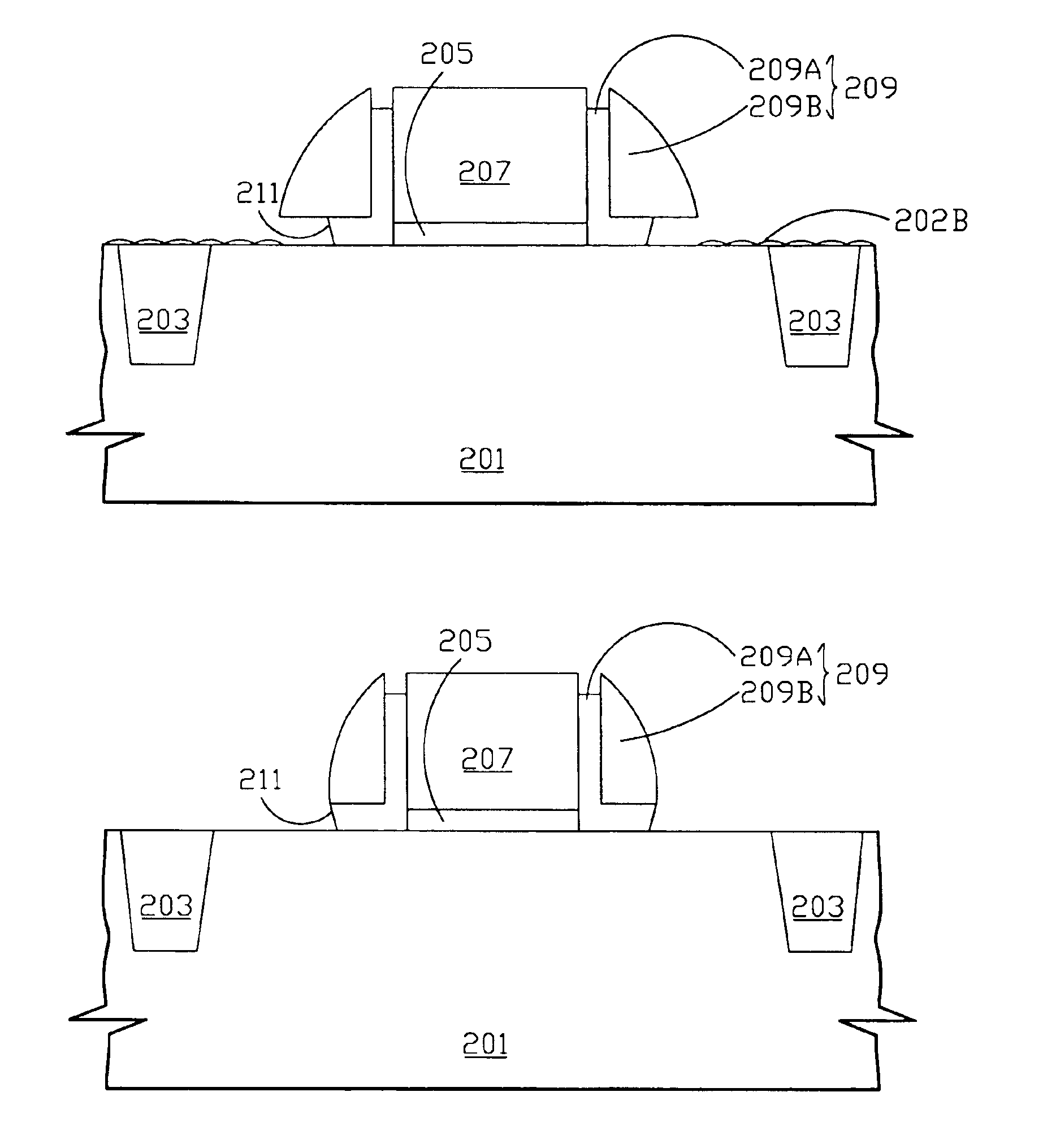

Nf3/h2 remote plasma process with high etch selectivity of psg/bpsg over thermal oxide and low density surface defects

InactiveUS20100099263A1Fast etchElectric discharge tubesSemiconductor/solid-state device manufacturingHydrogenRemote plasma

A method and apparatus for selectively etching doped semiconductor oxides faster than undoped oxides. The method comprises applying dissociative energy to a mixture of nitrogen trifluoride and hydrogen gas remotely, flowing the activated gas toward a processing chamber to allow time for charged species to be extinguished, and applying the activated gas to the substrate. Reducing the ratio of hydrogen to nitrogen trifluoride increases etch selectivity. A similar process may be used to smooth surface defects in a silicon surface.

Owner:APPLIED MATERIALS INC

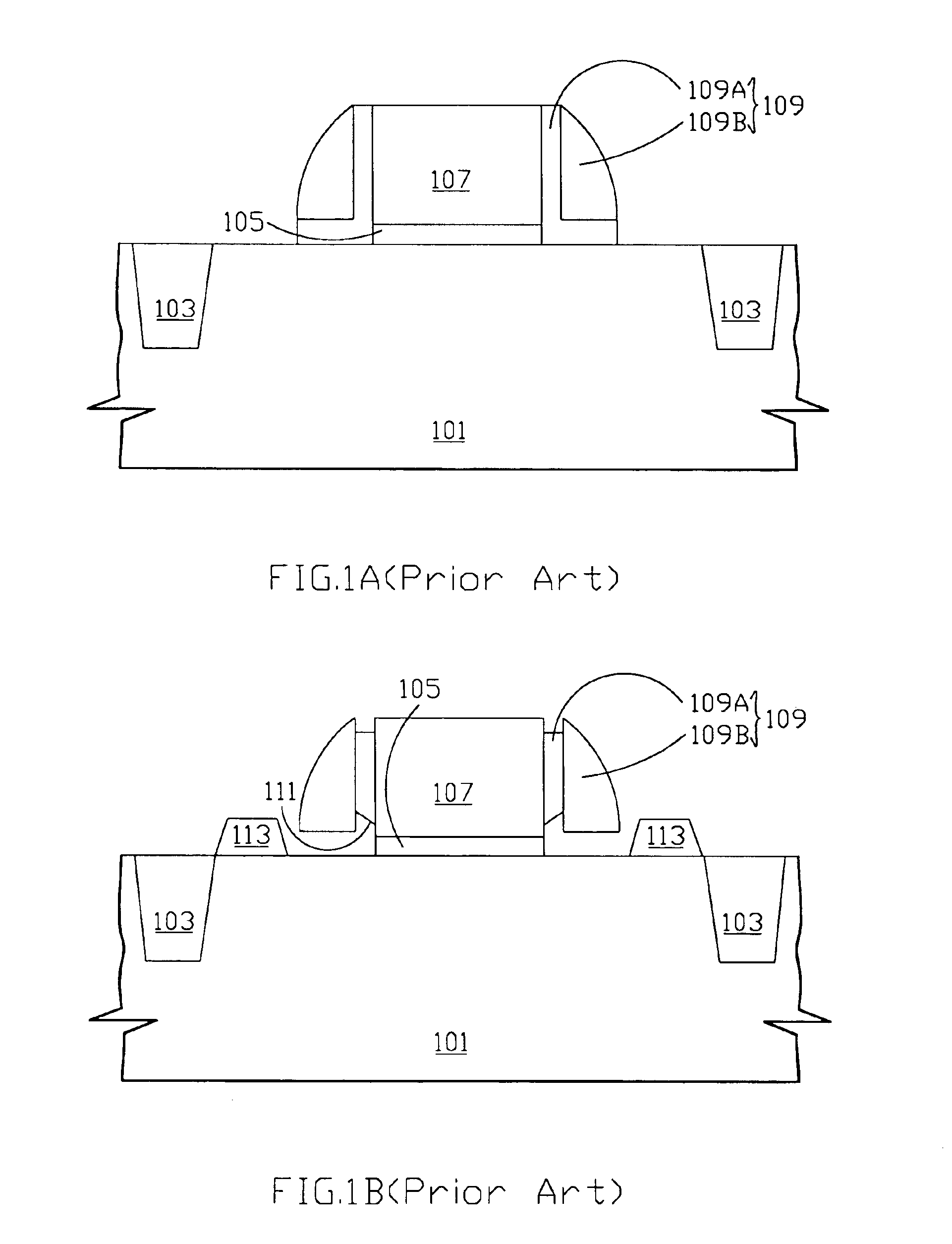

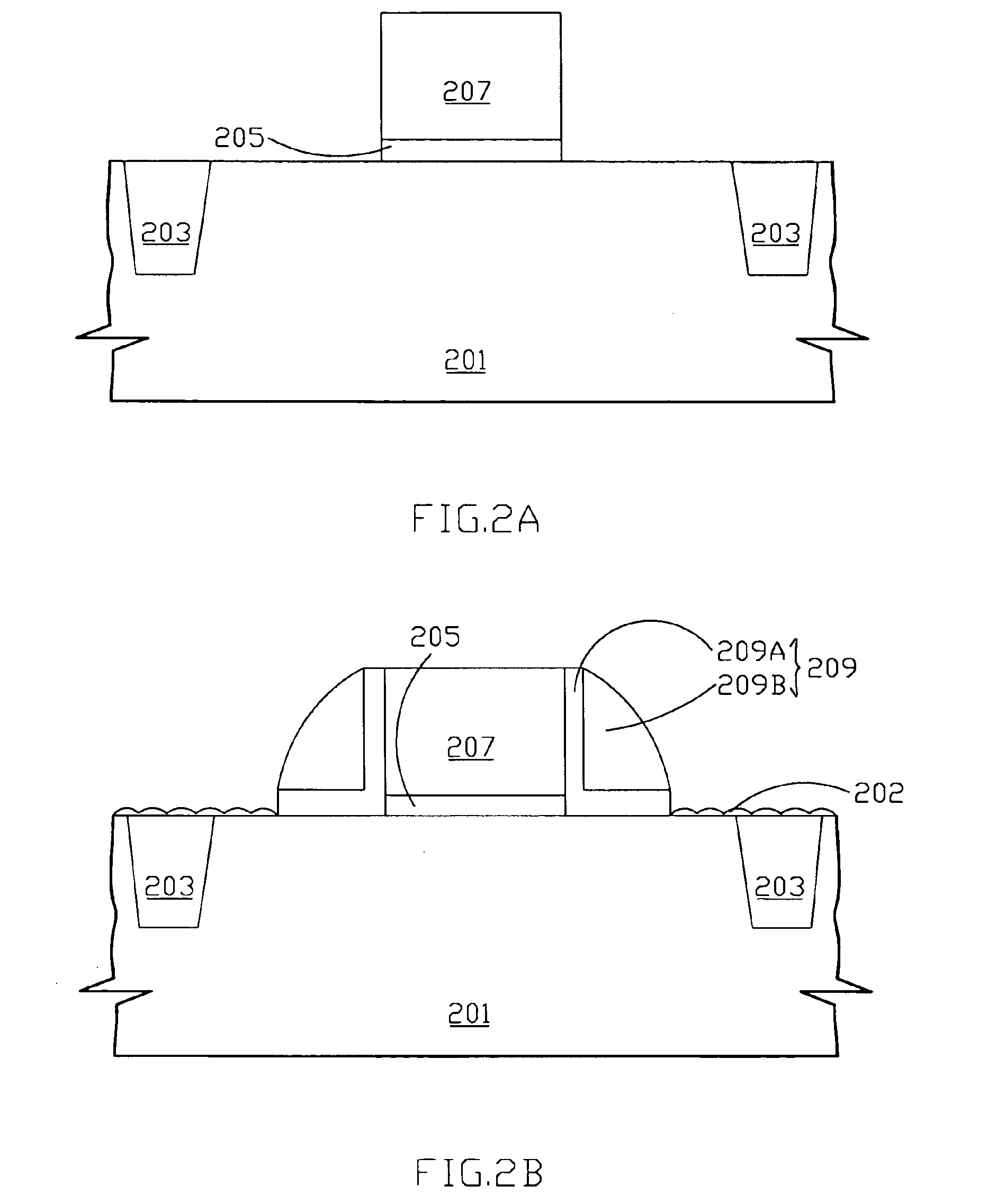

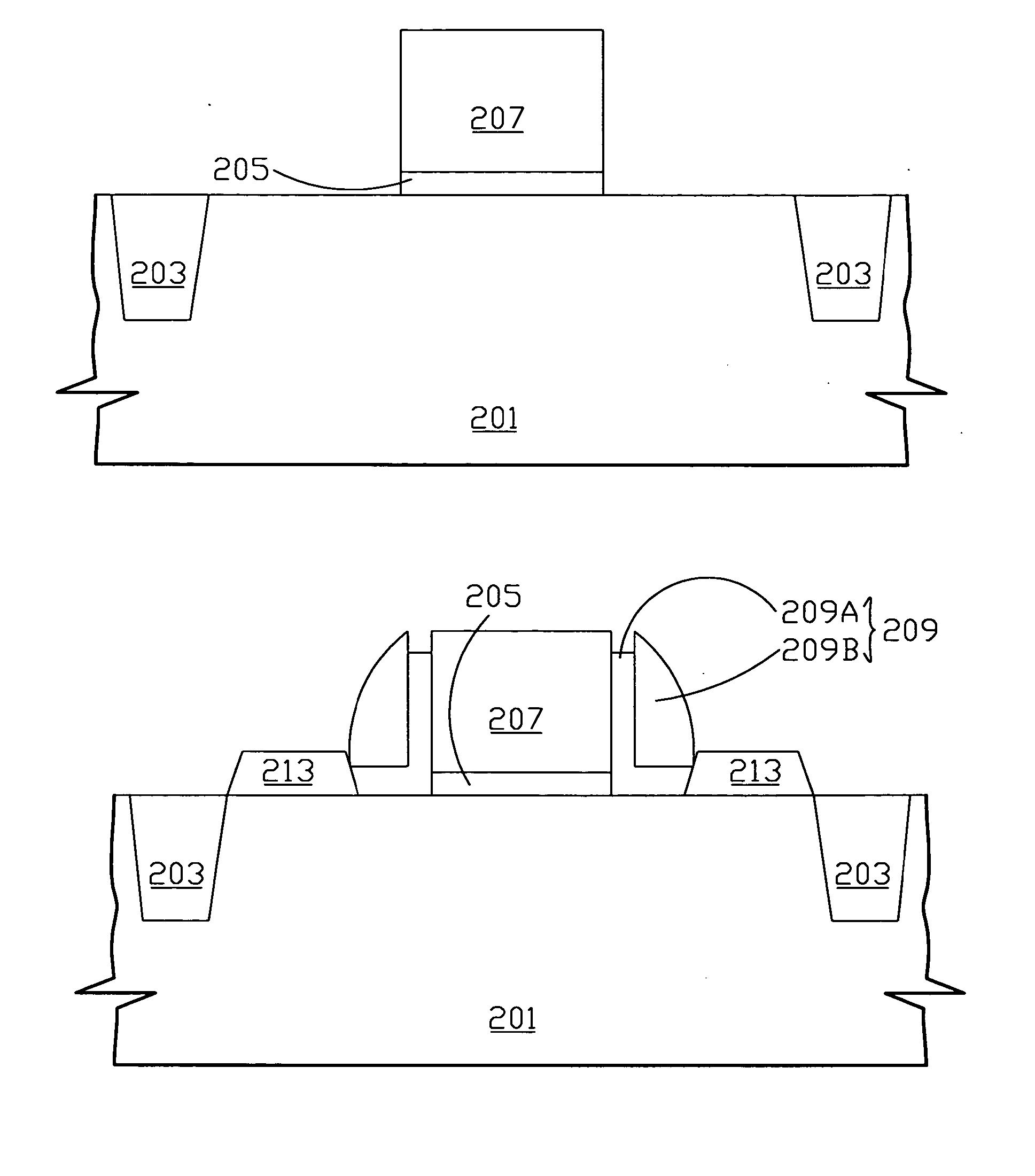

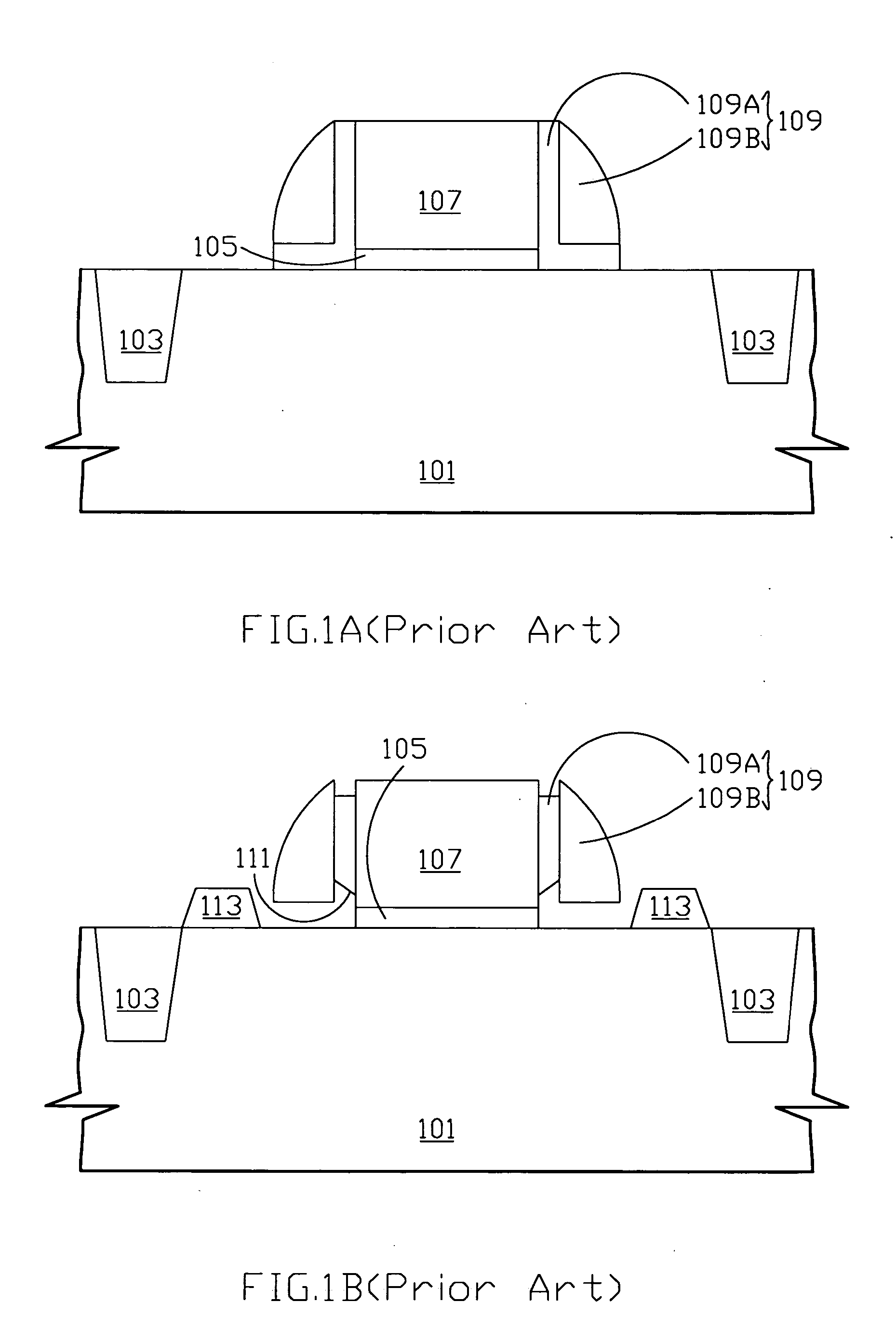

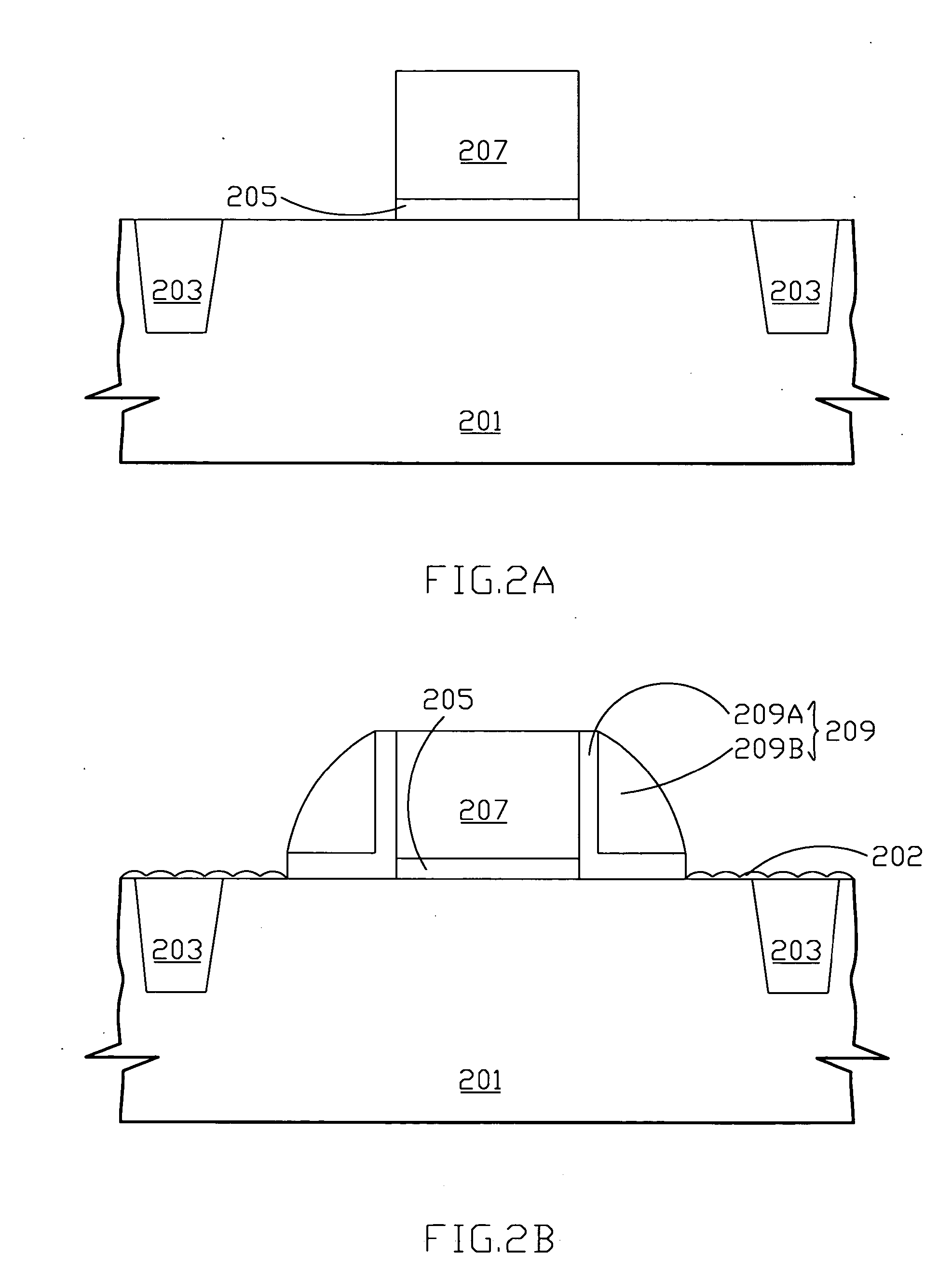

Method for preventing to form a spacer undercut in SEG pre-clean process

InactiveUS6991991B2Avoid leakage currentFast etchSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

A method for preventing to form a spacer undercut in SEG preclean process is provided. This present invention utilizes HFEG solution to etch the first spacer and the second spacer simultaneously, which can prevent from producing a spacer undercut, meanwhile; a native oxide layer upon a surface of a semiconductor substrate is removed. Hence, the clean surface on the semiconductor substrate is obtained. This method includes the steps as follows: Firstly, the native oxide layer upon the surface of the semiconductor substrate is removed by DHF (HF in deionized water) solution. Then, etching the first spacer and the second spacer at the same time by HFEG (HF diluted by ethylene glycol) solution. Also, the native oxide upon the semiconductor substrate is removed. Therefore, it obtains the clean semiconductor surface without a serious spacer undercut.

Owner:MARLIN SEMICON LTD

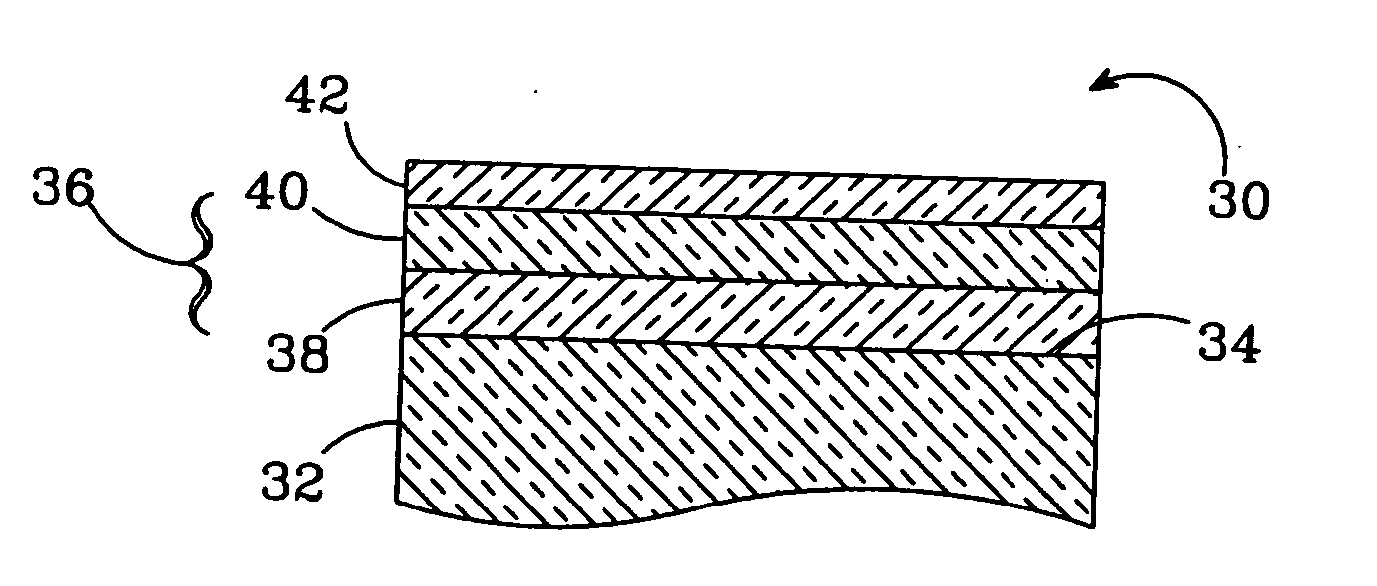

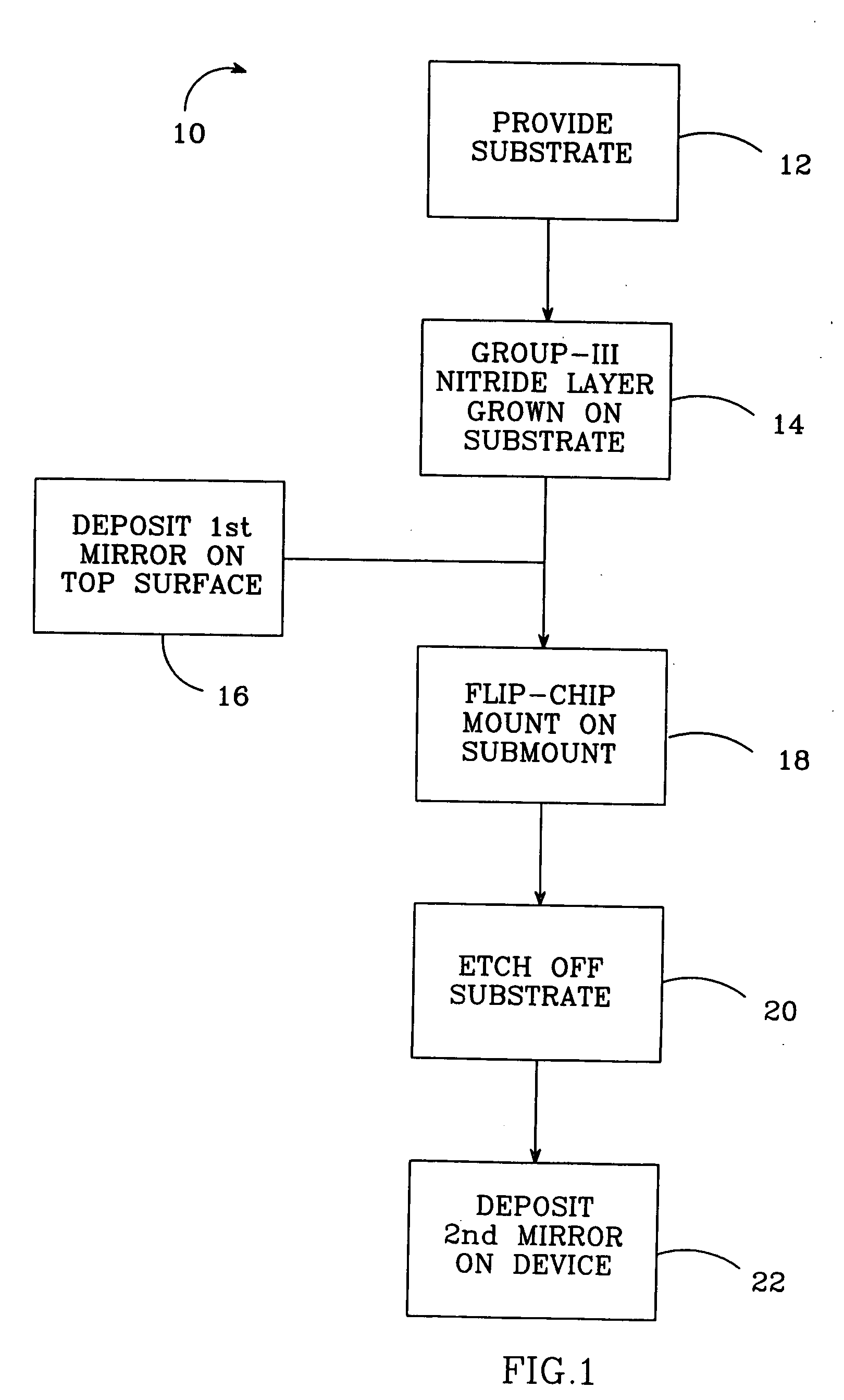

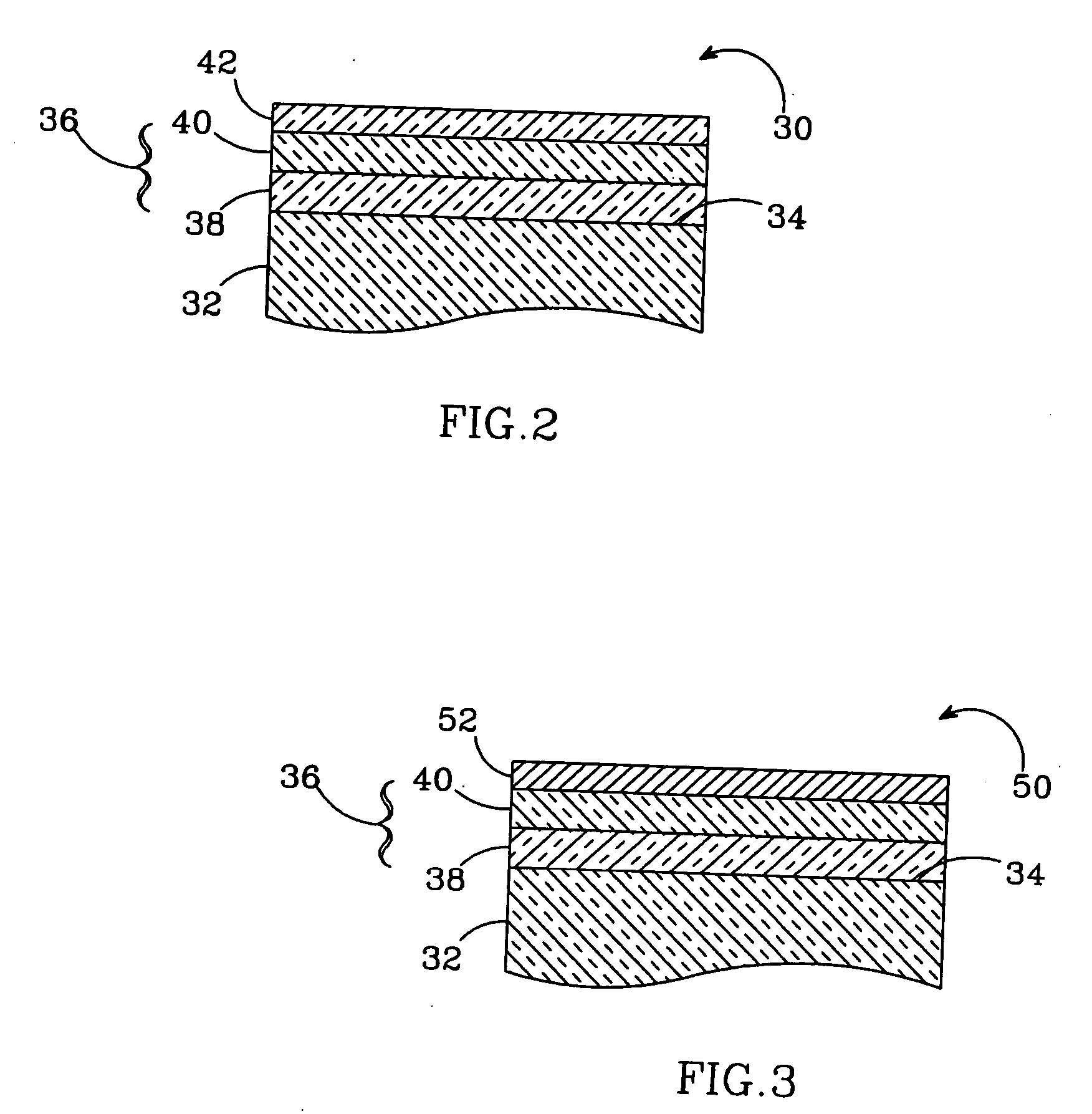

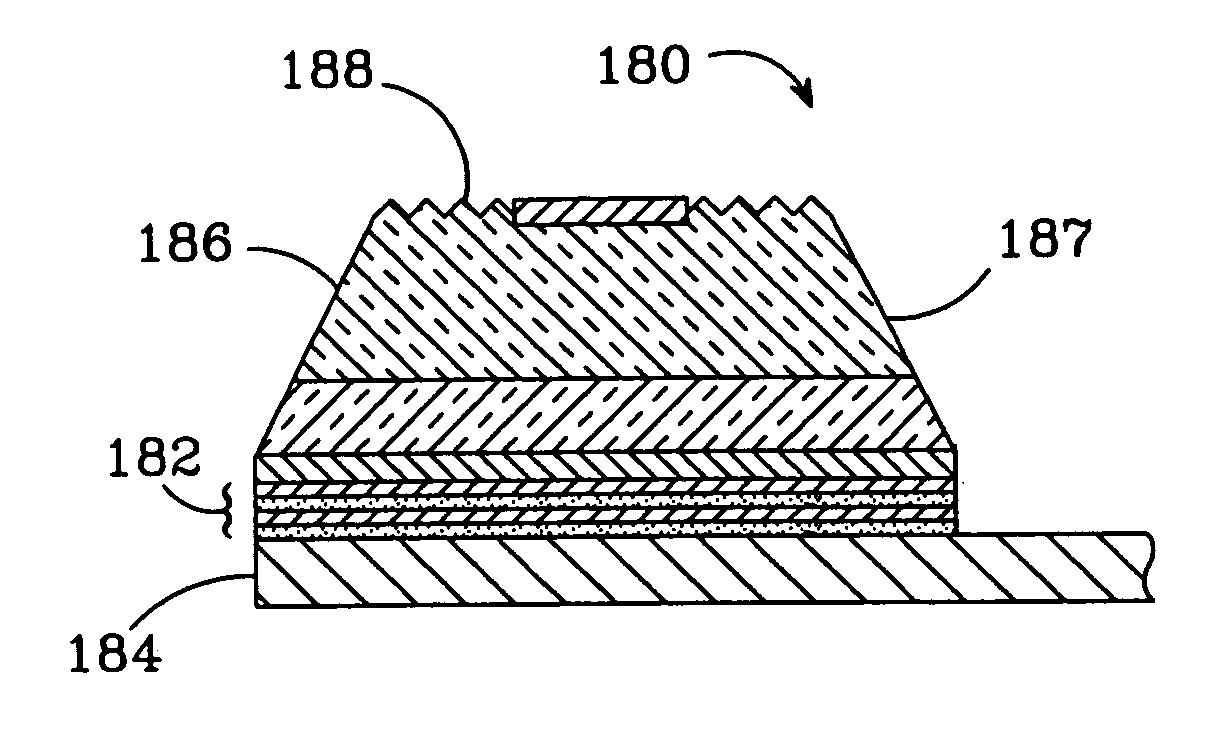

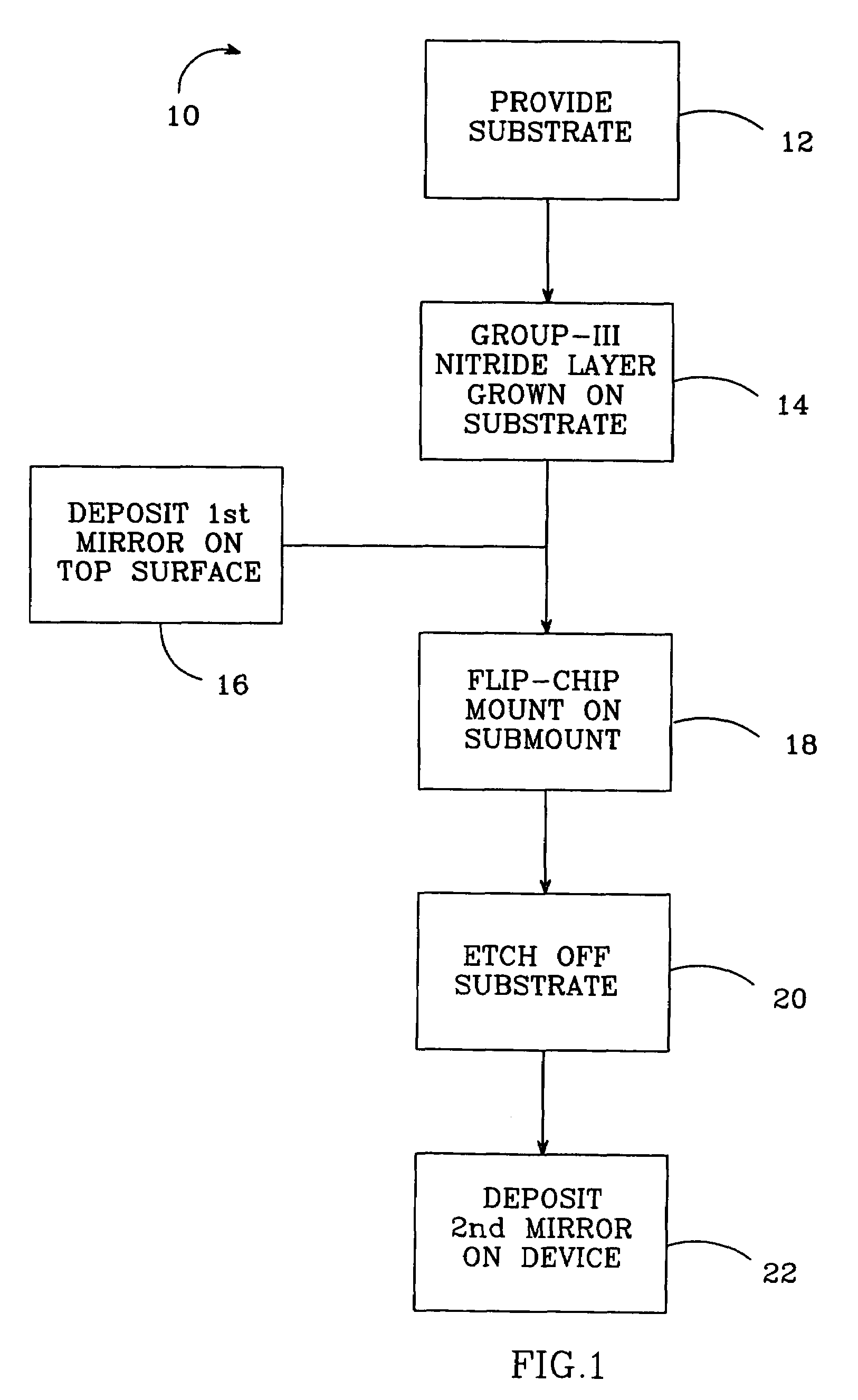

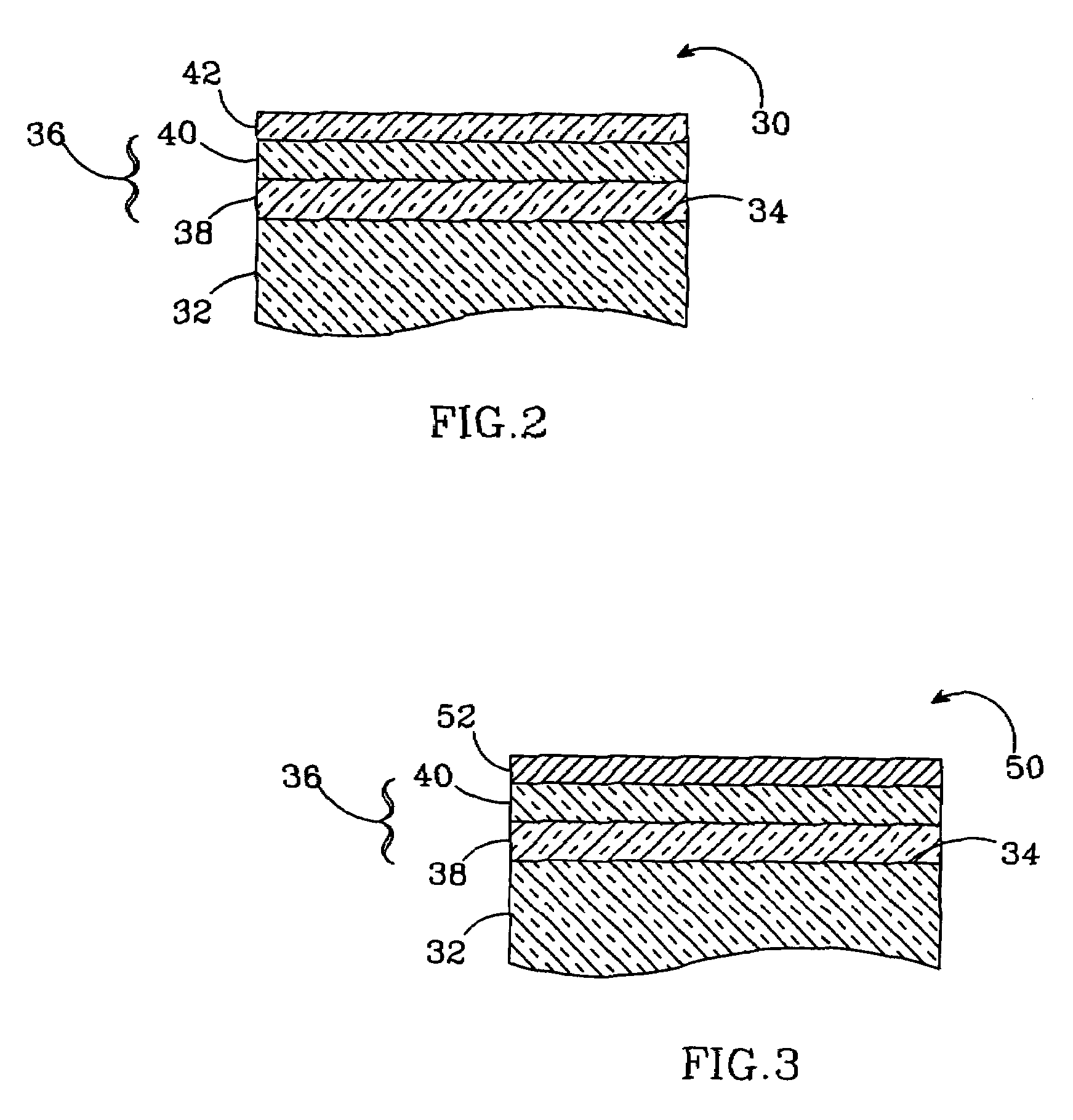

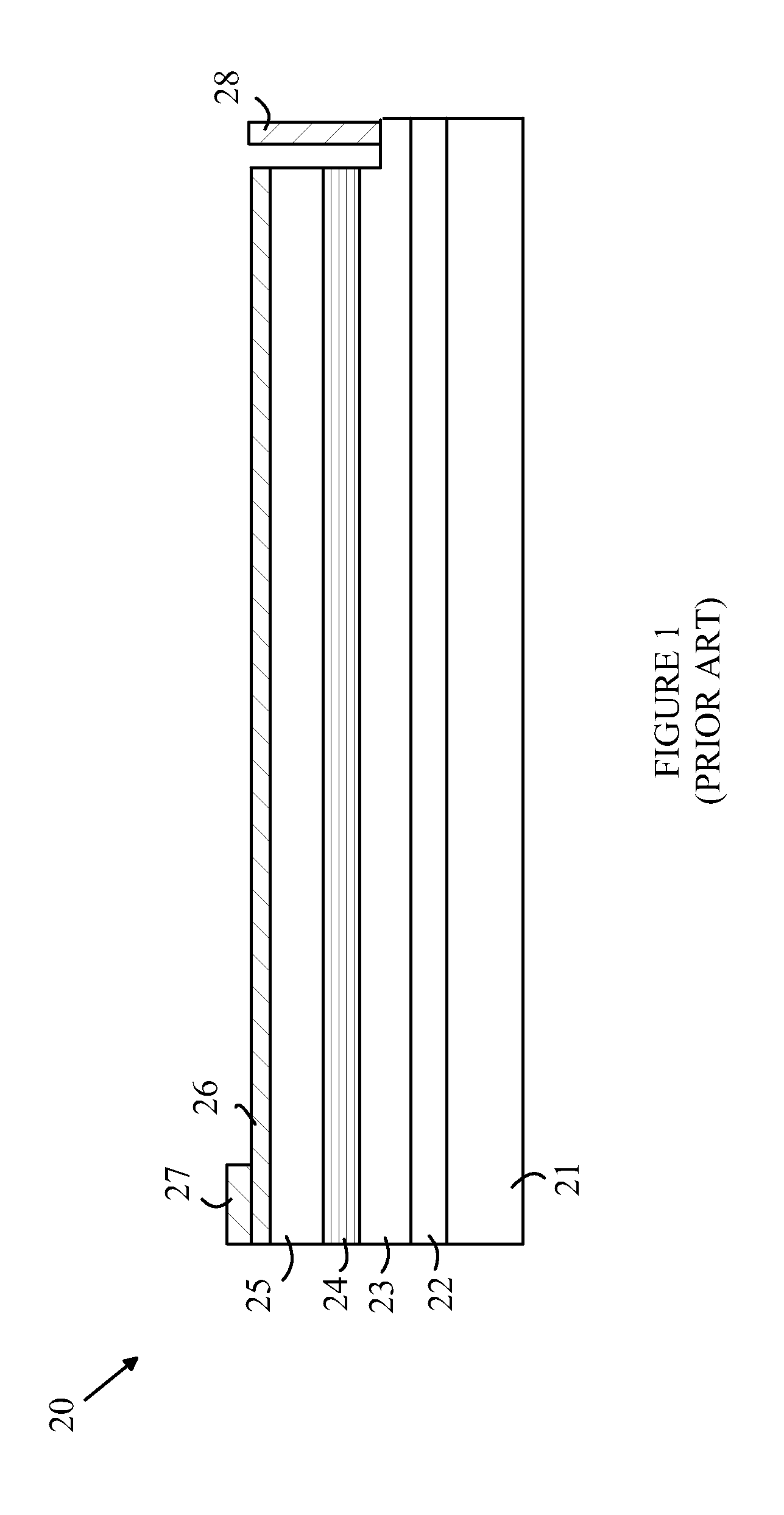

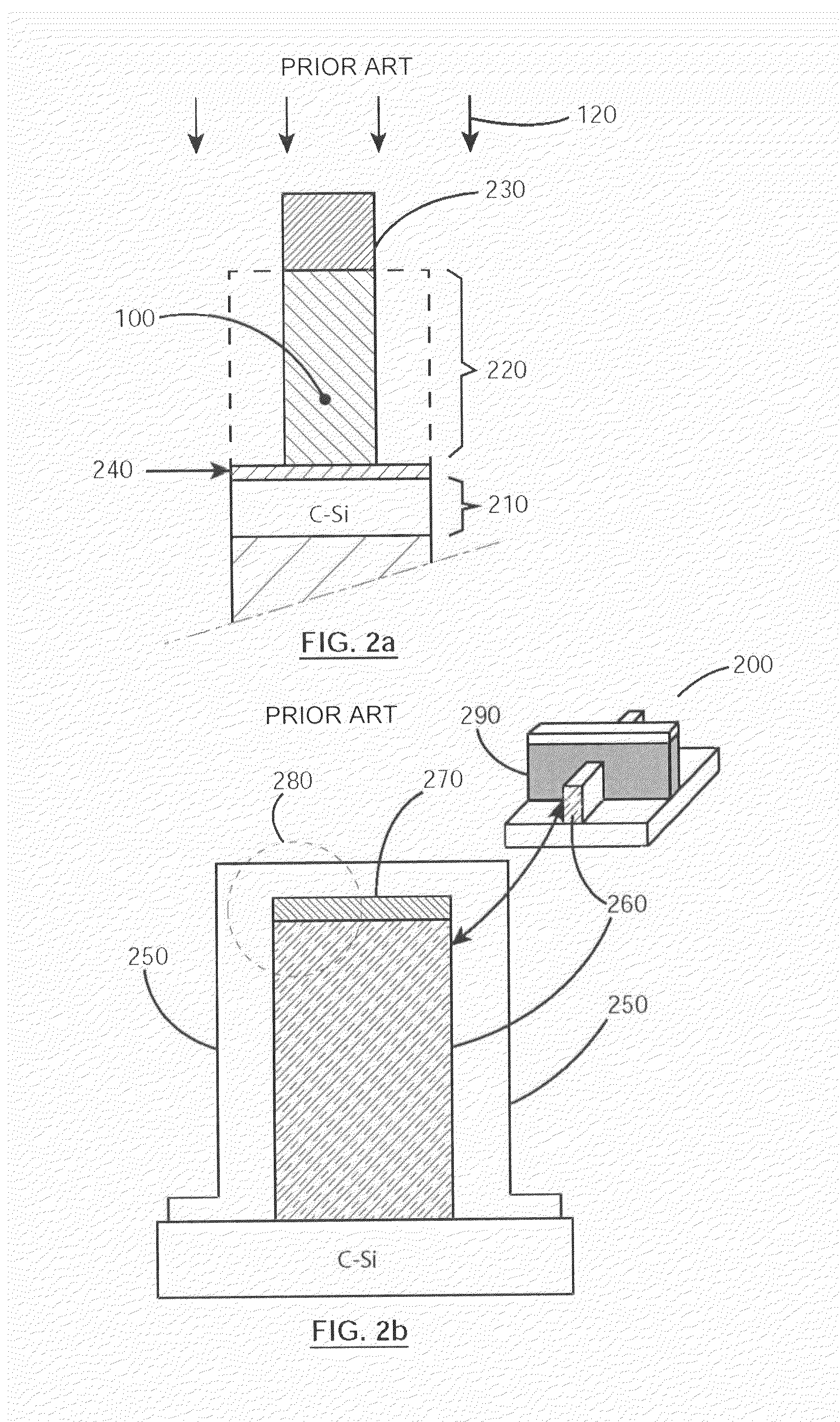

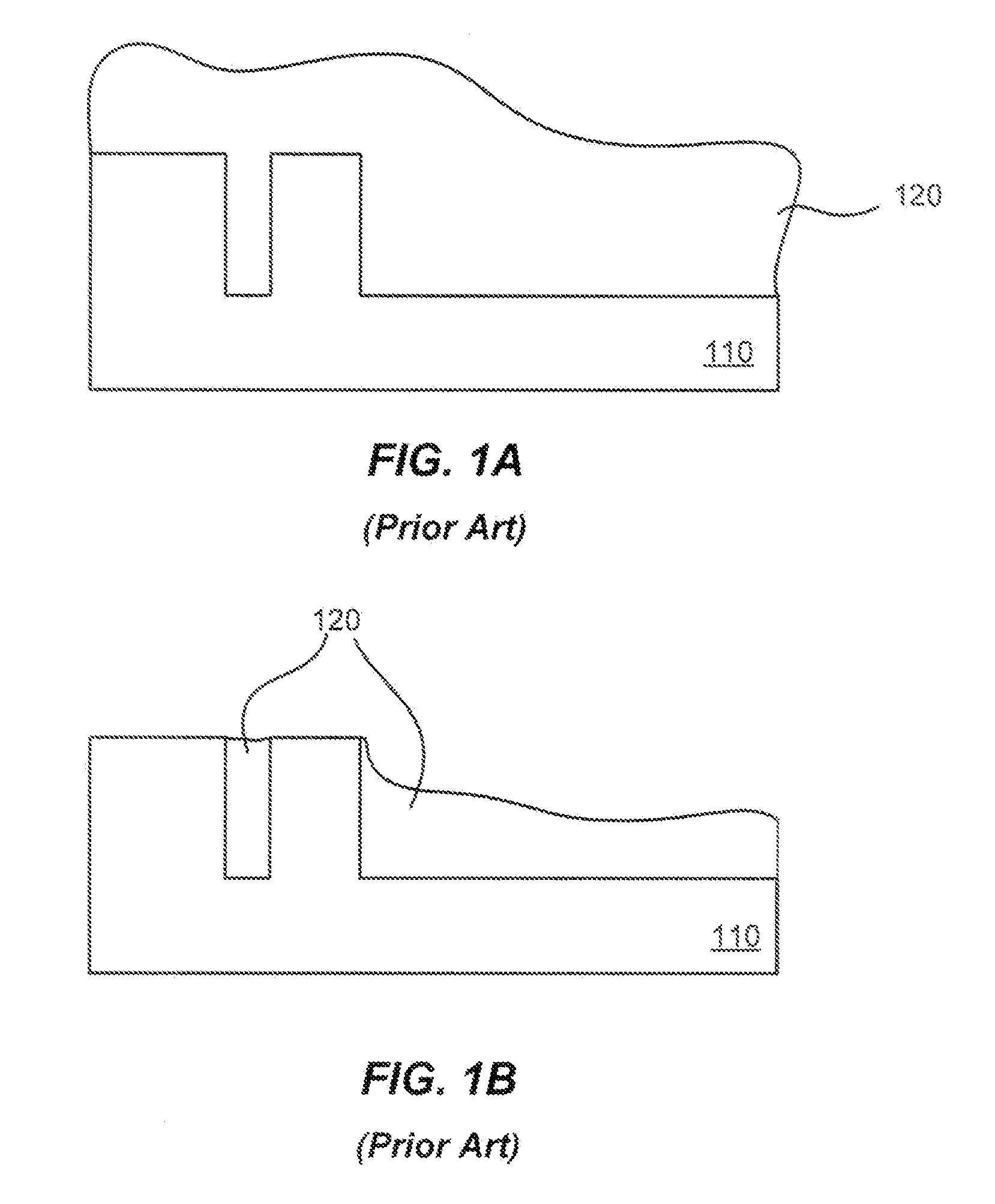

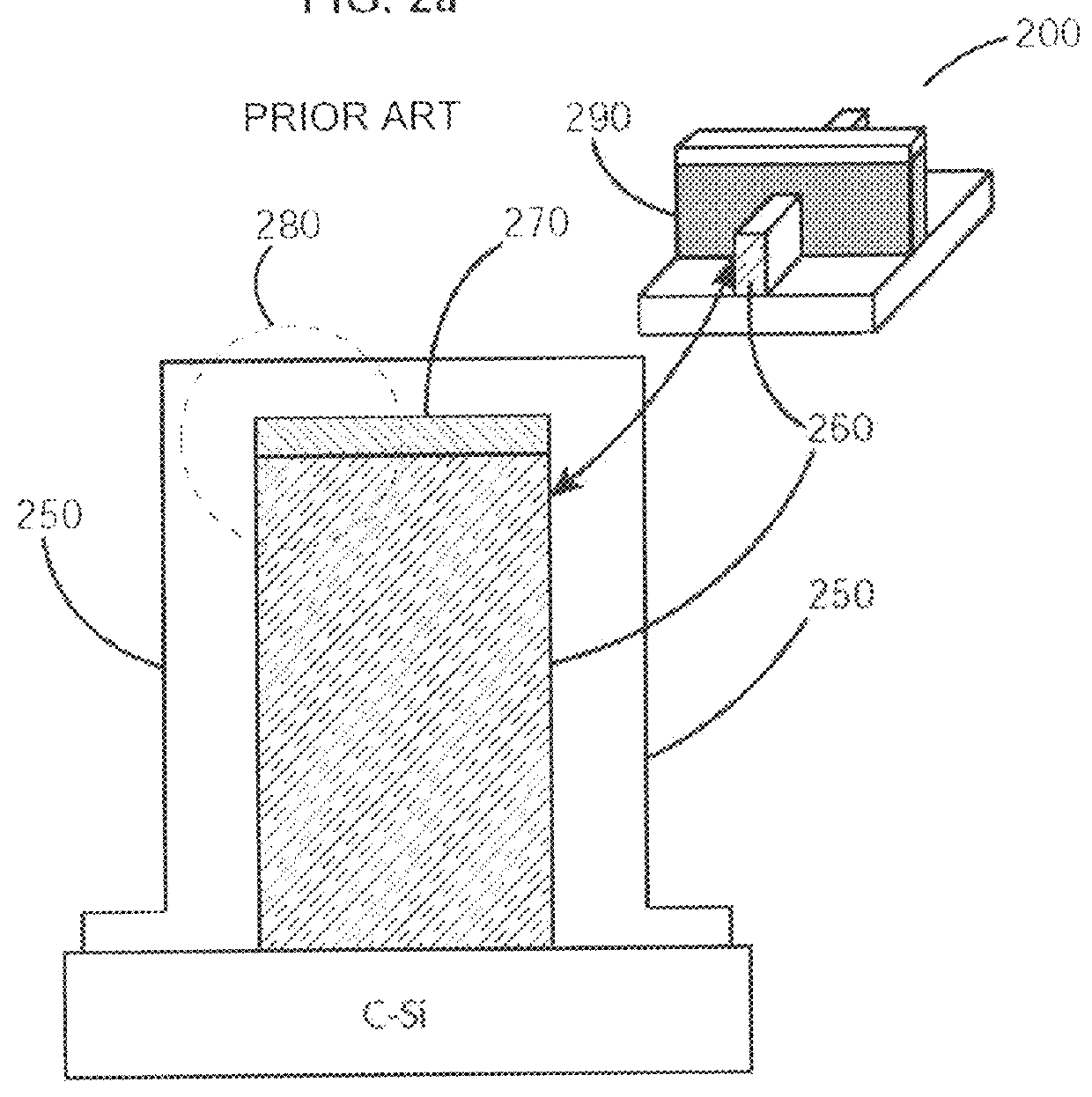

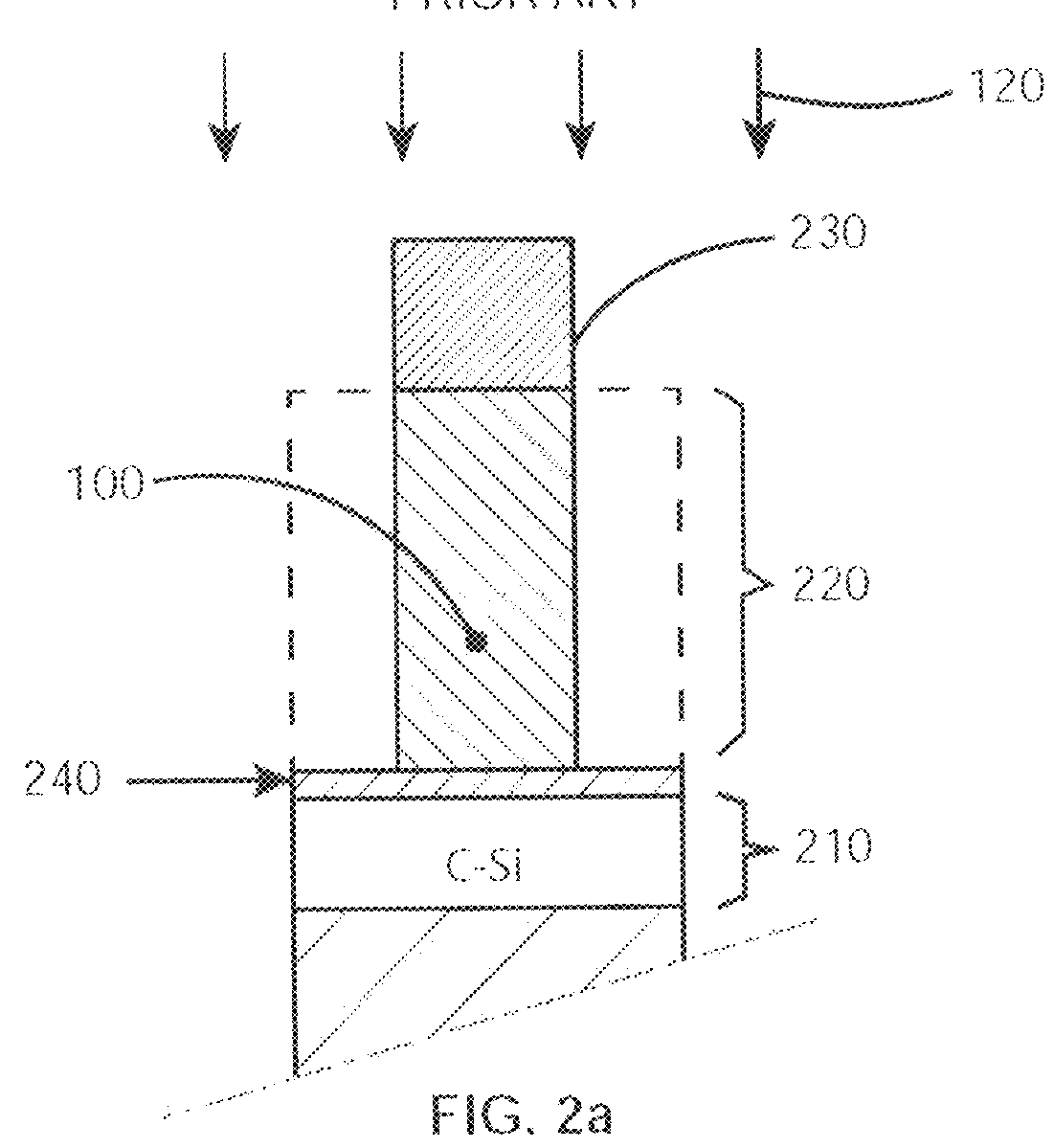

Method for fabricating group-III nitride devices and devices fabricated using method

ActiveUS20060049411A1Fast etchSolid-state devicesSemiconductor/solid-state device manufacturingResonant cavityDevice material

A method according to the present invention for fabricating high light extraction photonic devices comprising growing an epitaxial semiconductor structure on a substrate and depositing a first mirror layer on the epitaxial semiconductor structure such that the epitaxial semiconductor structure is sandwiched between the first mirror layer and the substrate. Flip-chip mounting the epitaxial semiconductor structure, with its first mirror and substrate on a submount such that the epitaxial semiconductor device structure is sandwiched between the submount and substrate. The substrate is then removed from the epitaxial structure by introducing an etch environment to the substrate. A second mirror layer is deposited on the epitaxial semiconductor structure such that the epitaxial semiconductor structure is sandwiched between the first and second mirror layers. A device according to the present invention comprising a resonant cavity light emitting diode (RCLED) mounted to a submount.

Owner:CREELED INC

Method for fabricating group-III nitride devices and devices fabricated using method

ActiveUS7332365B2Fast etchSolid-state devicesSemiconductor/solid-state device manufacturingResonant cavitySemiconductor structure

A method according to the present invention for fabricating high light extraction photonic devices comprising growing an epitaxial semiconductor structure on a substrate and depositing a first mirror layer on the epitaxial semiconductor structure such that the epitaxial semiconductor structure is sandwiched between the first mirror layer and the substrate. Flip-chip mounting the epitaxial semiconductor structure, with its first mirror and substrate on a submount such that the epitaxial semiconductor device structure is sandwiched between the submount and substrate. The substrate is then removed from the epitaxial structure by introducing an etch environment to the substrate. A second mirror layer is deposited on the epitaxial semiconductor structure such that the epitaxial semiconductor structure is sandwiched between the first and second mirror layers. A device according to the present invention comprising a resonant cavity light emitting diode (RCLED) mounted to a submount.

Owner:CREELED INC

Interconnect structure improvements

InactiveUS6960519B1Fast etchImprove conductivitySemiconductor/solid-state device detailsSolid-state devicesStress inducedCapacitance

Methods and conductive interconnect structures are provided for preventing cracks in a dielectric layer on a substrate. Substantially half cylindrical or cylindrical trench openings are formed within at least one dielectric layer, which are then filled with a high conductivity metal for forming substantially half cylindrical or cylindrical wires. The rounded bottom portions of the substantially half cylindrical wires, or the rounded bottom and top portions of the substantially half cylindrical wires, avoid any propagation points for starting cracks in the dielectric layer, as compared to conventional rectangular conductors having angled edges, which in fact are propagation points for initiating cracks. The substantially half cylindrical or cylindrical wires also reduce the line-to-line capacitance between neighboring wires, substantially eliminate any high stress points in the dielectric layer, reduce mechanical stresses induced on the IC and increase the overall mechanical strength of the IC.

Owner:INTELLECTUAL DISCOVERY INC

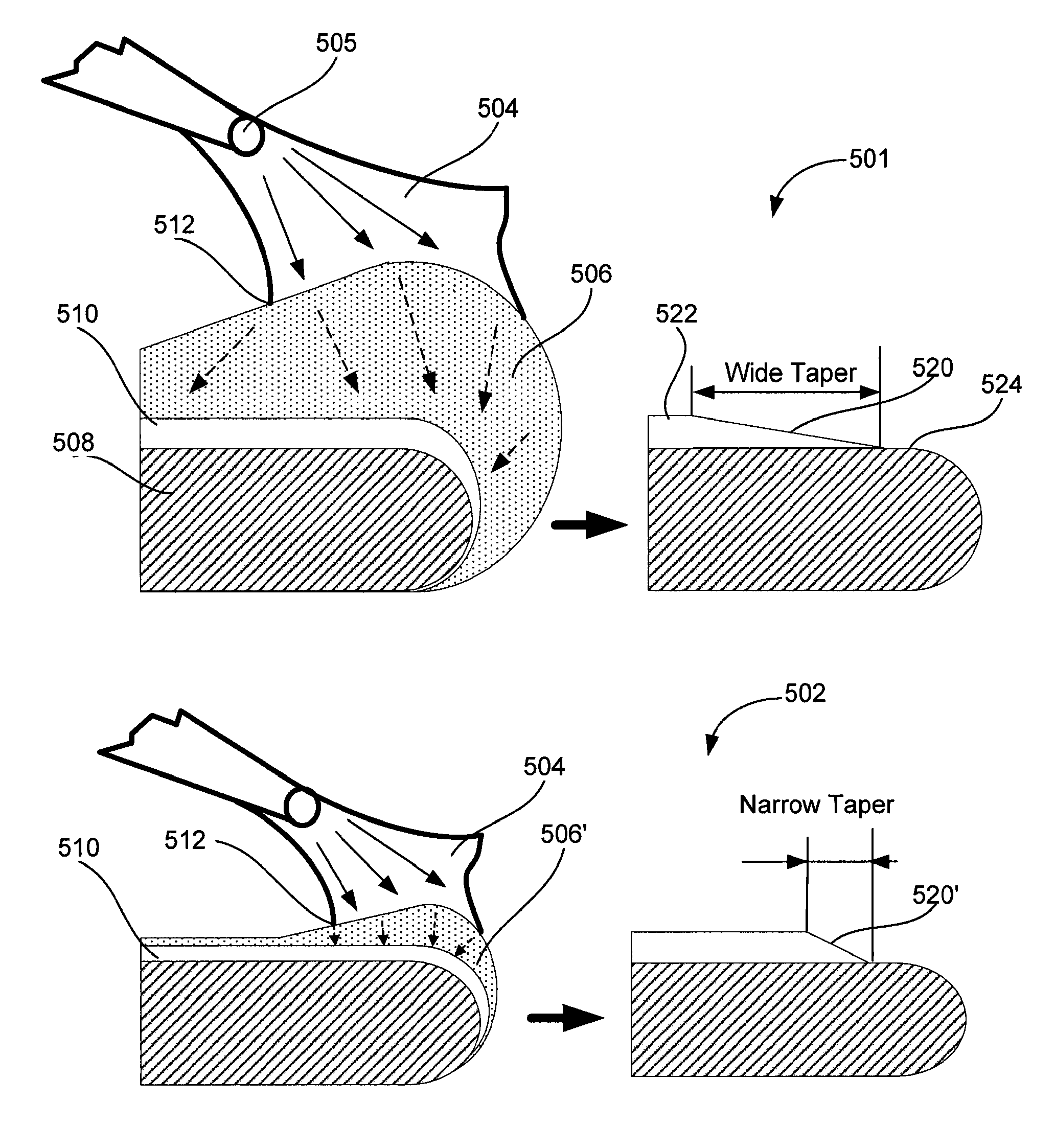

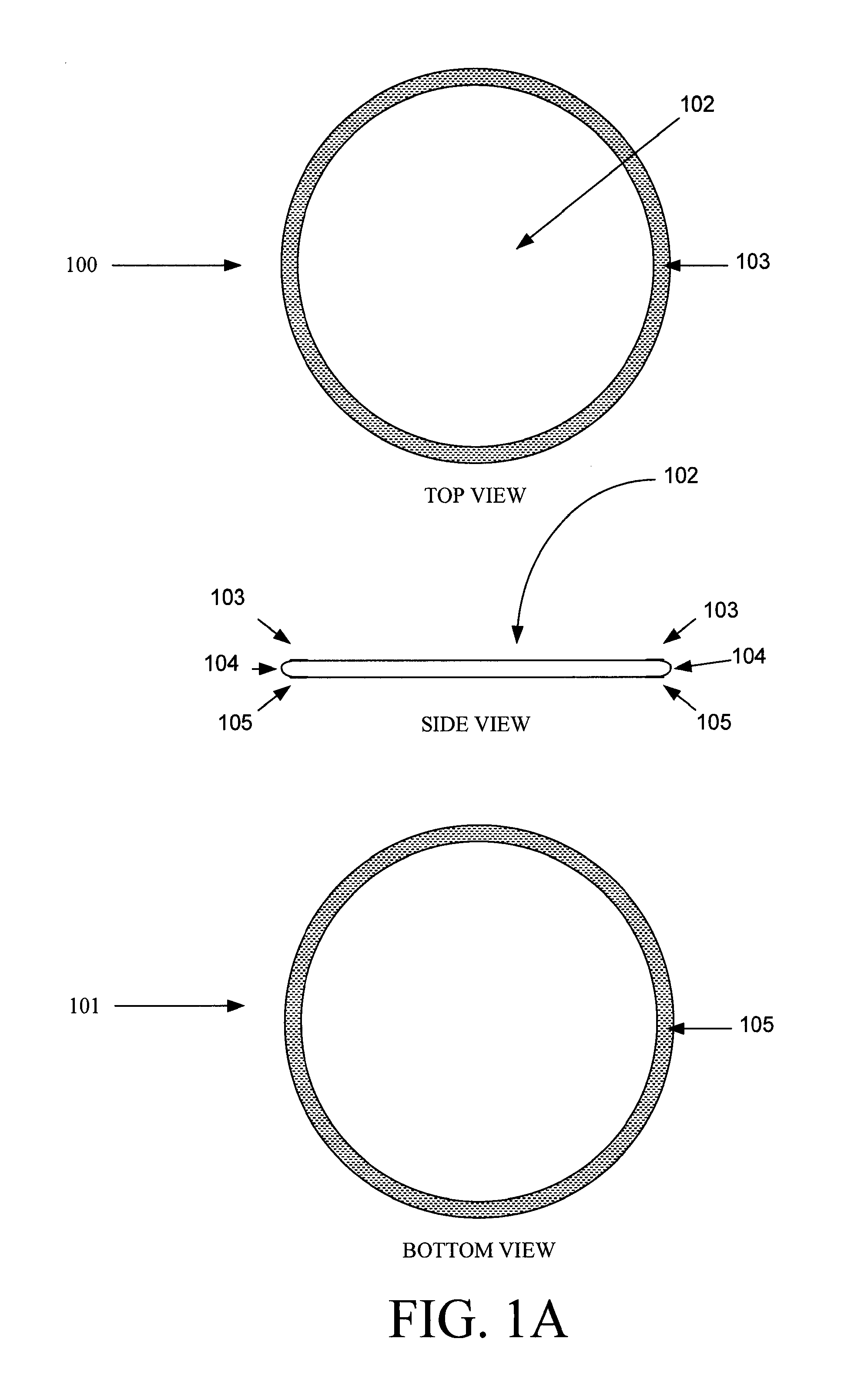

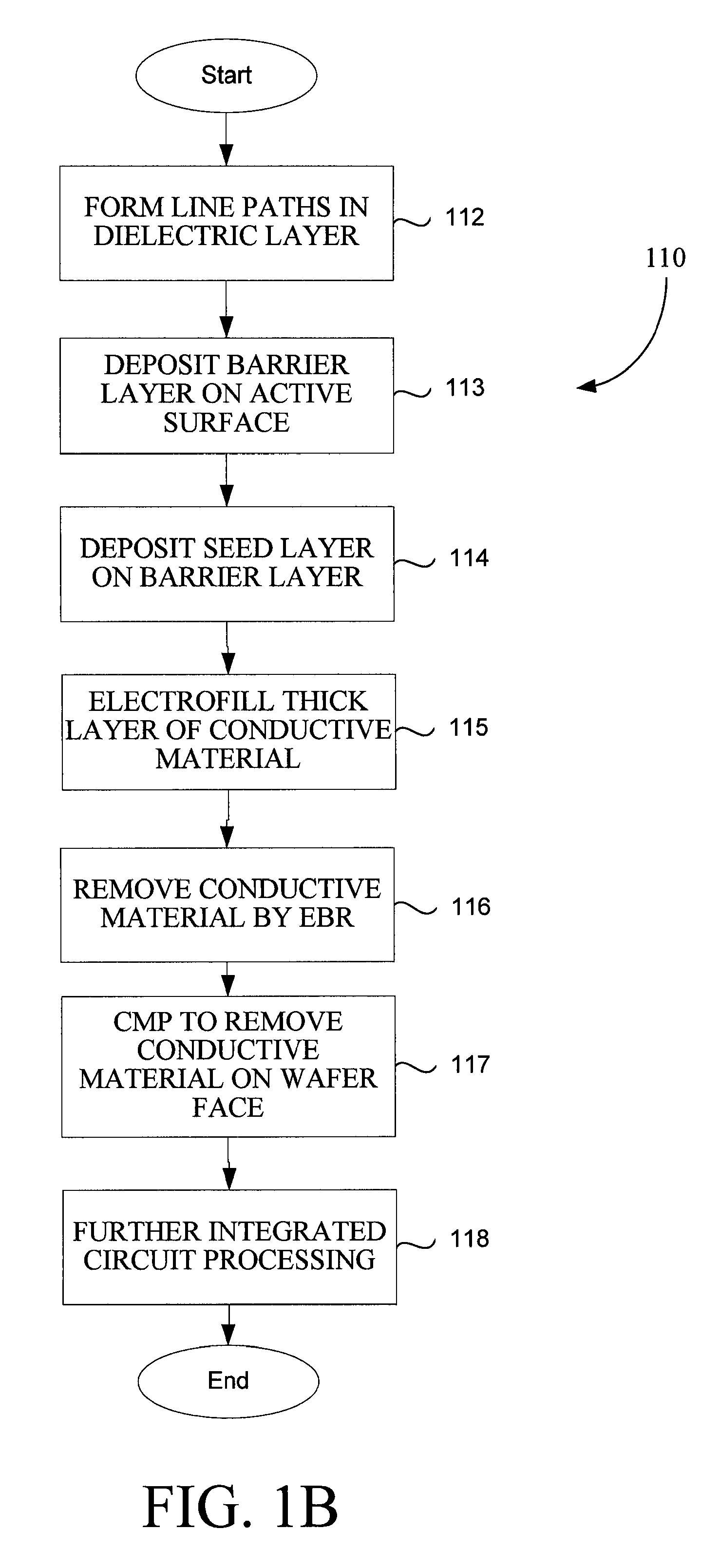

Apparatus and method for edge bevel removal of copper from silicon wafers

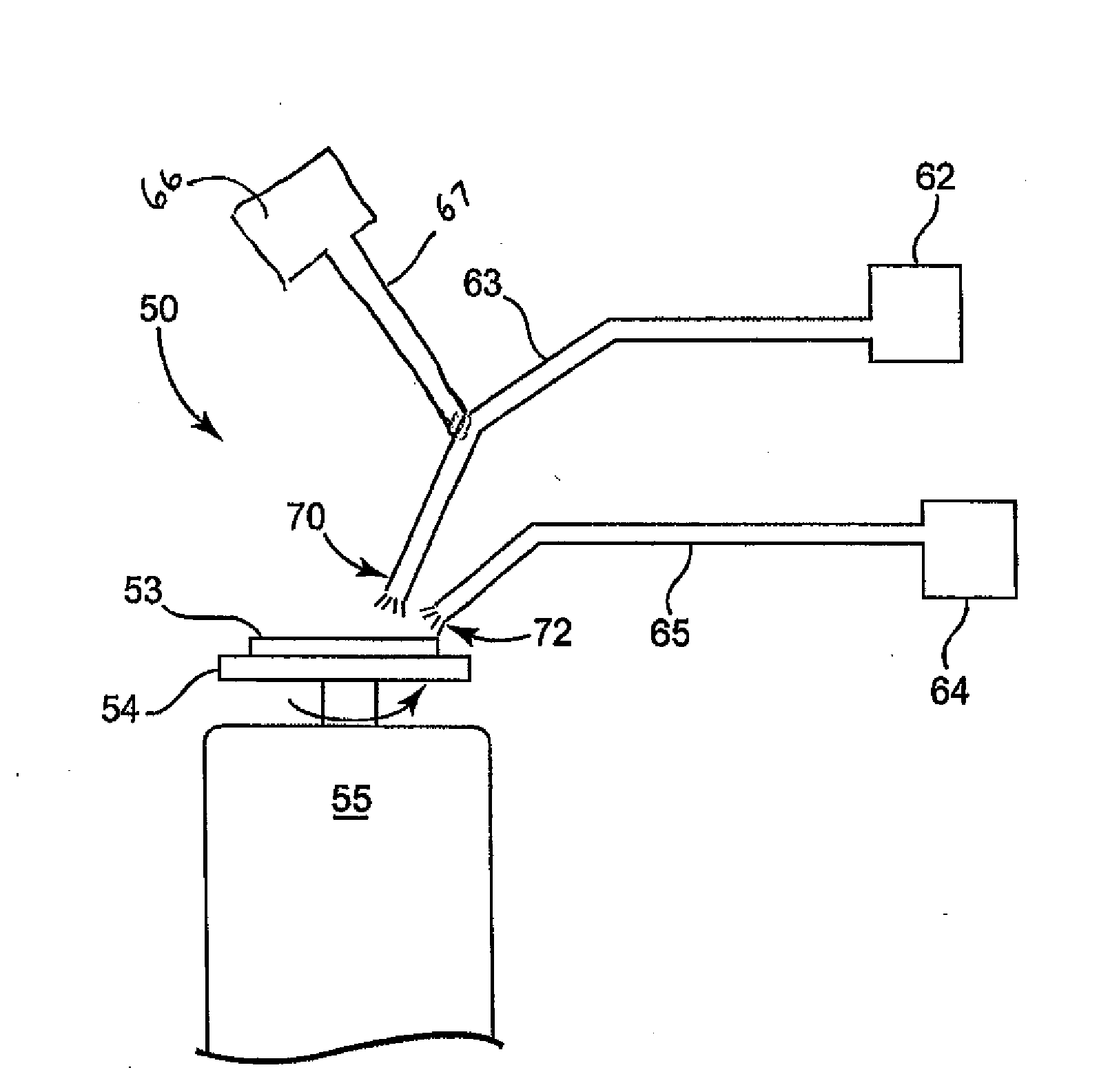

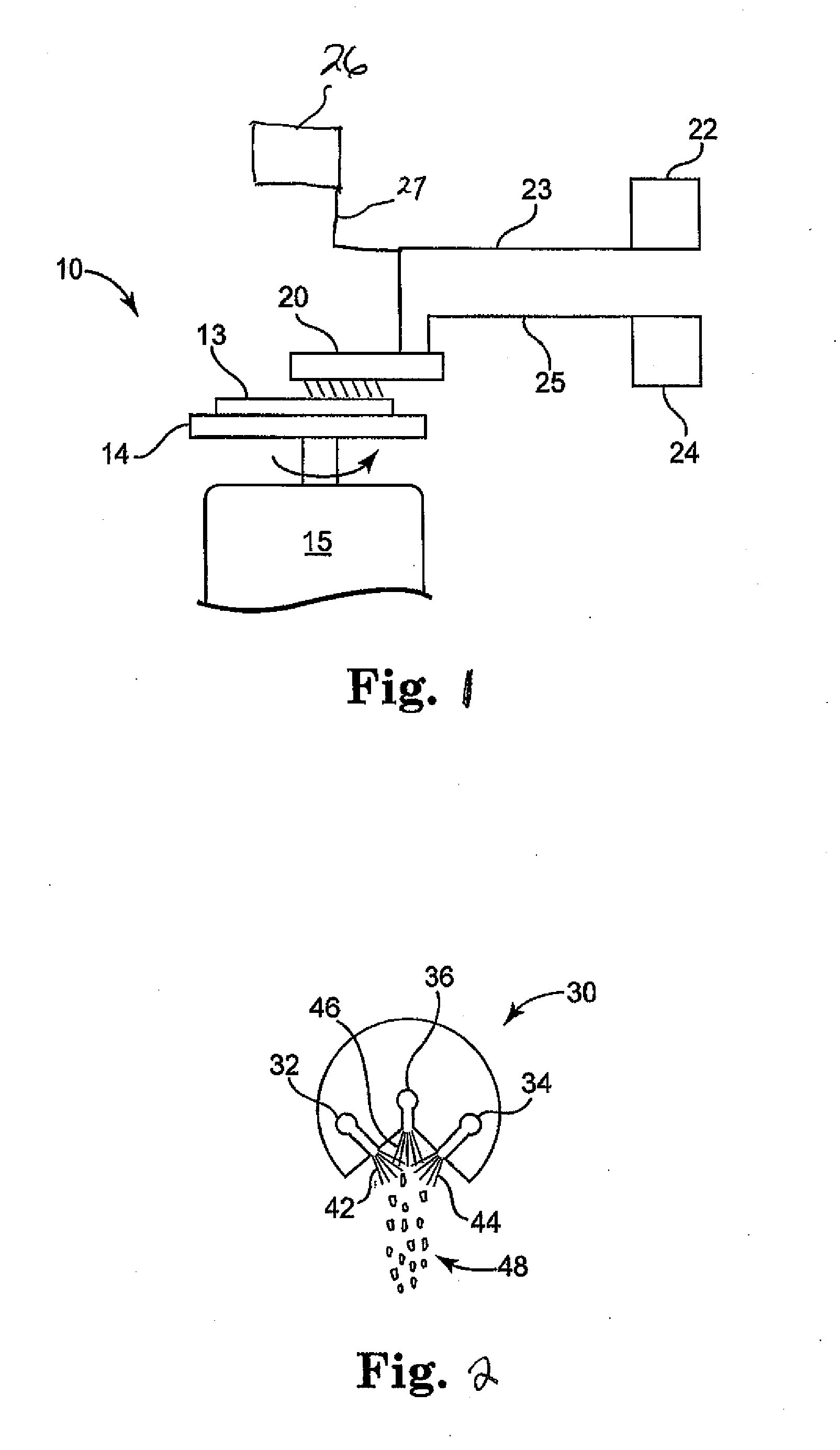

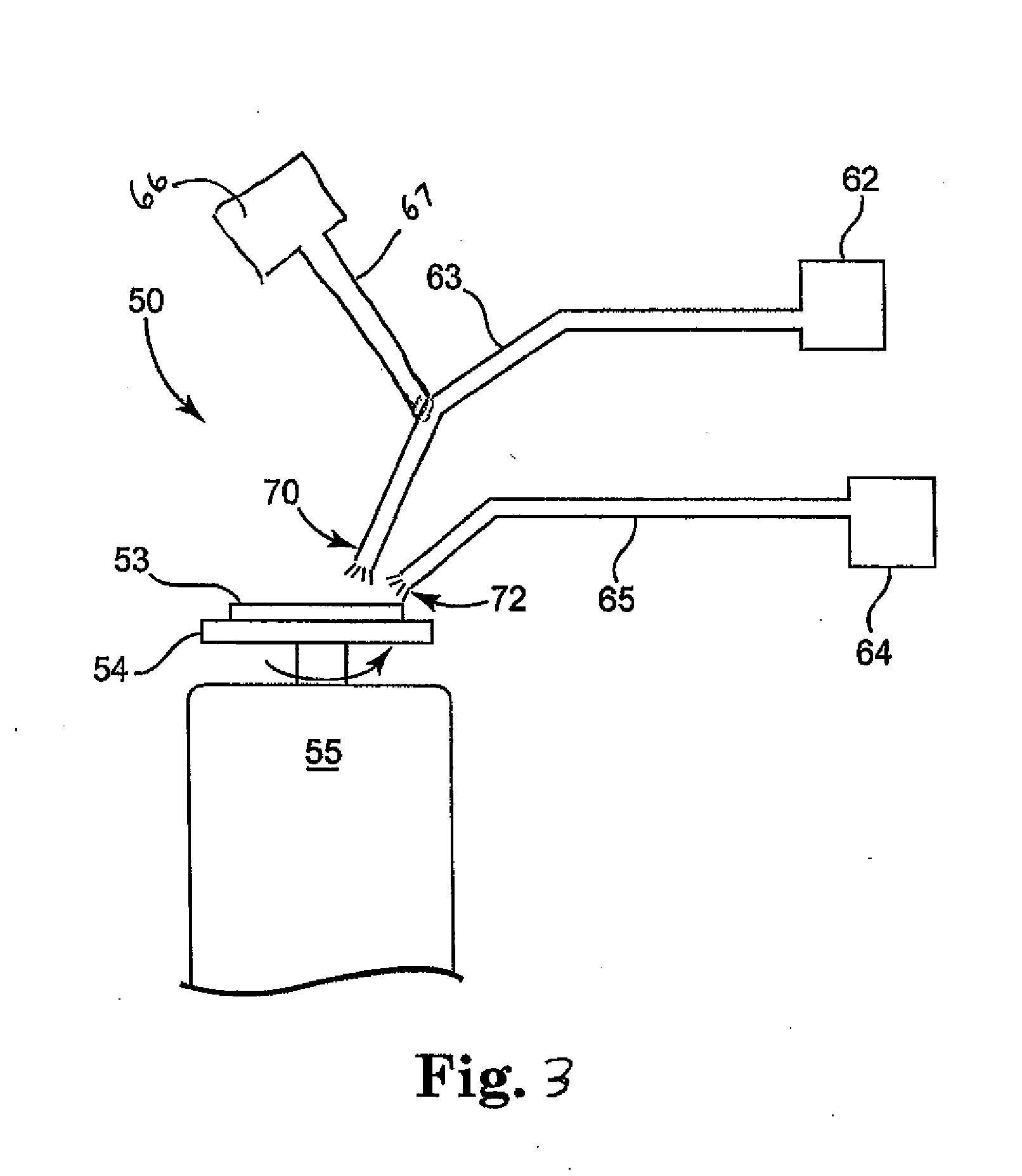

ActiveUS20100055924A1Facilitated DiffusionIncrease etch rateDecorative surface effectsSemiconductor/solid-state device manufacturingLiquid layerThin layer

Chemical etching methods and associated modules for performing the removal of metal from the edge bevel region of a semiconductor wafer are described. The methods and systems provide the thin layer of pre-rinsing liquid before applying etchant at the edge bevel region of the wafer. The etchant is less diluted and diffuses faster through a thinned layer of rinsing liquid. An edge bevel removal embodiment involving that is particularly effective at reducing process time, narrowing the metal taper and allowing for subsequent chemical mechanical polishing, is disclosed.

Owner:NOVELLUS SYSTEMS

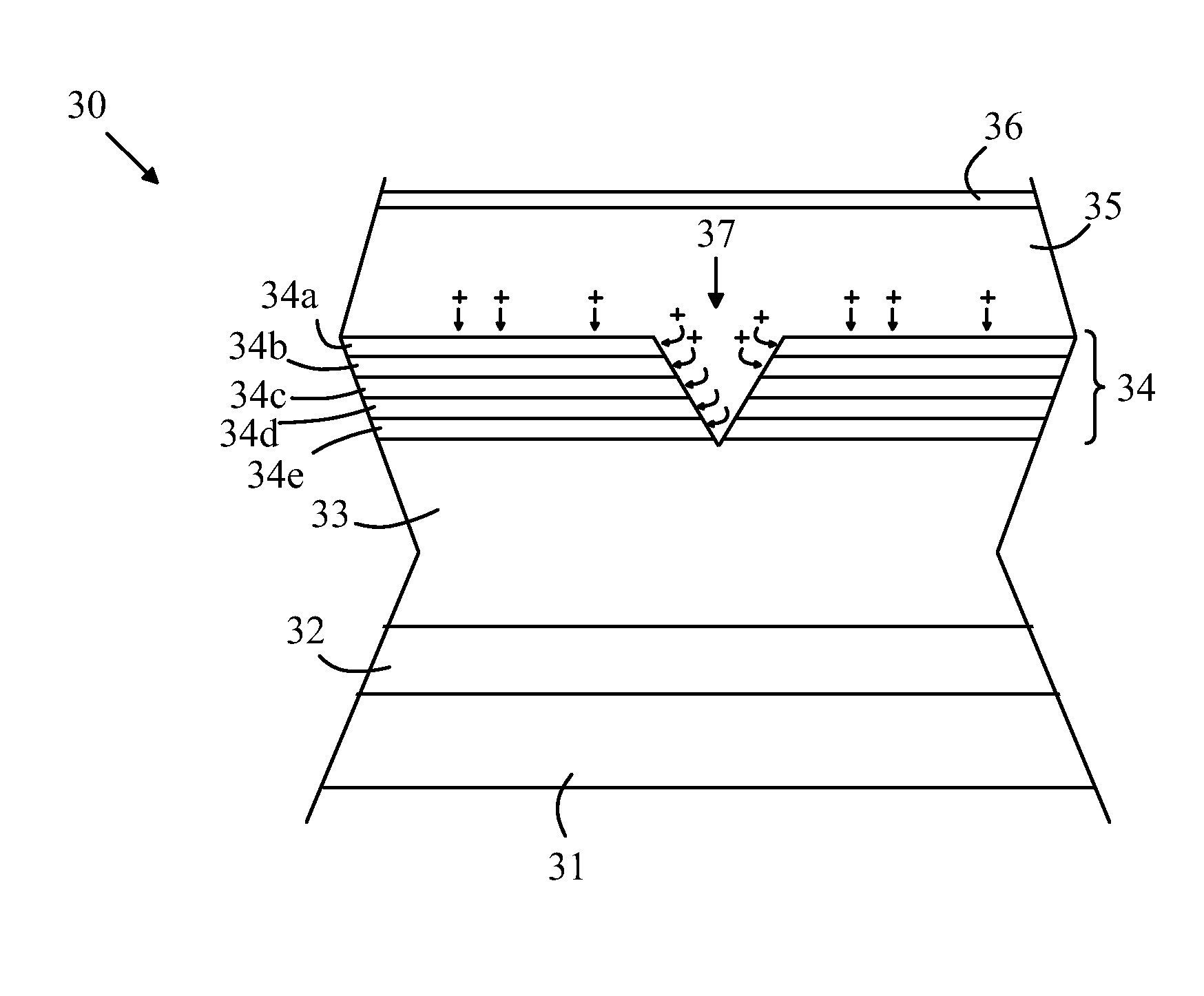

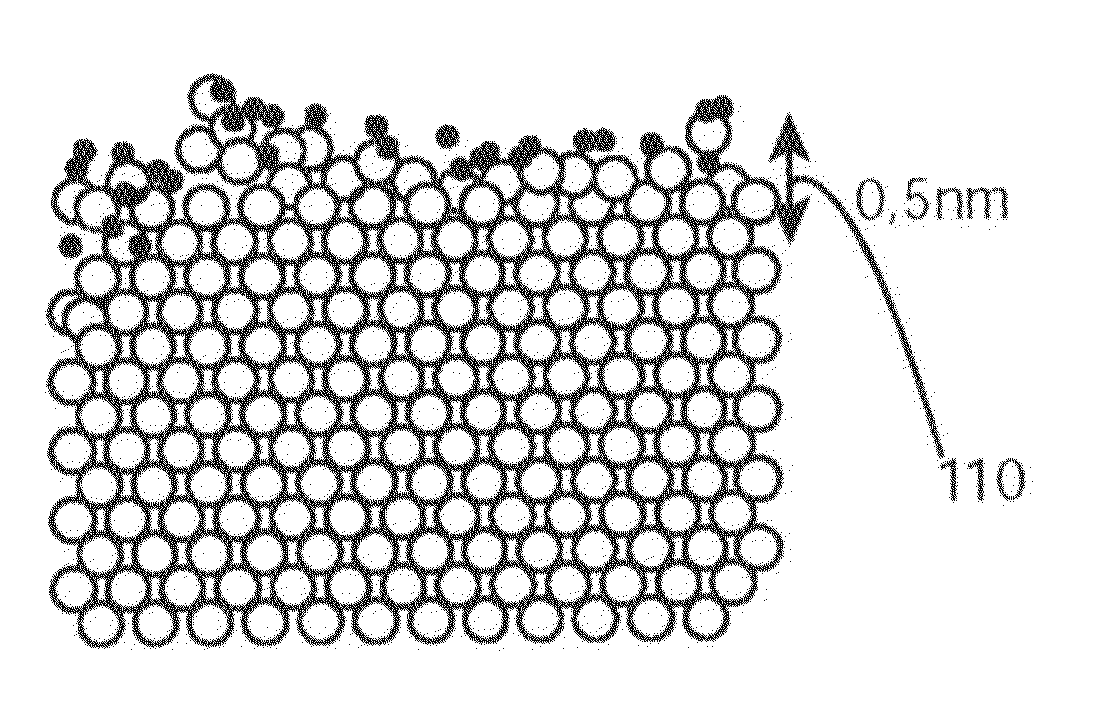

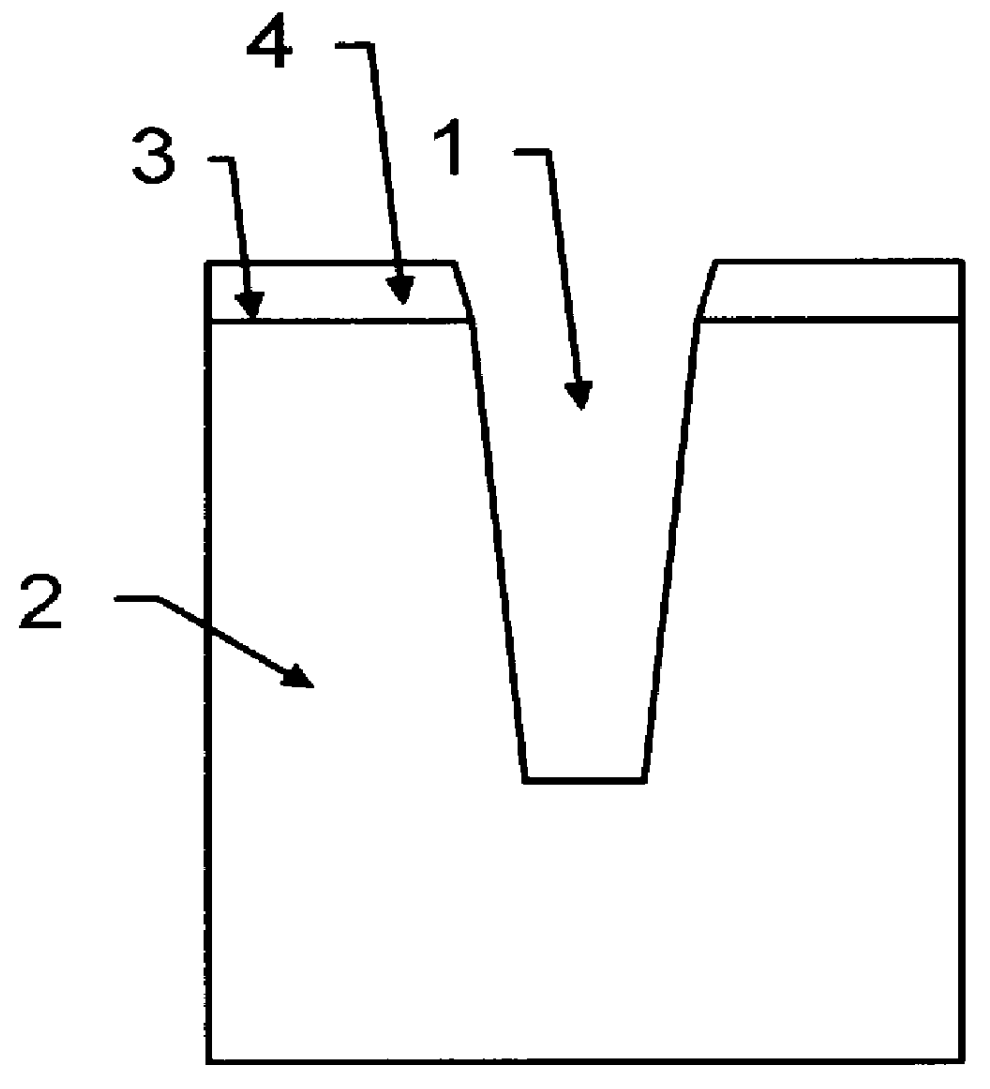

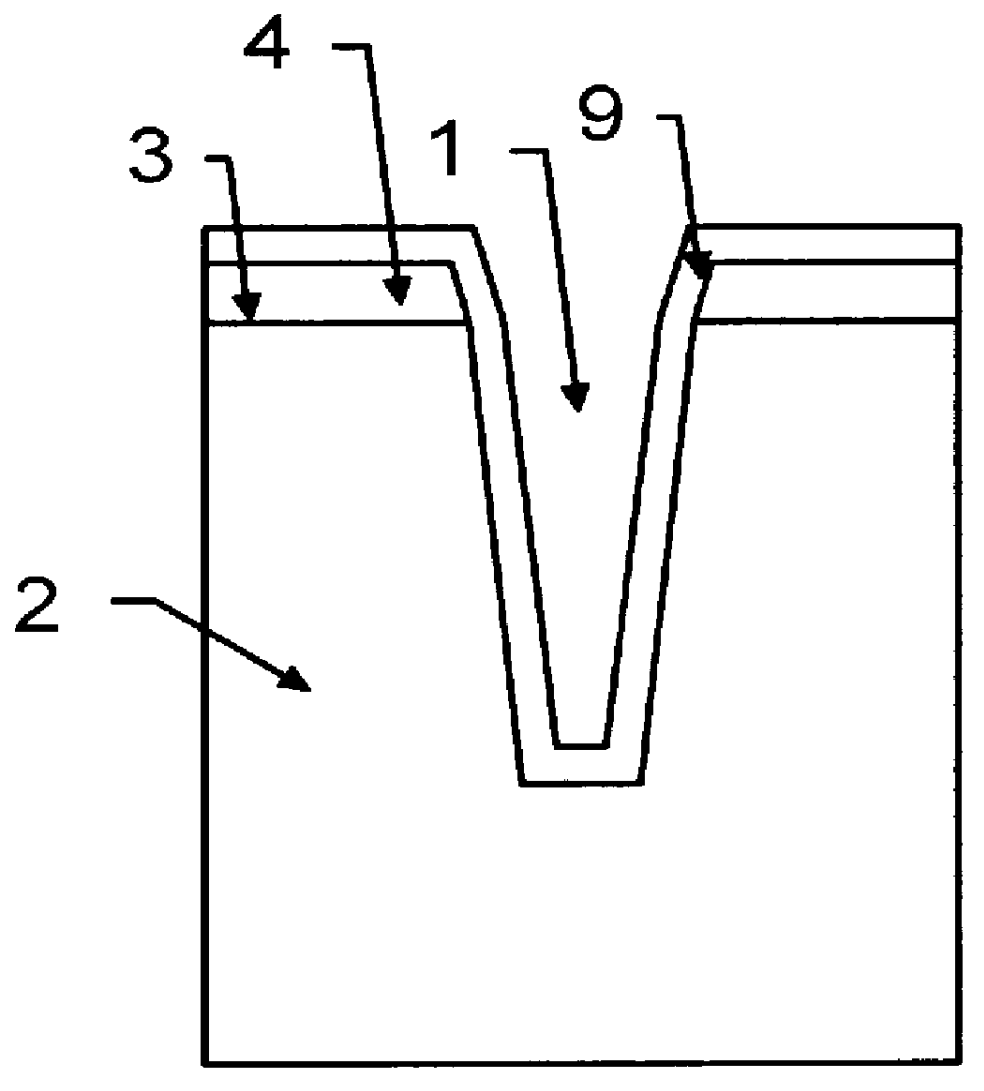

LED with Improved Injection Efficiency

ActiveUS20110121357A1Fast etchSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsActive layer

A light emitting device and method for making the same is disclosed. The light-emitting device includes an active layer sandwiched between a p-type semiconductor layer and an n-type semiconductor layer. The active layer emits light when holes from the p-type semiconductor layer combine with electrons from the n-type semiconductor layer therein. The active layer includes a number of sub-layers and has a plurality of pits in which the side surfaces of a plurality of the sub-layers are in contact with the p-type semiconductor material such that holes from the p-type semiconductor material are injected into those sub-layers through the exposed side surfaces without passing through another sub-layer. The pits can be formed by utilizing dislocations in the n-type semiconductor layer and etching the active layer using an etching atmosphere in the same chamber used to deposit the semiconductor layers without removing the partially fabricated device.

Owner:SAMSUNG ELECTRONICS CO LTD

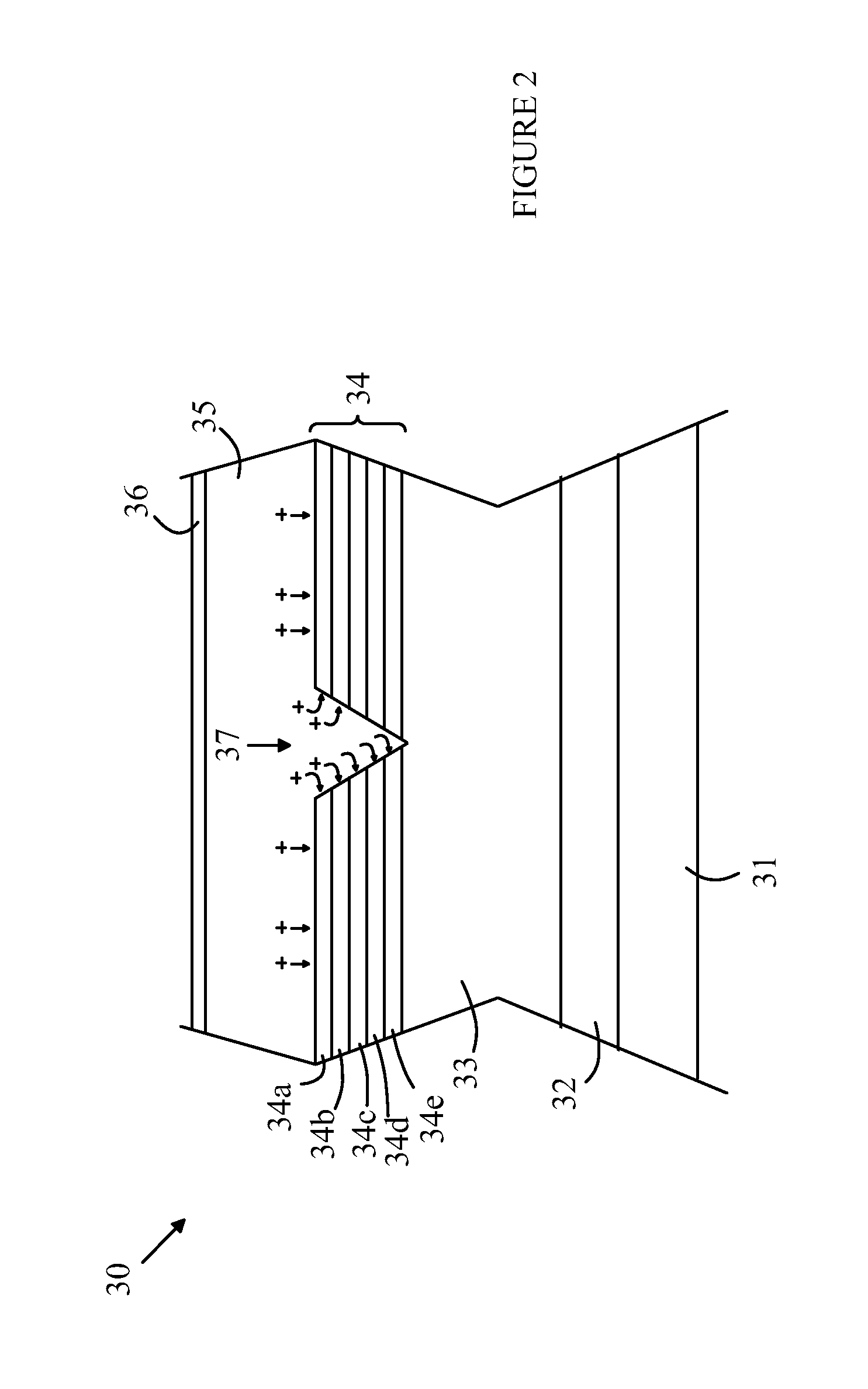

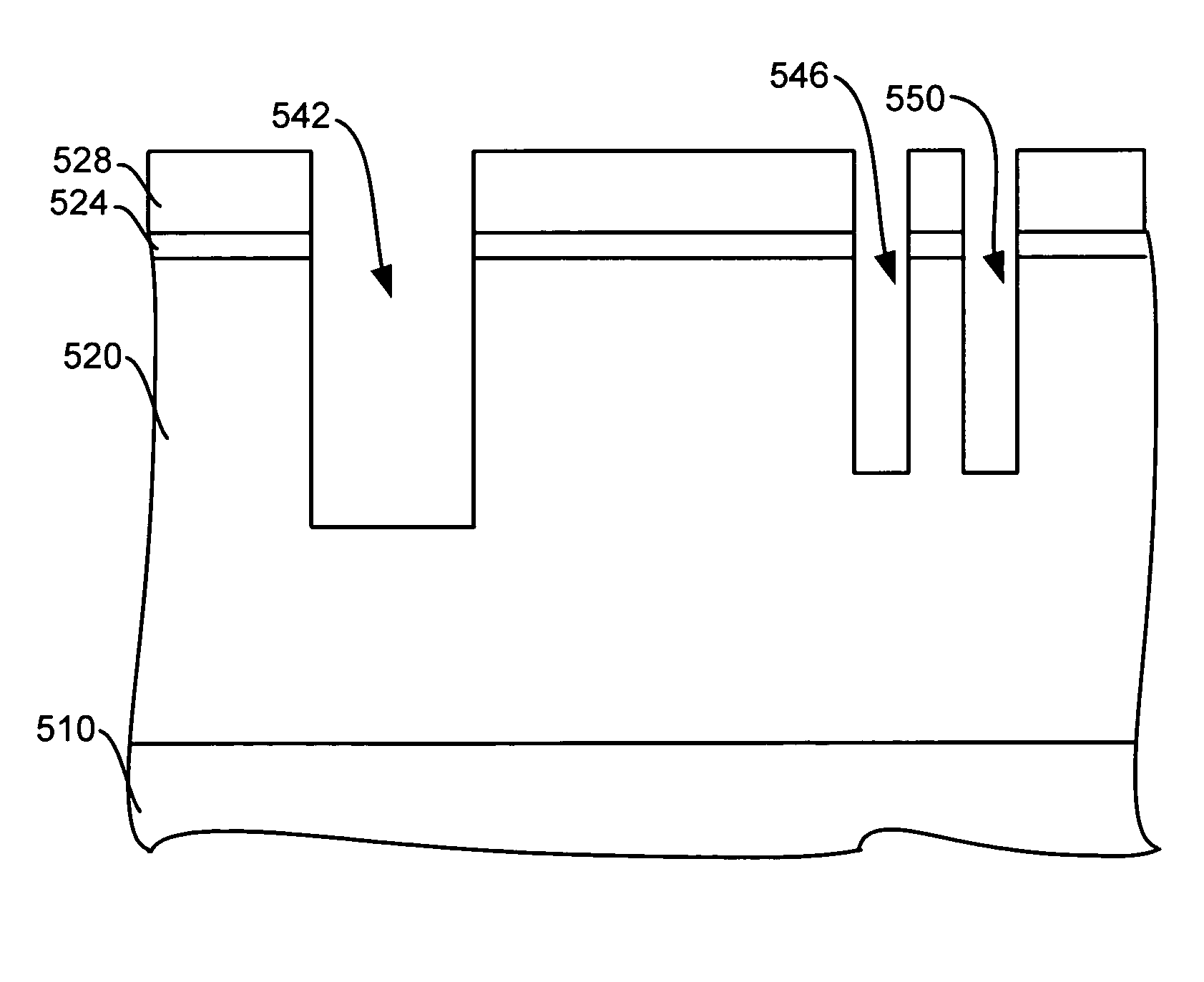

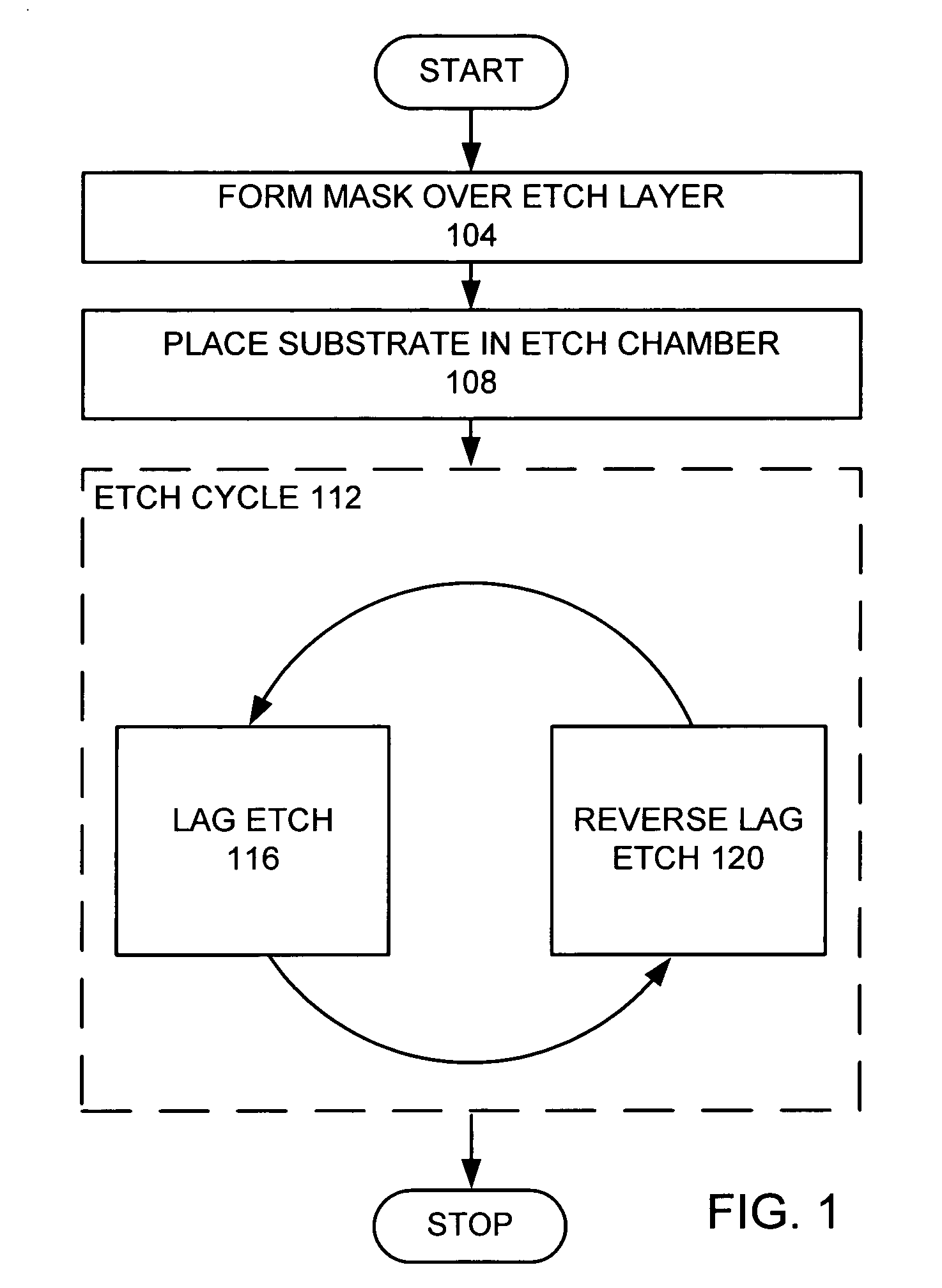

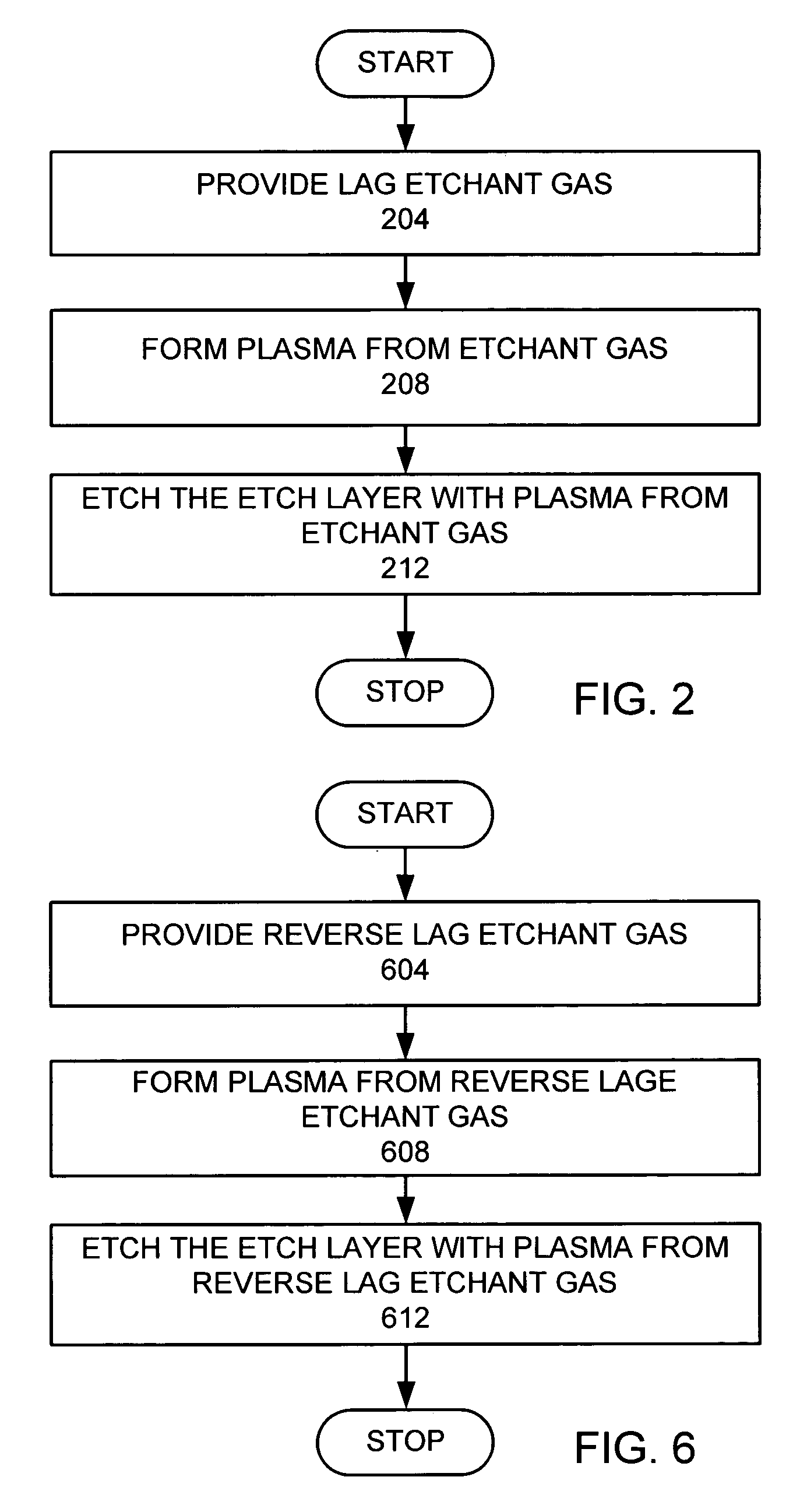

Lag control

ActiveUS7307025B1Small featureFast etchSemiconductor/solid-state device manufacturingOptoelectronicsSilicon oxide

A method for etching features in a silicon oxide based dielectric layer over a substrate, comprising performing an etch cycle. A lag etch partially etching features in the silicon oxide based dielectric layer is performed, comprising providing a lag etchant gas, forming a plasma from the lag etchant gas, and etching the etch layer with the lag etchant gas, so that smaller features are etched slower than wider features. A reverse lag etch further etching the features in the silicon oxide based dielectric layer is performed comprising providing a reverse lag etchant gas, which is different from the lag etchant gas and is more polymerizing than the lag etchant gas, forming a plasma from the reverse lag etchant gas, and etching the silicon oxide based dielectric layer with the plasma formed from the reverse lag etchant gas, so that smaller features are etched faster than wider features.

Owner:LAM RES CORP

Deep reactive ion etching process and microelectromechanical devices formed thereby

InactiveUS7077007B2Uniform widthConstant gap widthAcceleration measurement using interia forcesDecorative surface effectsDevice formEngineering

A process for forming a microelectromechanical system (MEMS) device by a deep reactive ion etching (DRIE) process during which a substrate overlying a cavity is etched to form trenches that breach the cavity to delineate suspended structures. A first general feature of the process is to define suspended structures with a DRIE process, such that the dimensions desired for the suspended structures are obtained. A second general feature is the proper location of specialized features, such as stiction bumps, vulnerable to erosion caused by the DRIE process. Yet another general feature is to control the environment surrounding suspended structures delineated by DRIE in order to obtain their desired dimensions. A significant problem identified and solved by the invention is the propensity for the DRIE process to etch certain suspended features at different rates. In addition to etching wider trenches more rapidly than narrower trenches, the DRIE process erodes suspended structures more rapidly at greater distances from anchor sites of the substrate being etched. At the masking level, the greater propensity for backside and lateral erosion of certain structures away from substrate anchor sites is exploited so that, at the completion of the etch process, suspended structures have acquired their respective desired widths.

Owner:GOOGLE LLC

Chemical etching solution for titanium and titanium alloy

A chemical etching solution used in Ti and Ti alloys characterizes that it is composed of H2F2, HNO3 and water, their volume percentage is: H2F2 5-15% HNO3 8-35%, water 50-85%, which can be used under normal temperature having the advantages of quick corrosion, small side corrosion, long life time of the solution and low process cost.

Owner:OCEAN UNIV OF CHINA

Plasma etching process

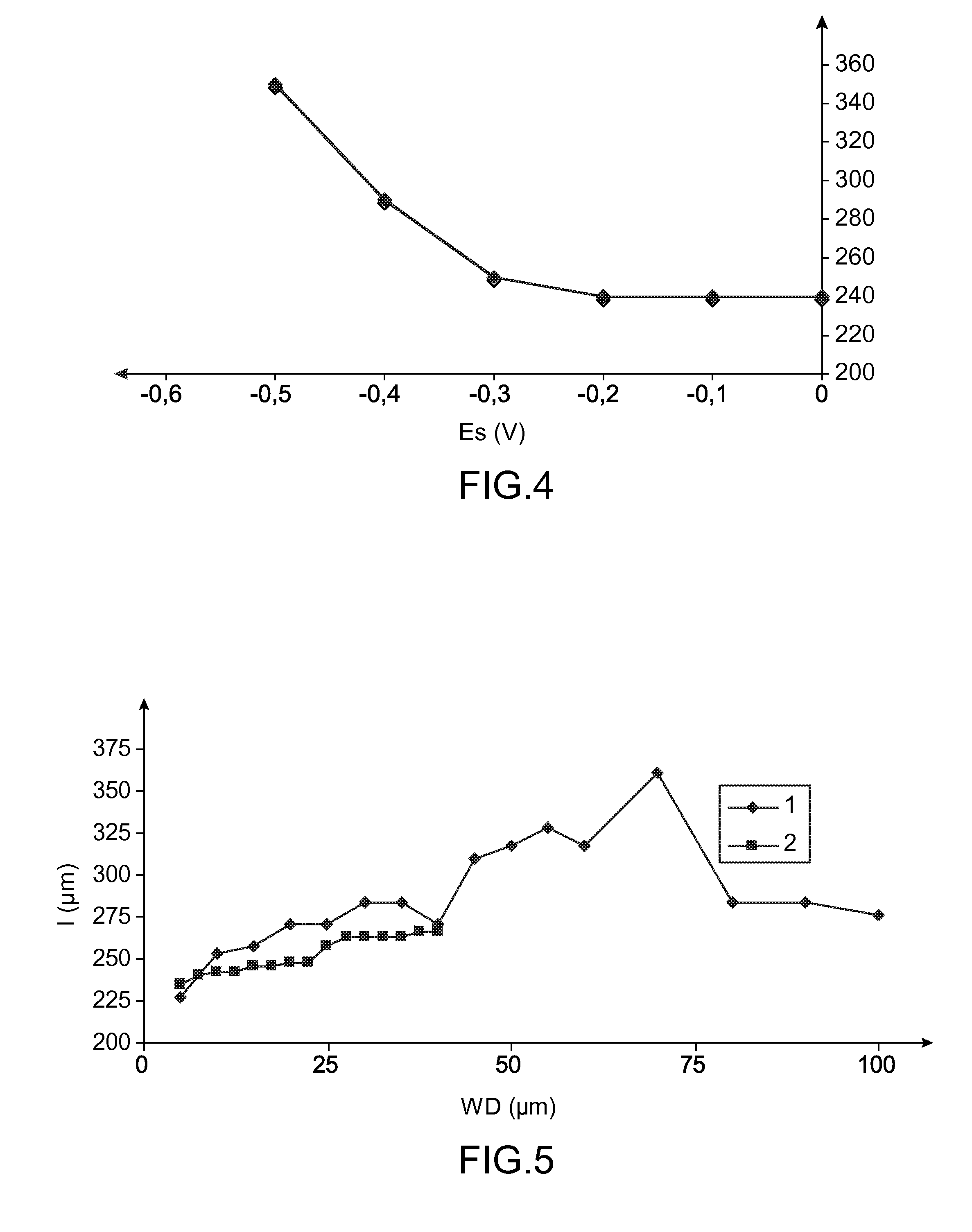

ActiveUS20150228495A1Easy to controlImprove etching precisionSemiconductor/solid-state device manufacturingReactive gasGas plasma

A method and system are provided for etching a layer to be etched in a plasma etching reactor, including: forming a reactive layer by injection of at least one reactive gas to form a reactive gas plasma, which forms, together with the layer to be etched, a reactive layer which goes into the layer to be etched during etching of said layer to be etched, wherein the reactive layer reaches a steady state thickness upon completion of a determined duration of said injection; said injection being interrupted before said determined duration has elapsed so that, upon completion of the forming of the reactive layer, the thickness of the reactive layer is smaller than said steady state thickness; and removing the reactive layer by injection of at least one inert gas to form an inert gas plasma, which makes it possible to remove only the reactive layer.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES +1

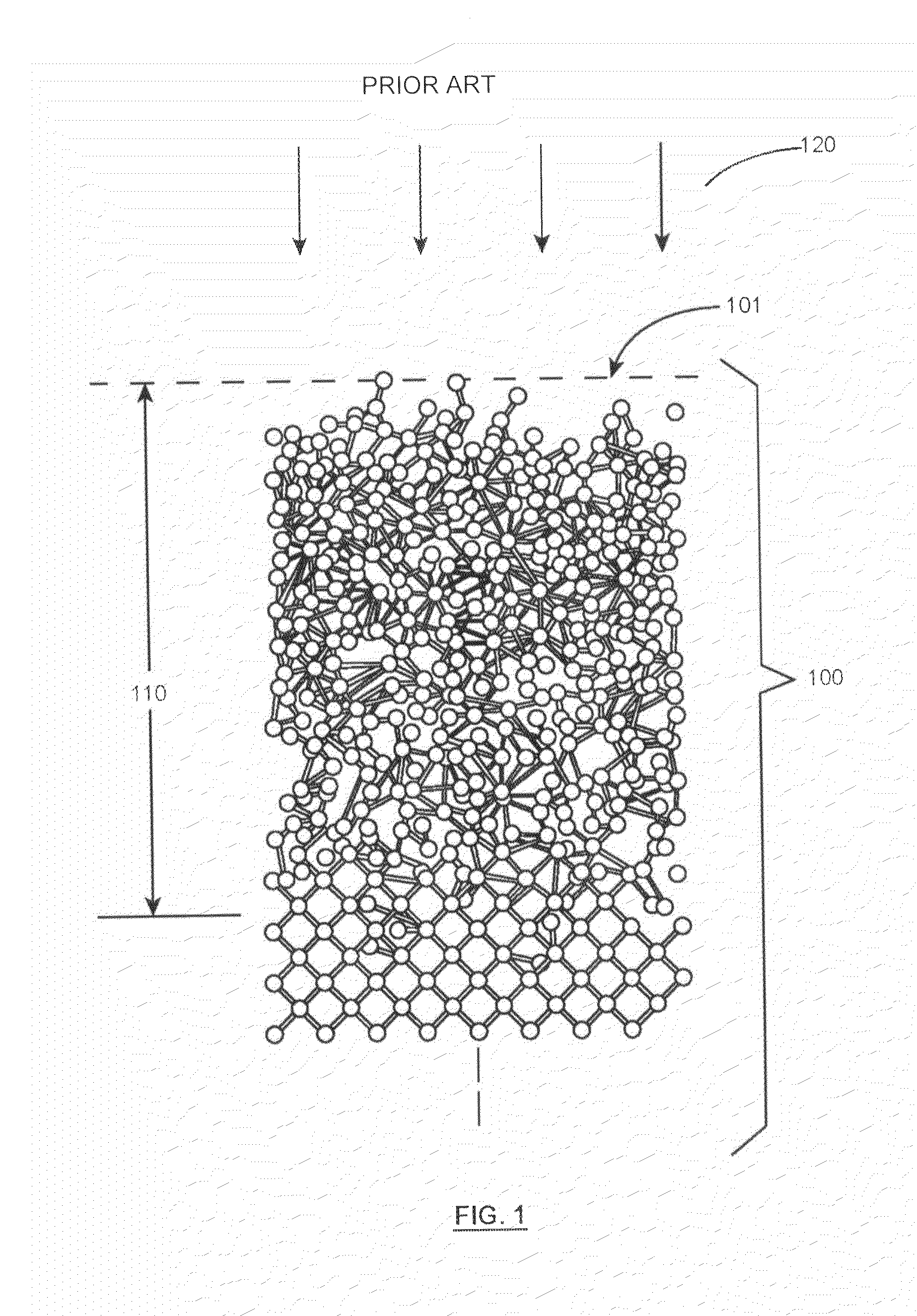

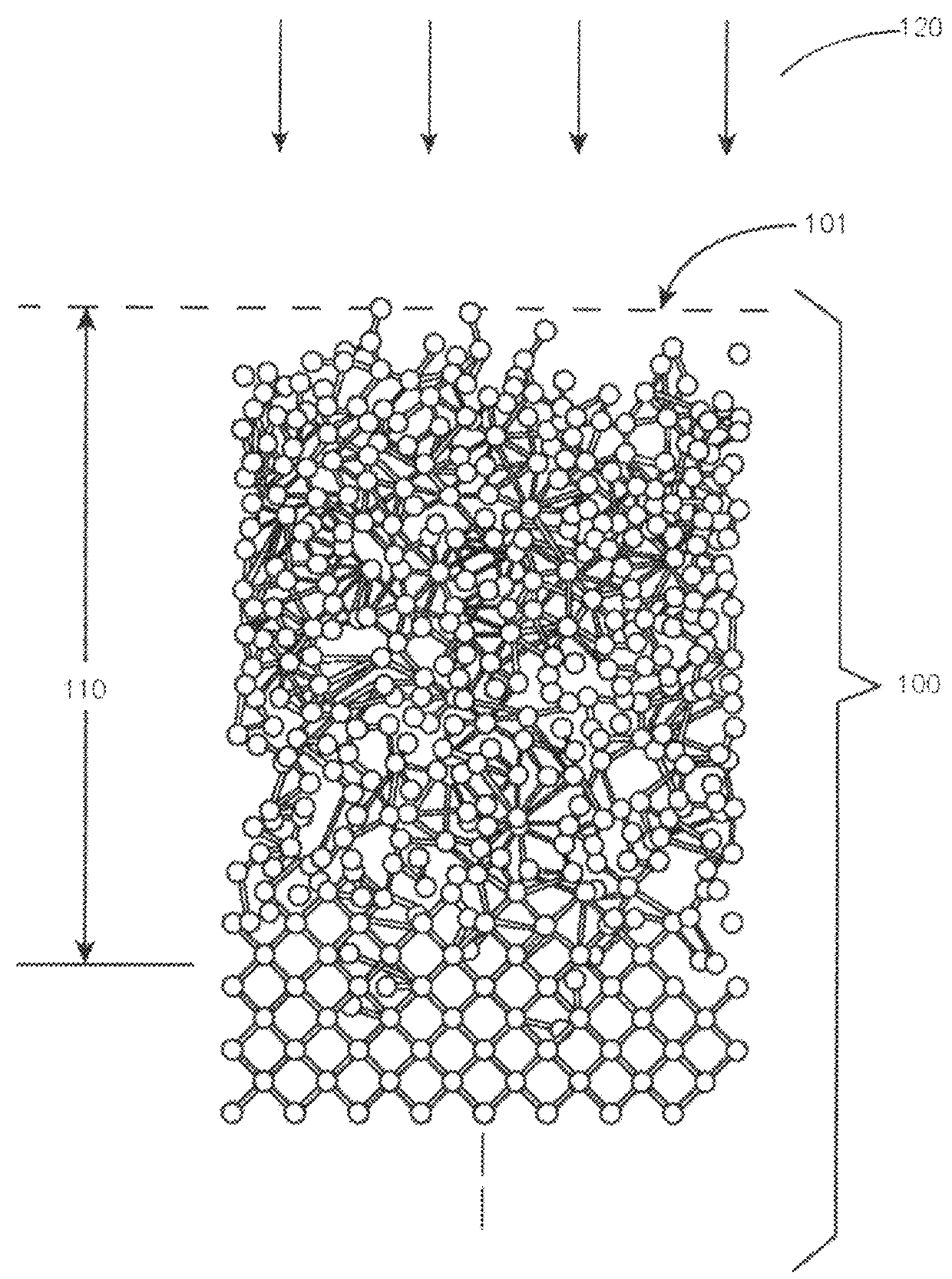

Texturing and cleaning medium for the surface treatment of wafers and use thereof

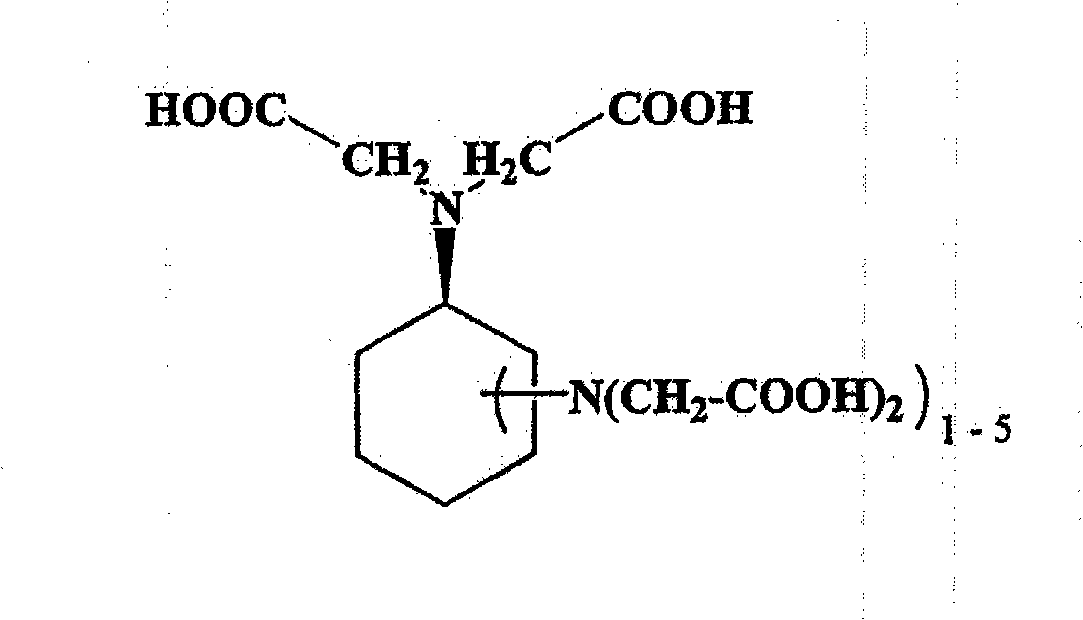

InactiveCN101952406AFacilitated DiffusionFast etchDetergent mixture composition preparationOrganic non-surface-active detergent compositionsSimple Organic CompoundsWafering

The invention relates to a fluid medium for the surface treatment of monocrystalline wafers, which contains an alkaline etching agent and at least one organic compound with low volatility. Systems of this type can be used either for cleaning, the removal of defects and the texturing of wafer surfaces in a single etching step or, exclusively, for the texturing of silicon wafers having different surface qualities, such as wafers which are cut by a wire saw and exhibit high surface degradation or chemically polished surfaces having a minimal number of defects.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

Process for selectively removing nitride from substrates

ActiveUS20120145672A1High removal rateFacilitate useDecorative surface effectsSemiconductor/solid-state device manufacturingPhosphoric acidSilicon nitride

A method of selectively removing silicon nitride from a substrate comprises providing a substrate having silicon nitride on a surface thereof; and dispensing phosphoric acid and sulfuric acid onto the surface of the substrate as a mixed acid liquid stream at a temperature greater than about 150° C. In this method, water is added to a liquid solution of the mixed acid liquid stream as or after the liquid solution of the mixed acid liquid stream passes through a nozzle.

Owner:TEL EPION

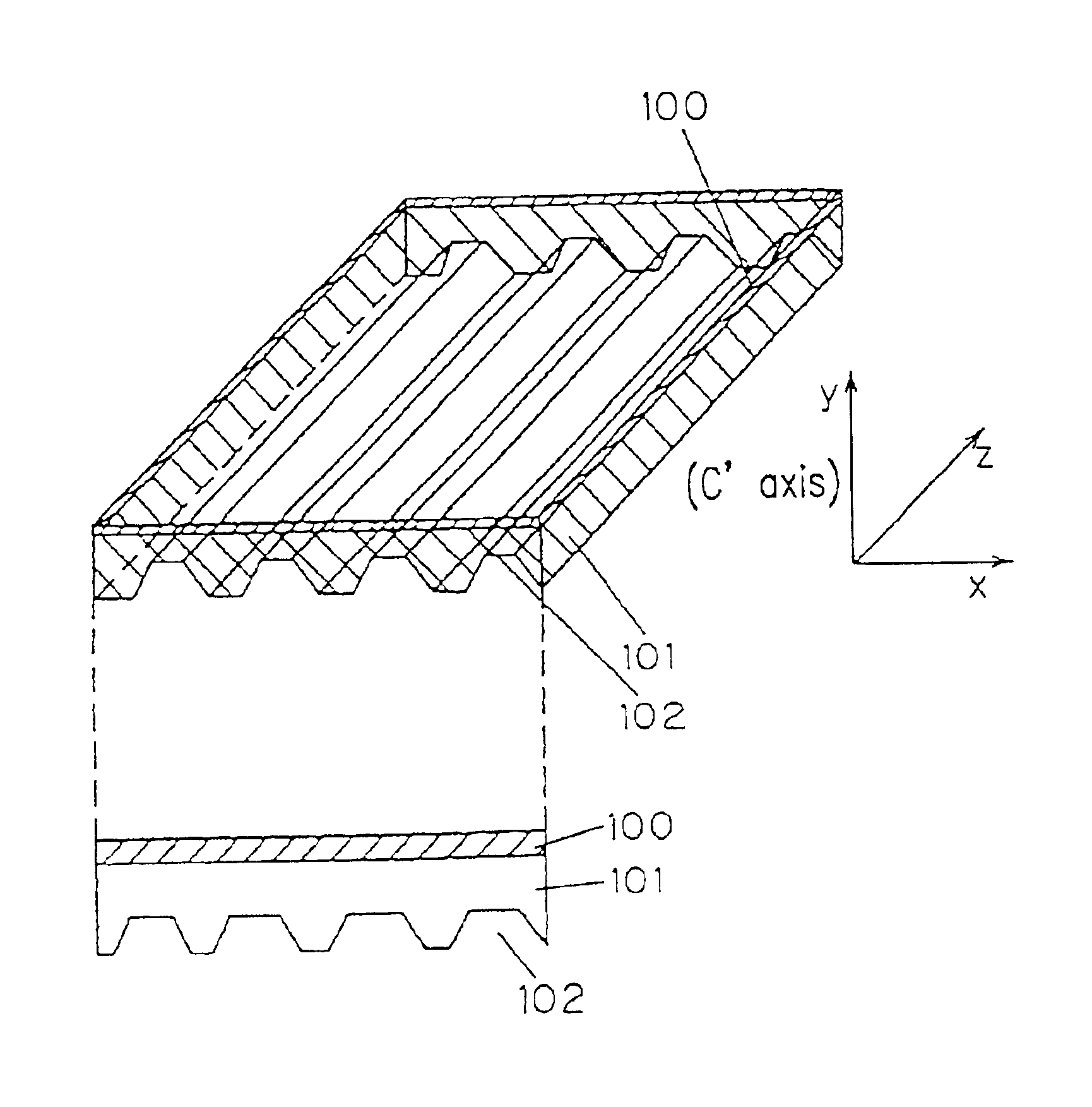

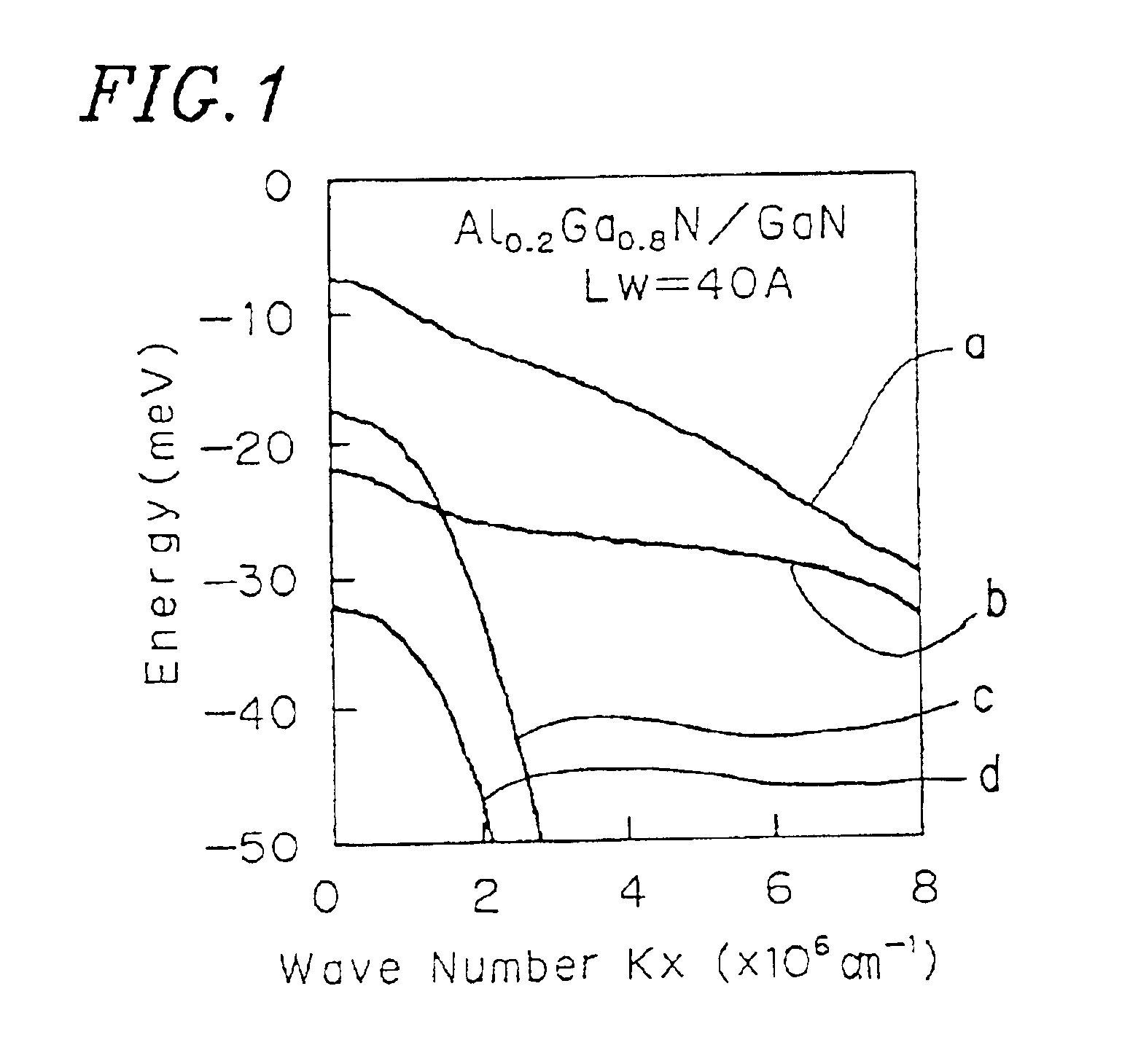

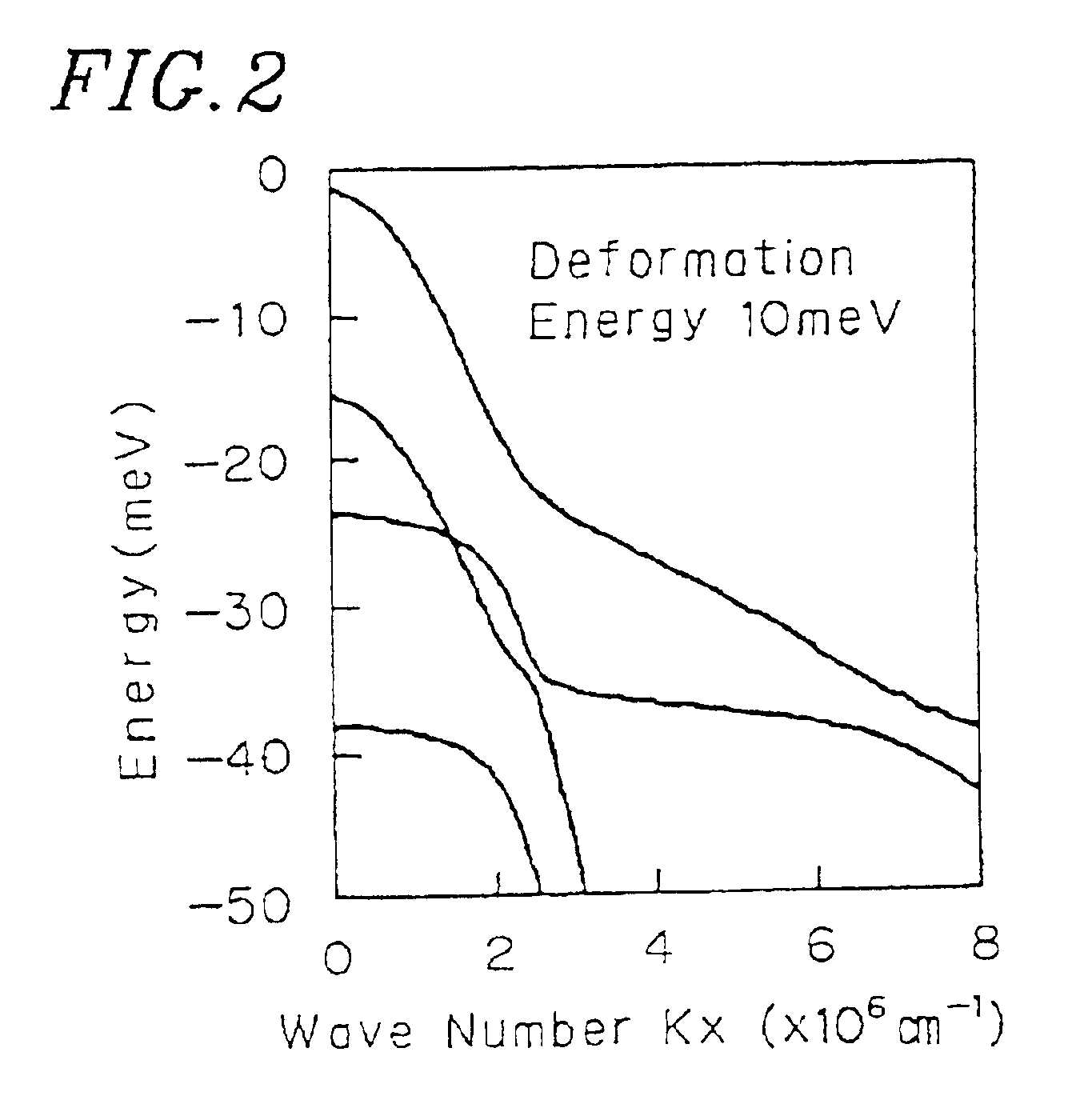

Semiconductor light emitting element and method for fabricating the same

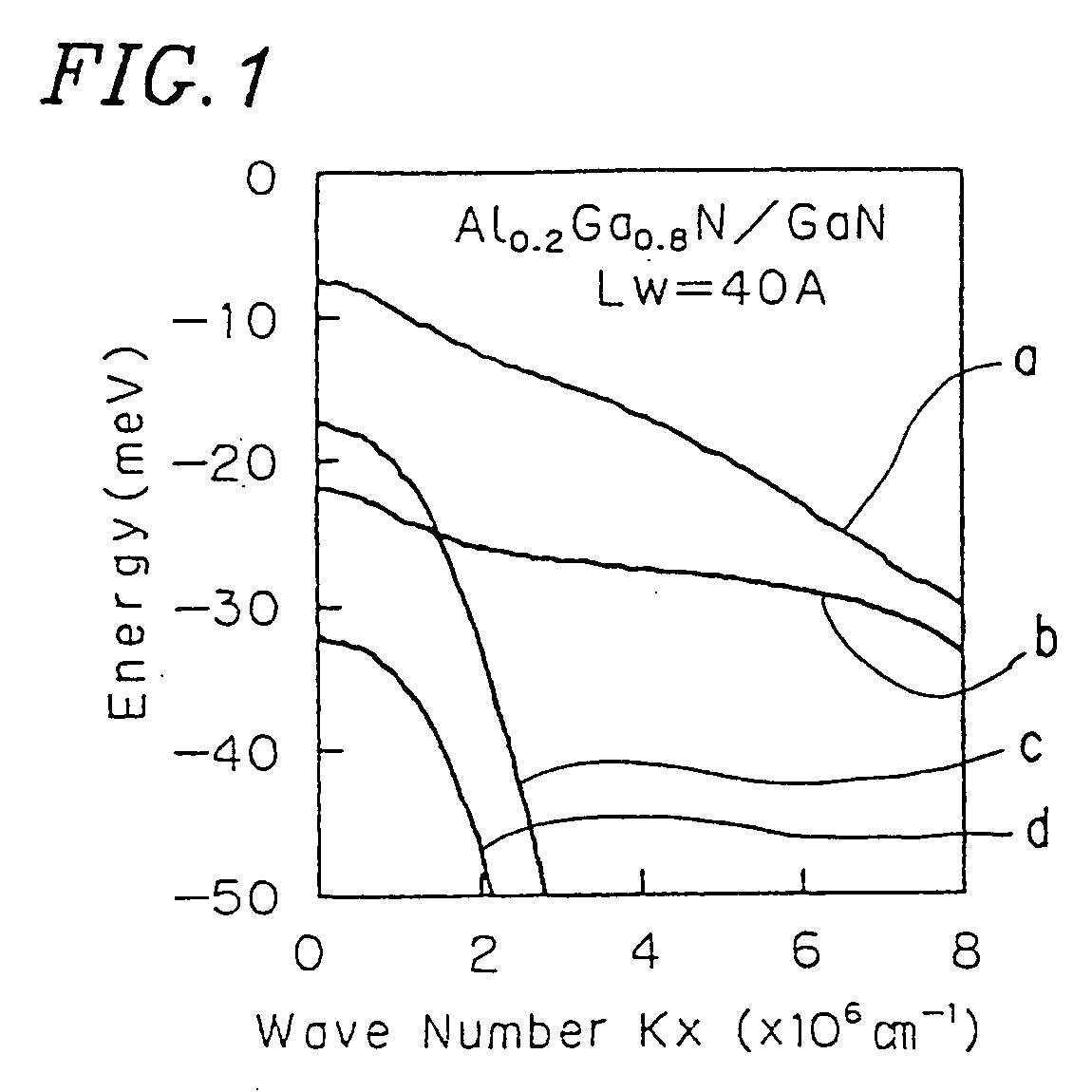

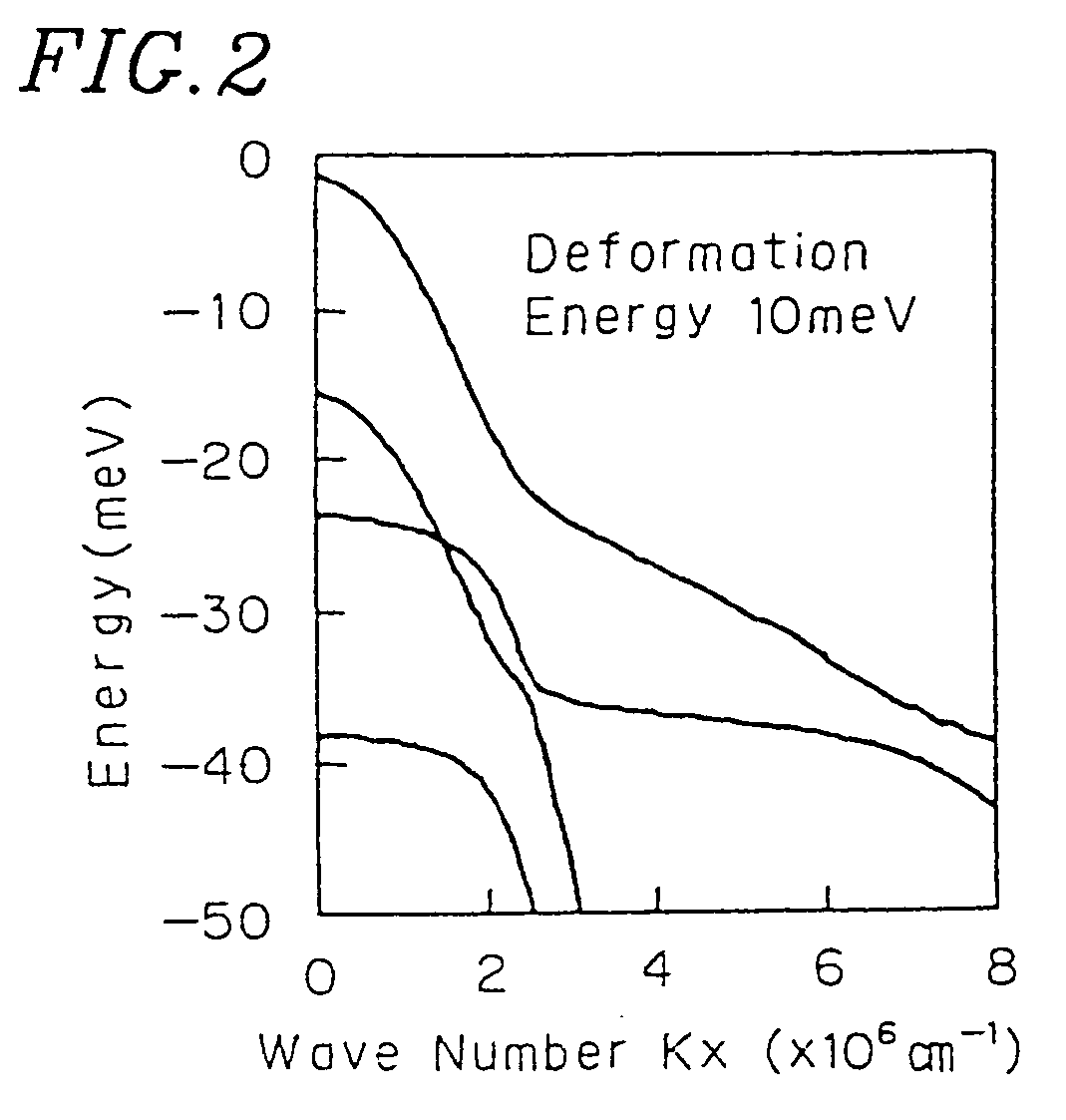

InactiveUS6861672B2Fast etchImprove performanceOptical wave guidanceLaser detailsAnisotropic strainActive layer

The semiconductor laser of this invention includes an active layer formed in a c-axis direction, wherein the active layer is made of a hexagonal-system compound semiconductor, and anisotropic strain is generated in a c plane of the active layer.

Owner:PANASONIC CORP

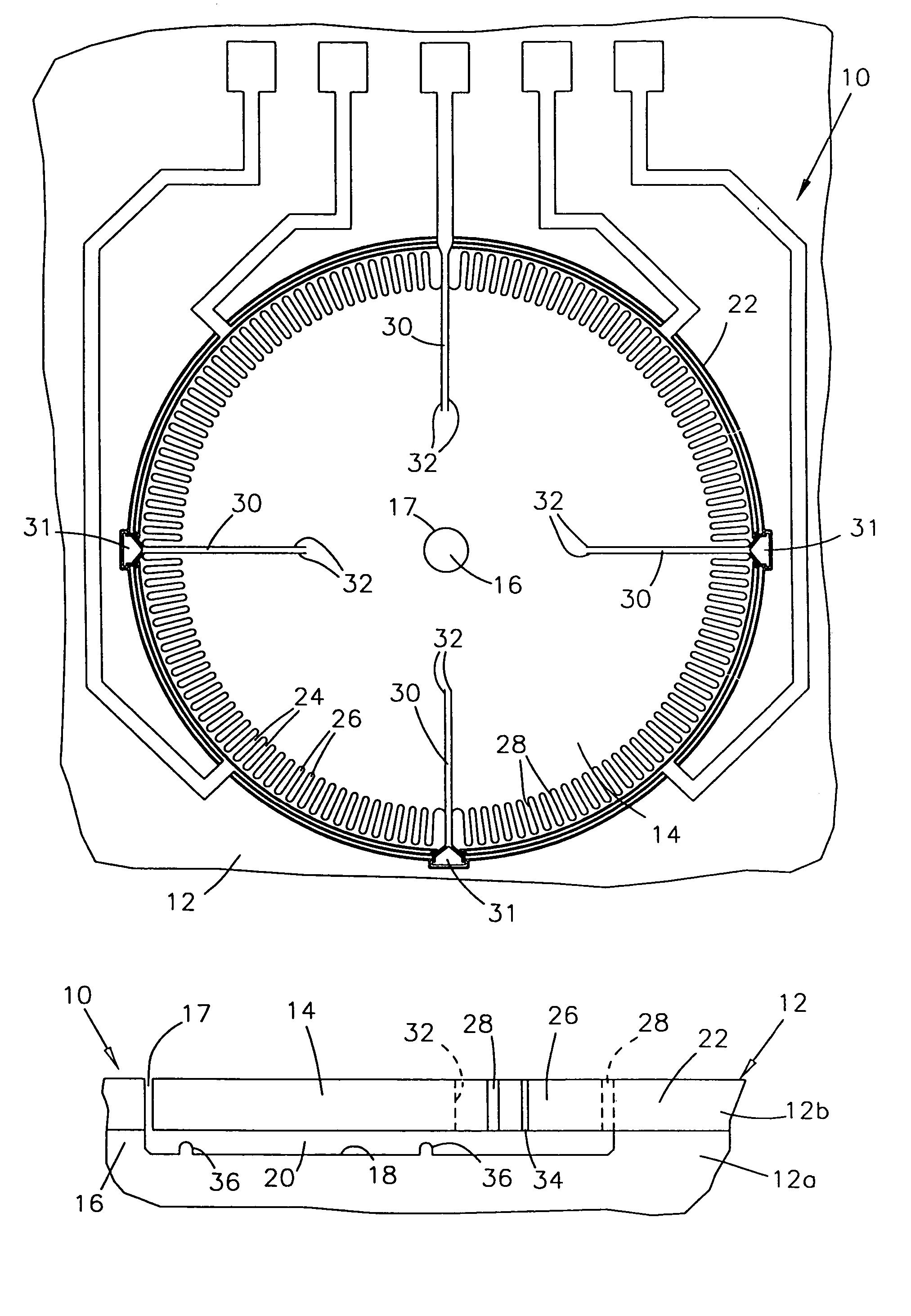

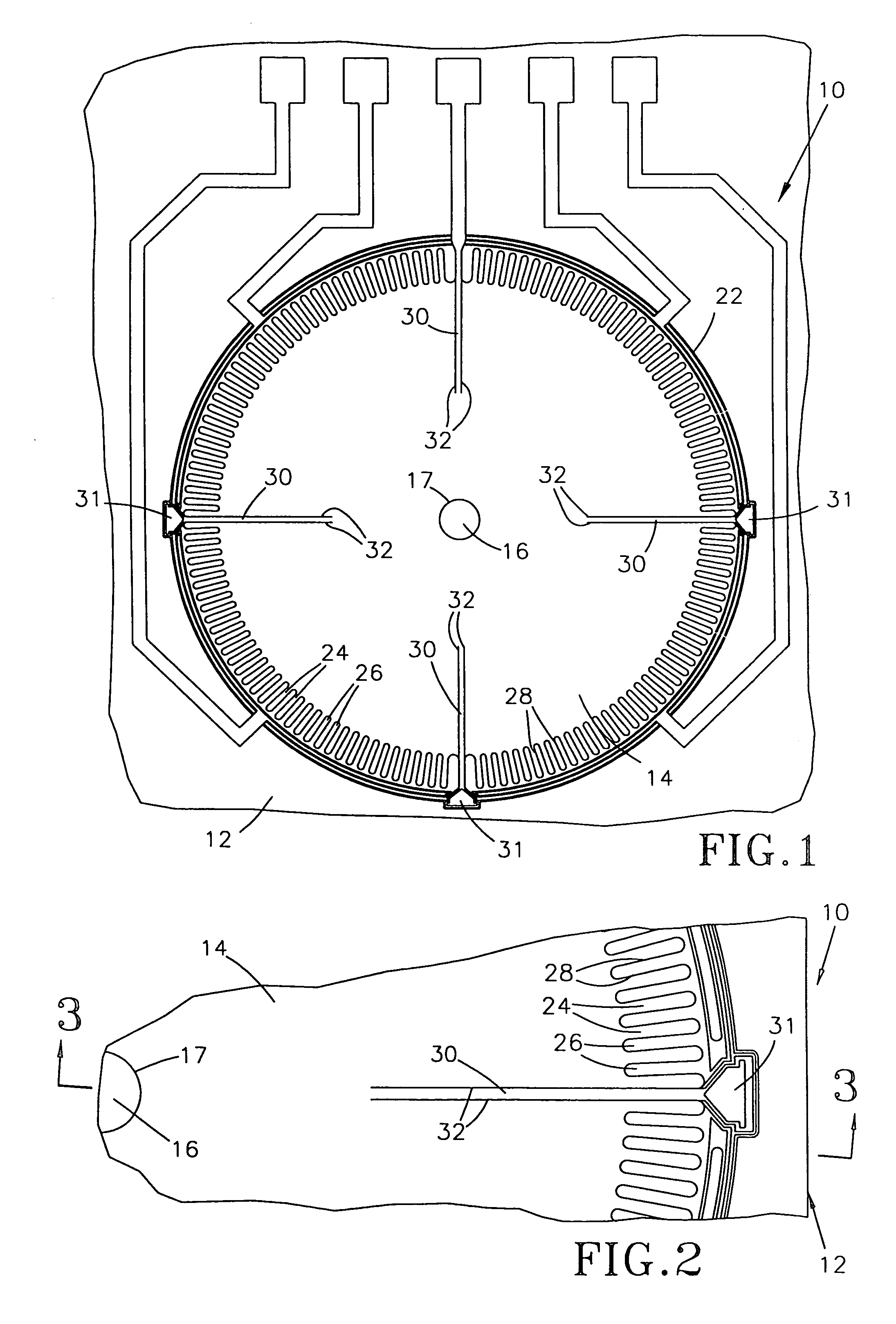

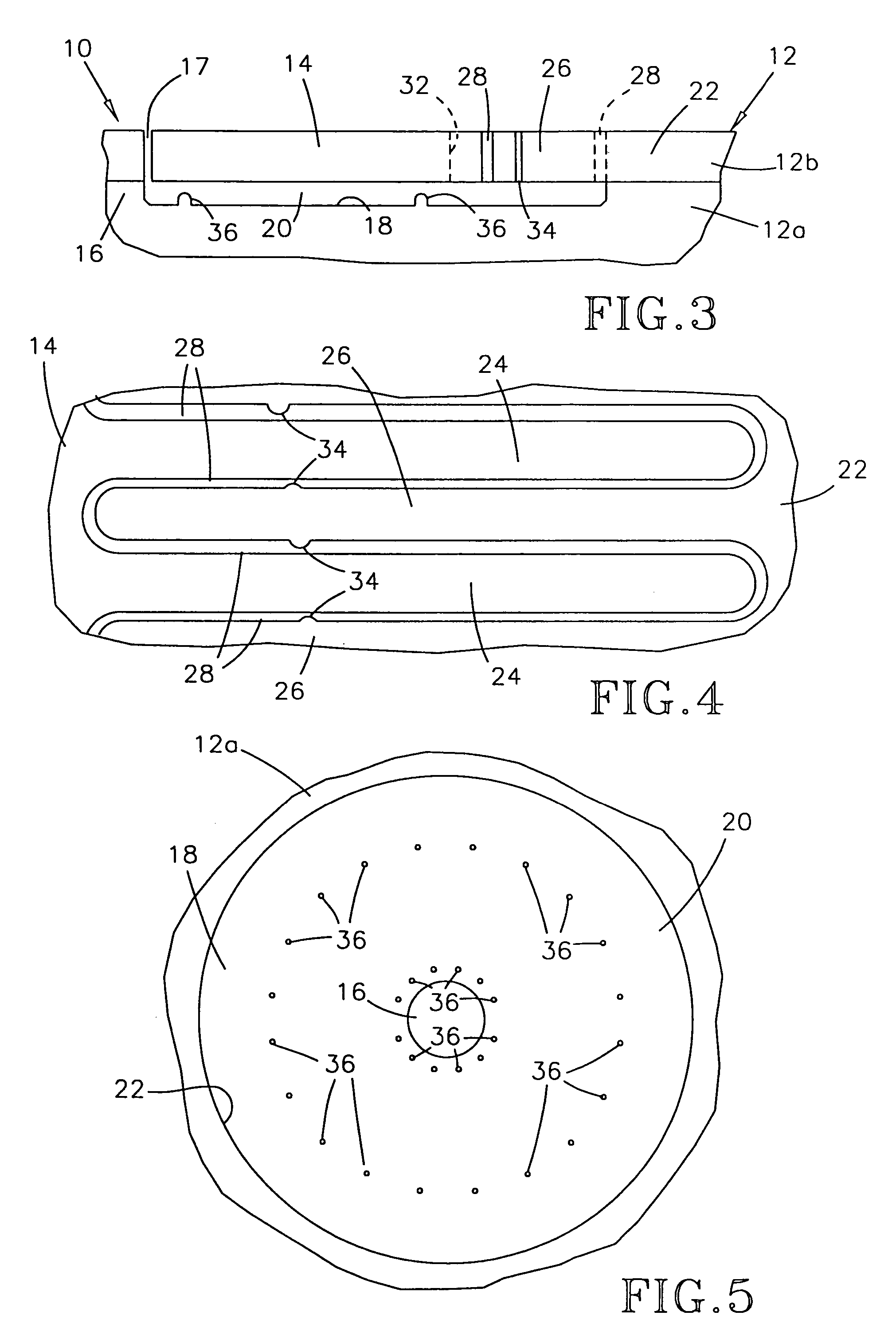

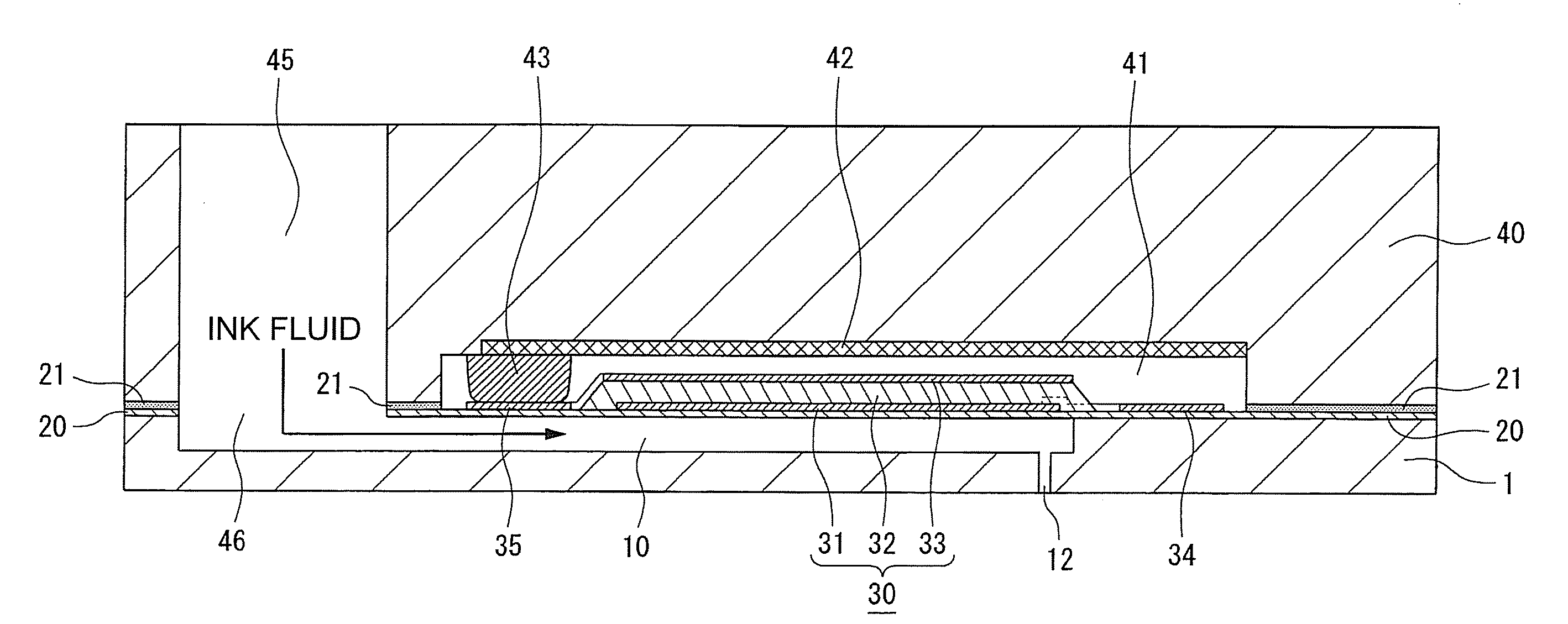

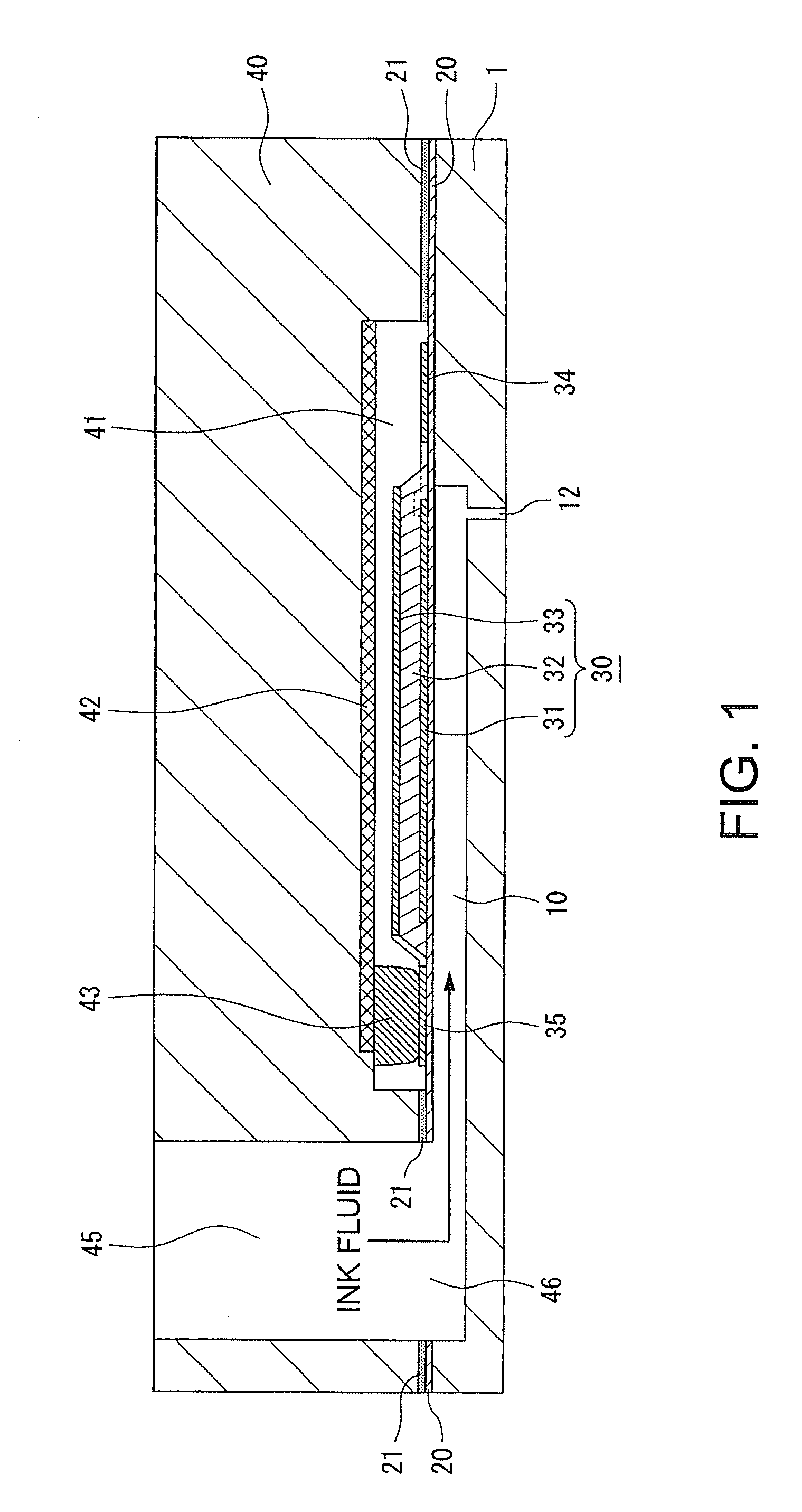

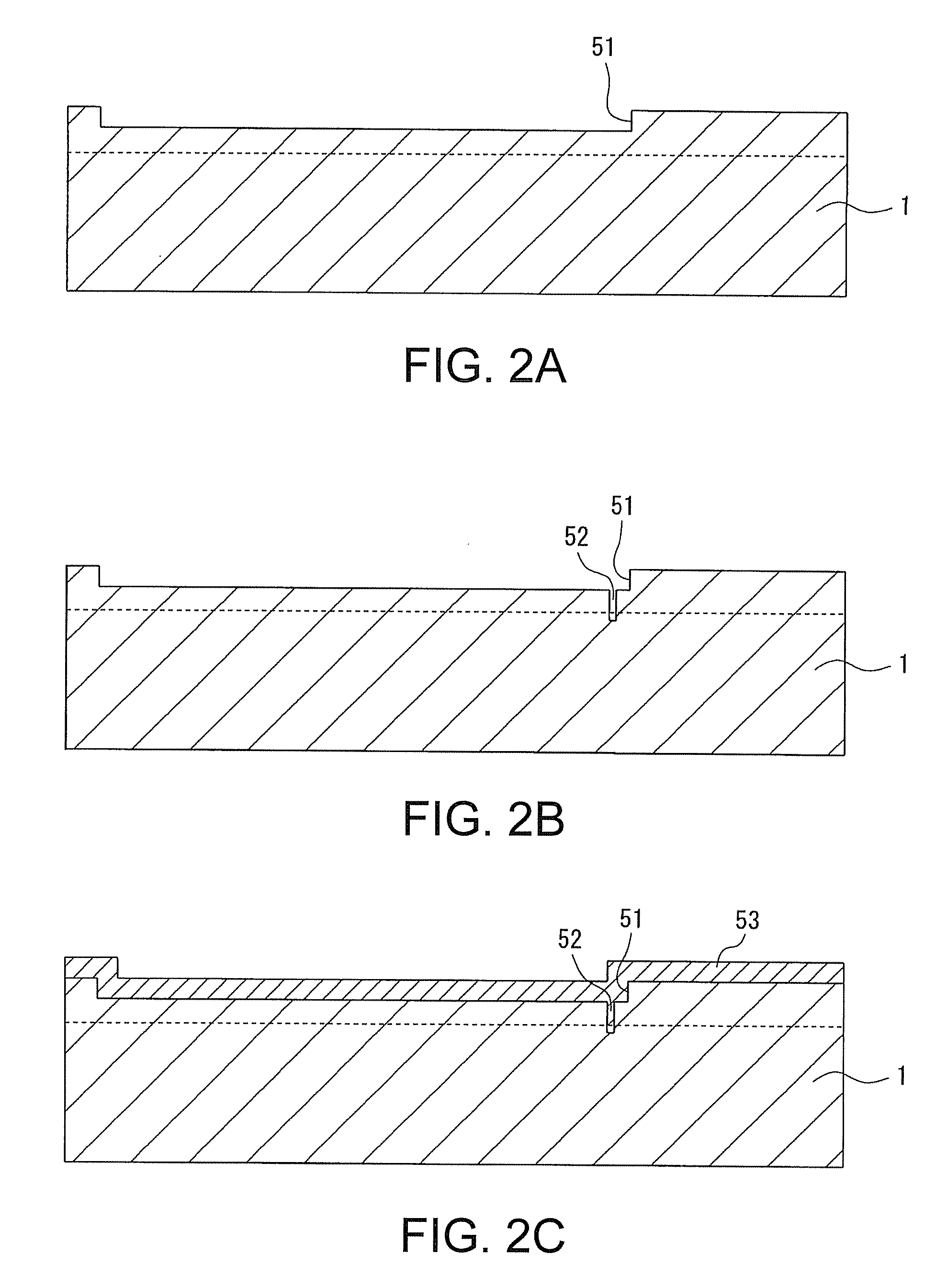

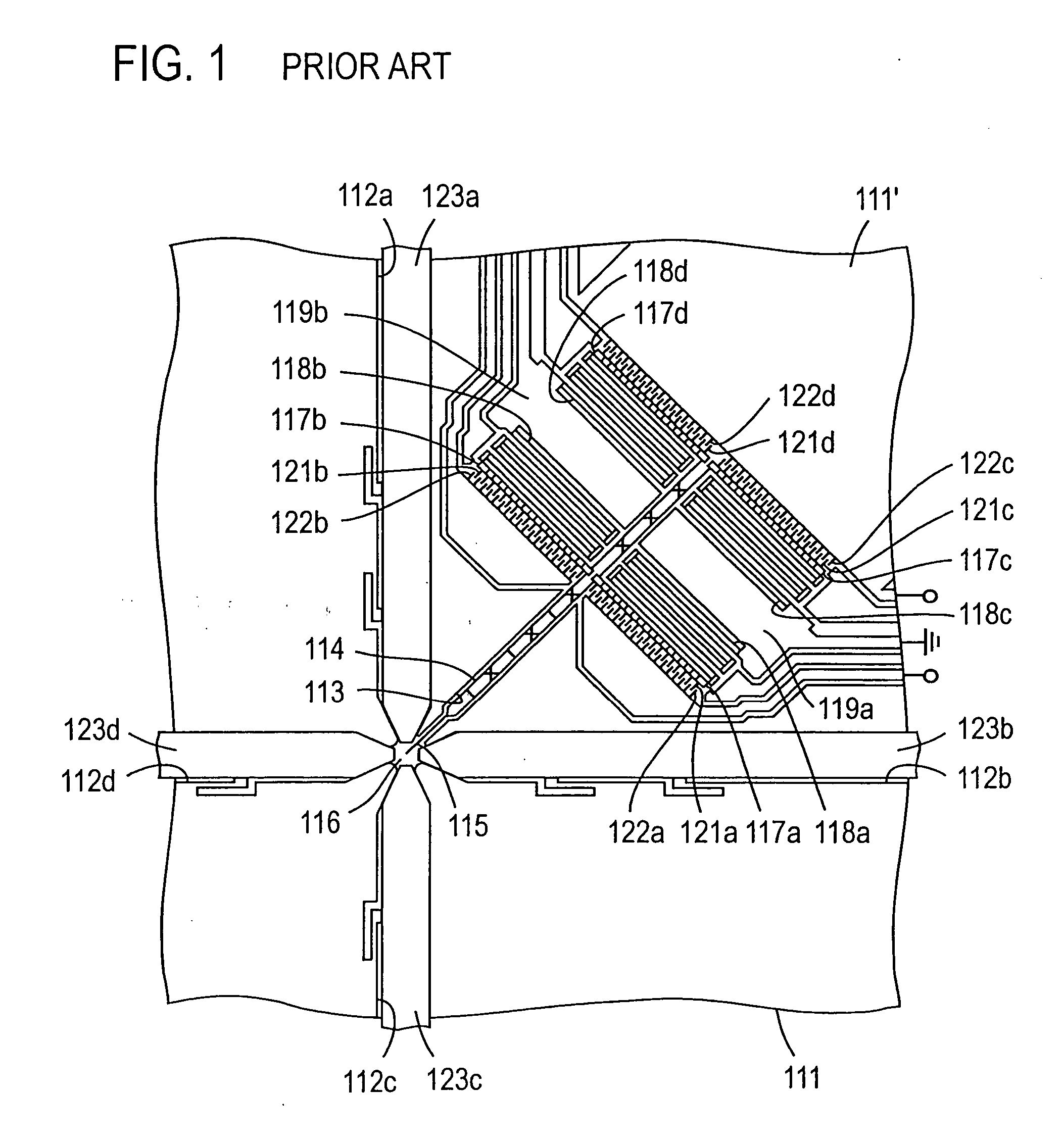

Inkjet recording head, inkjet recording device, and method for manufacturing the inkjet recording head

InactiveUS20090237454A1Avoid cloggingImprove etch selectivityPiezoelectric/electrostrictive device manufacture/assemblyPiezoelectric/electrostrictive transducersPressure generationElectrical and Electronics engineering

In a method for manufacturing an inkjet recording head which includes a pressure generation chamber supplied with ink fluid and a nozzle opening leading to the pressure generation chamber, the method includes: (a) forming a first trench which serves as the pressure generation chamber on a first surface of a first substrate; (b) forming a second trench which serves as the nozzle opening on a bottom surface of the first trench; (c) forming a sacrificial film on the first trench and the second trench; (d) forming a diaphragm on the sacrificial film as well as on the first surface of the first substrate; (e) forming a piezoelectric element on the diaphragm; (f) grinding a second surface of the first substrate so as to open a bottom surface of the second trench; (g) forming an opening which exposes the sacrificial film on the first surface of the first substrate; and (h) removing the sacrificial film through the opening.

Owner:SEIKO EPSON CORP

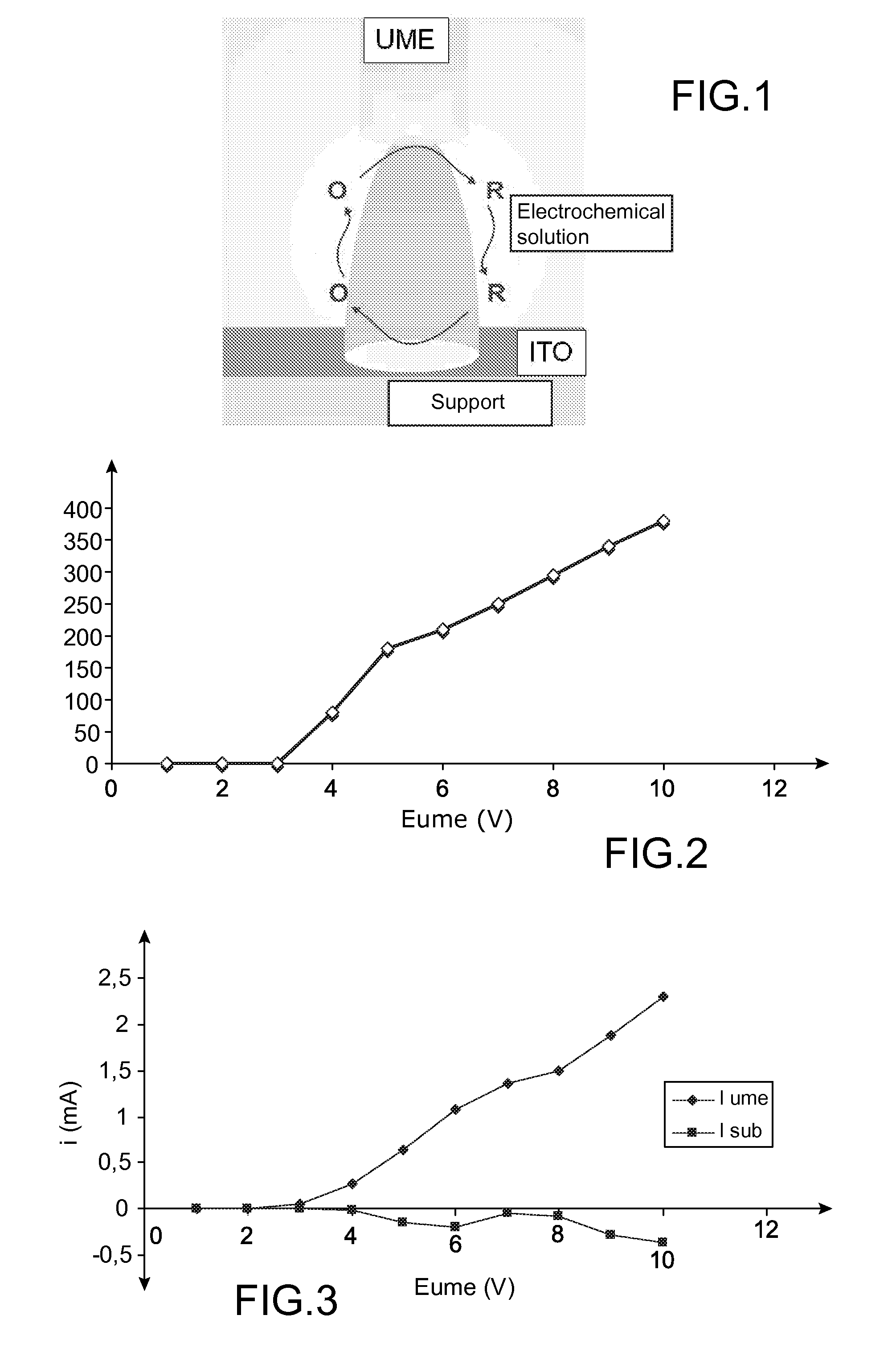

Method for etching conductive metal oxide layer using microelectrode

InactiveUS20130020115A1Fast etchEasy accessElectrolysis componentsSemiconductor/solid-state device manufacturingMicroelectrodeElectrochemistry

A method for etching a selected area of a conductive metal oxide layer deposited on a support is provided. The method comprises removing the area via electrochemical route in the presence of a polarized microelectrode and an electrochemical solution. In addition, an etched layer obtained with the foregoing method is provided.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

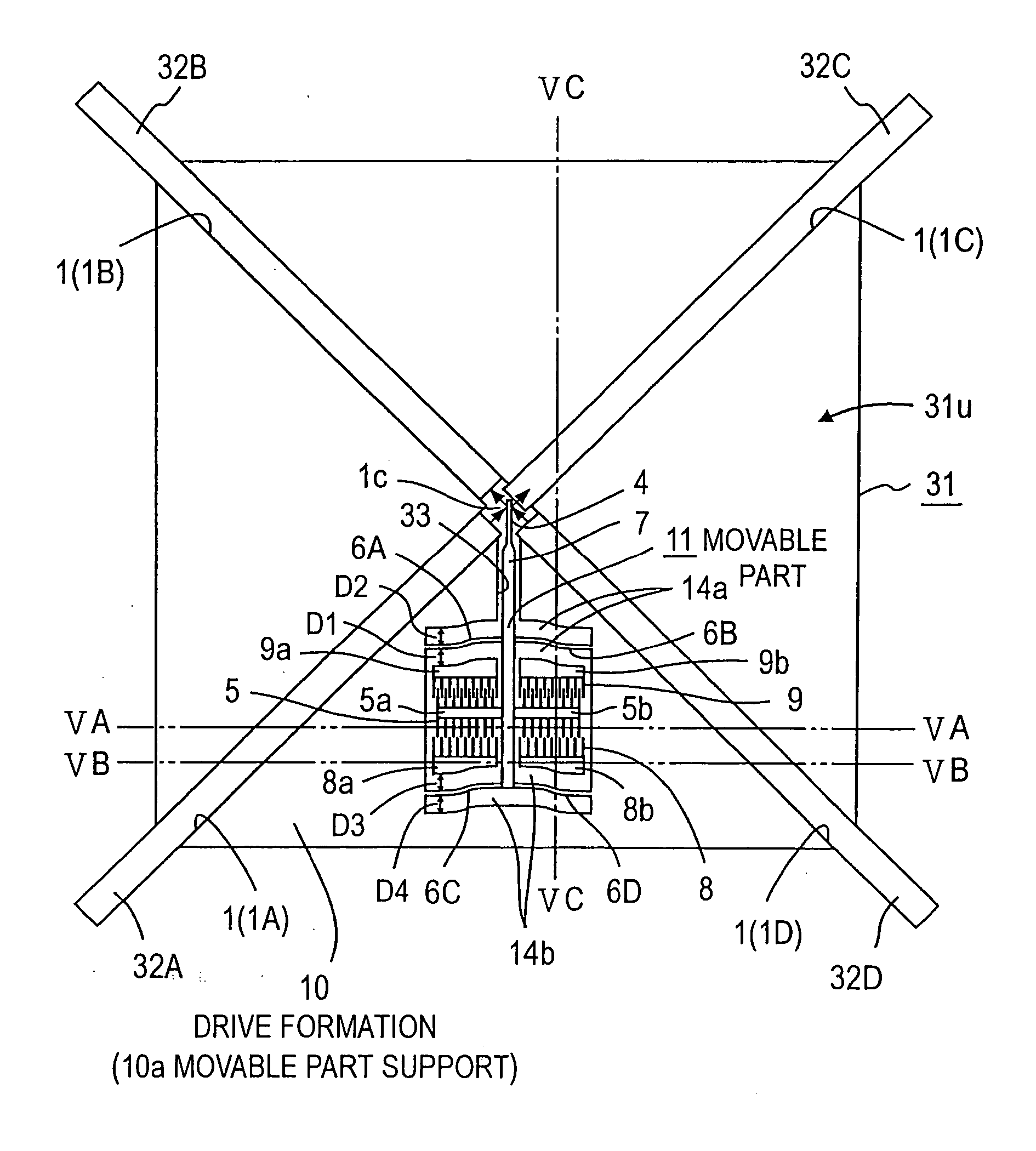

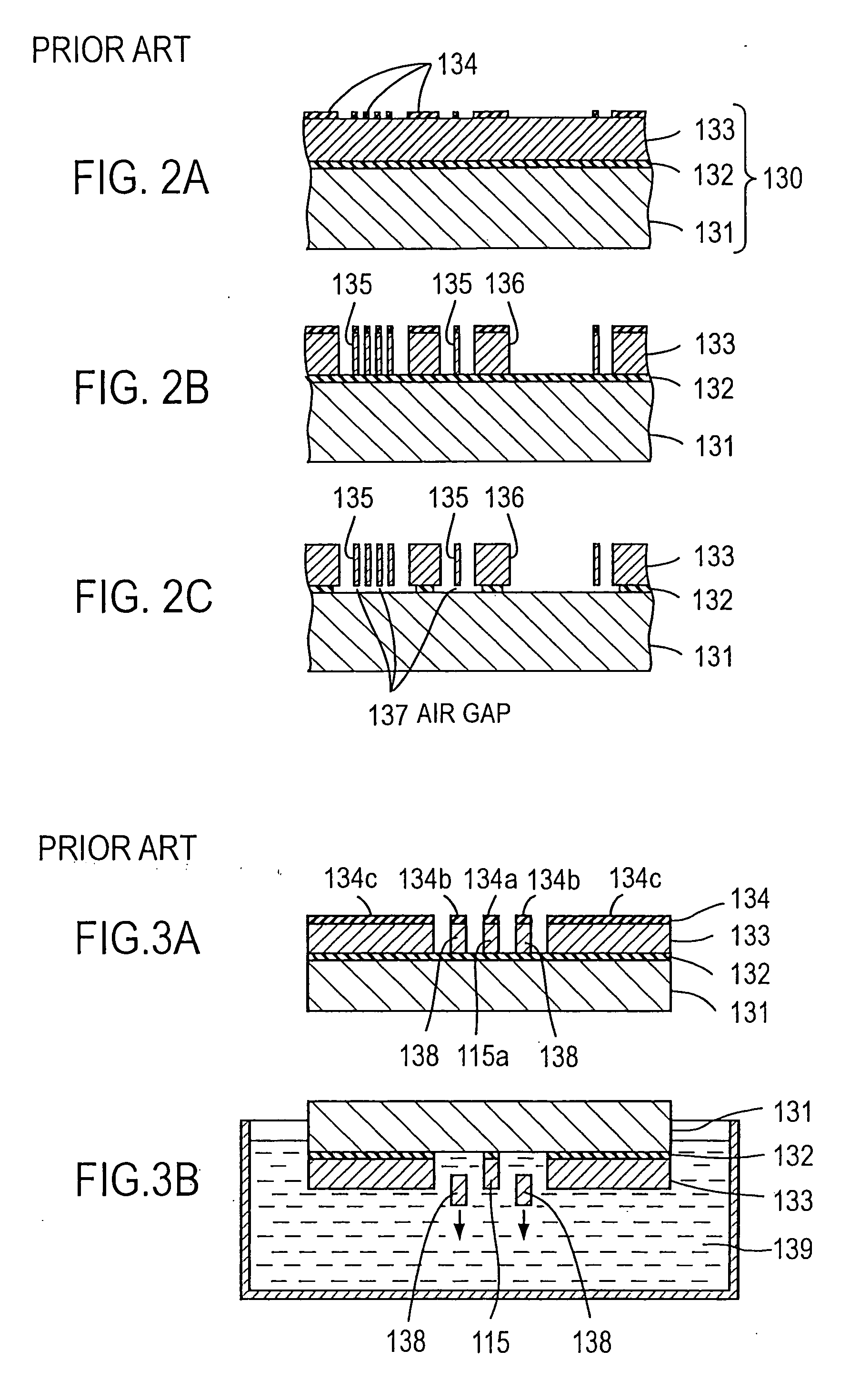

Micro-optic device and method of manufacturing same

InactiveUS20050069246A1Shorten the length of timeHigh yieldDecorative surface effectsCoupling light guidesSilicon dioxideDry etching

A micro-optic device including a complicate structure and a movable mirror is made to be manufactured in a reduced length of time. A silicon substrate and a single crystal silicon device layer with an intermediate layer of silicon dioxide interposed therebetween defines a substrate on which a layer of mask material is formed and is patterned to form a mask having the same pattern as the configuration of the intended optical device as viewed in plan view. A surface which is to be constructed as a mirror surface is chosen to be in a plane of the silicon crystal. Using the mask, the device layer is vertically etched by a reactive ion dry etching until the intermediate layer is exposed. Subsequently, using KOH solution, a wet etching which is anisotropic to the crystallographic orientation is performed with an etching rate which is on the order of 0.1 μm / min for a time interval on the order of ten minutes is performed to convert the sidewall surface of the mirror into a smooth crystallographic surface. Subsequently, the intermediate layer is selectively subject to a wet etching to remove the intermediate layer only in an area located below the movable part of the optical device.

Owner:JAPAN AVIATION ELECTRONICS IND LTD

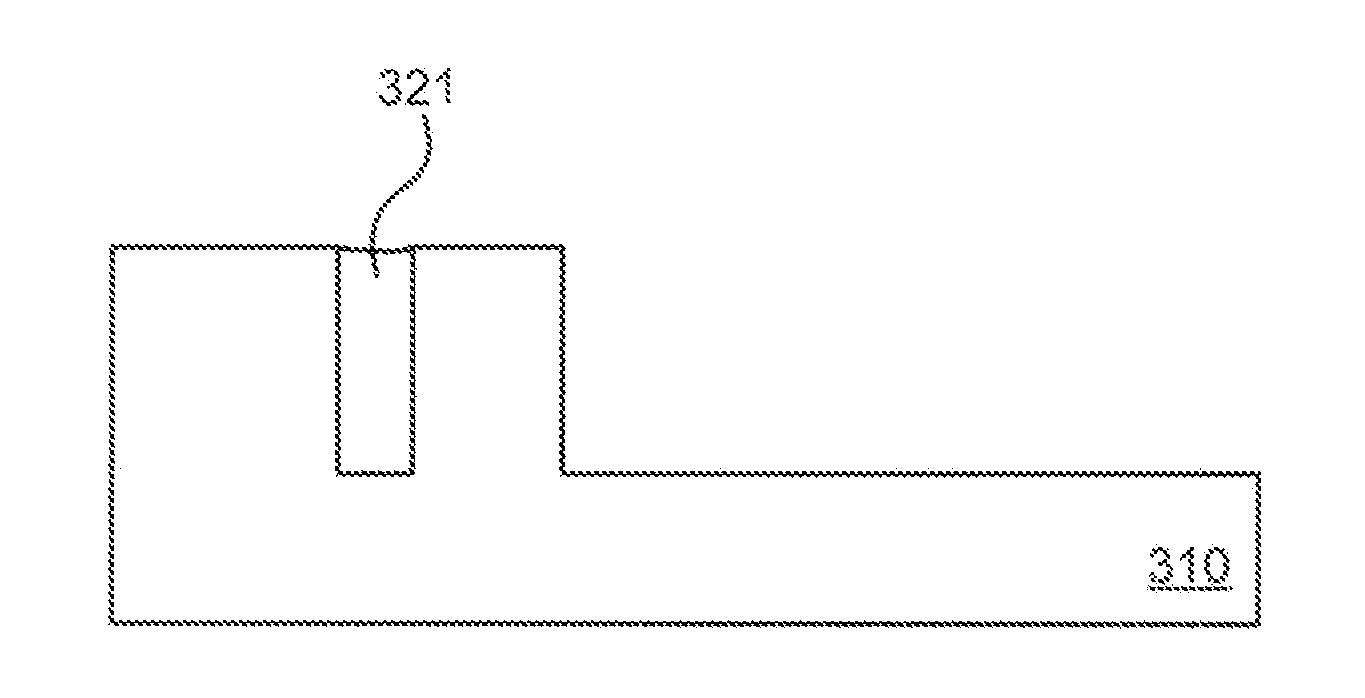

Method for preventing to form a spacer undercut in SEG pre-clean process

ActiveUS20050101093A1Avoid leakage currentFast etchSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringGlycol synthesis

A method for preventing to form a spacer undercut in SEG pre-clean process is provided. This present invention utilizes HFEG solution to etch the first spacer and the second spacer simultaneously, which can prevent from producing a spacer undercut, meanwhile; a native oxide layer upon a surface of a semiconductor substrate is removed. Hence, the clean surface on the semiconductor substrate is obtained. This method includes the steps as follows: Firstly, the native oxide layer upon the surface of the semiconductor substrate is removed by DHF (HF in deionized water) solution. Then, etching the first spacer and the second spacer at the same time by HFEG (HF diluted by ethylene glycol) solution. Also, the native oxide upon the semiconductor substrate is removed. Therefore, it obtains the clean semiconductor surface without a serious spacer undercut.

Owner:MARLIN SEMICON LTD

Semiconductor light emitting element and method for fabricating the same

InactiveUS20050003571A1Fast etchImprove performanceOptical wave guidanceLaser detailsAnisotropic strainActive layer

The semiconductor laser of this invention includes an active layer formed in a c-axis direction, wherein the active layer is made of a hexagonal-system compound semiconductor, and anisotropic strain is generated in a c plane of the active layer.

Owner:PANASONIC CORP

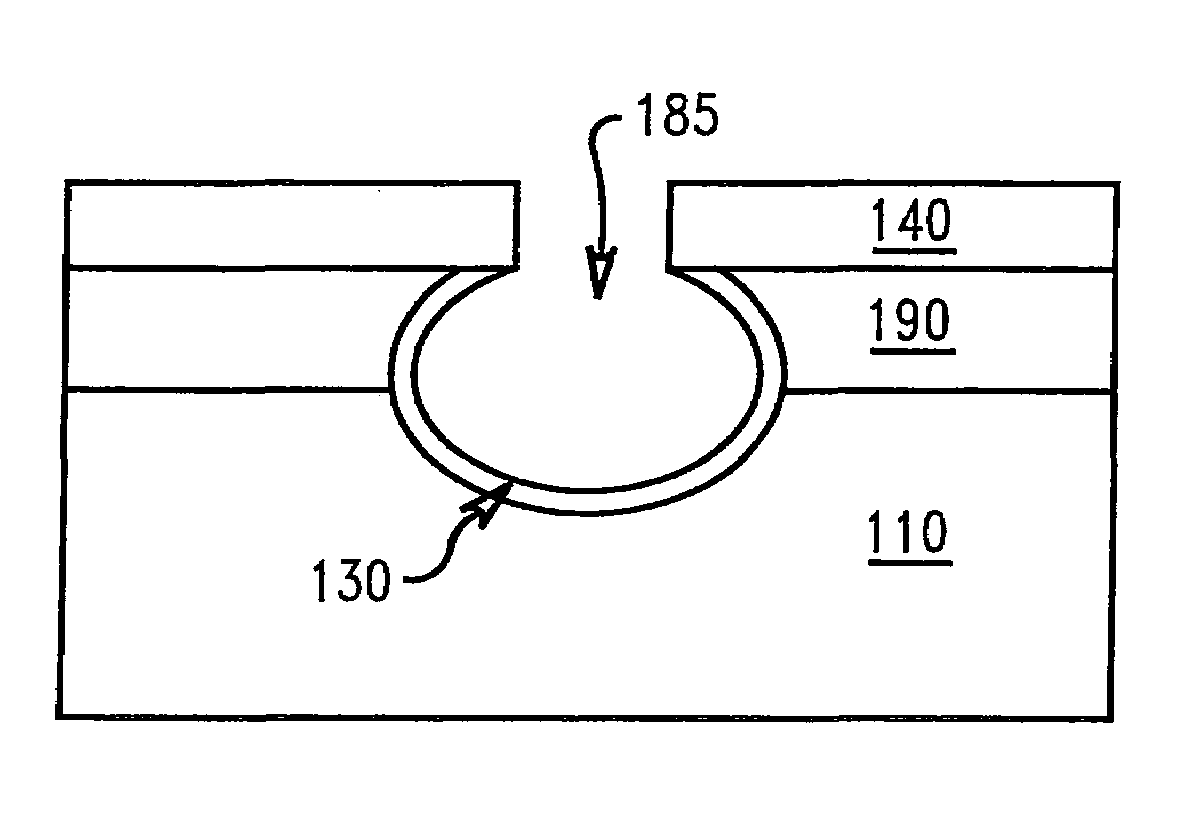

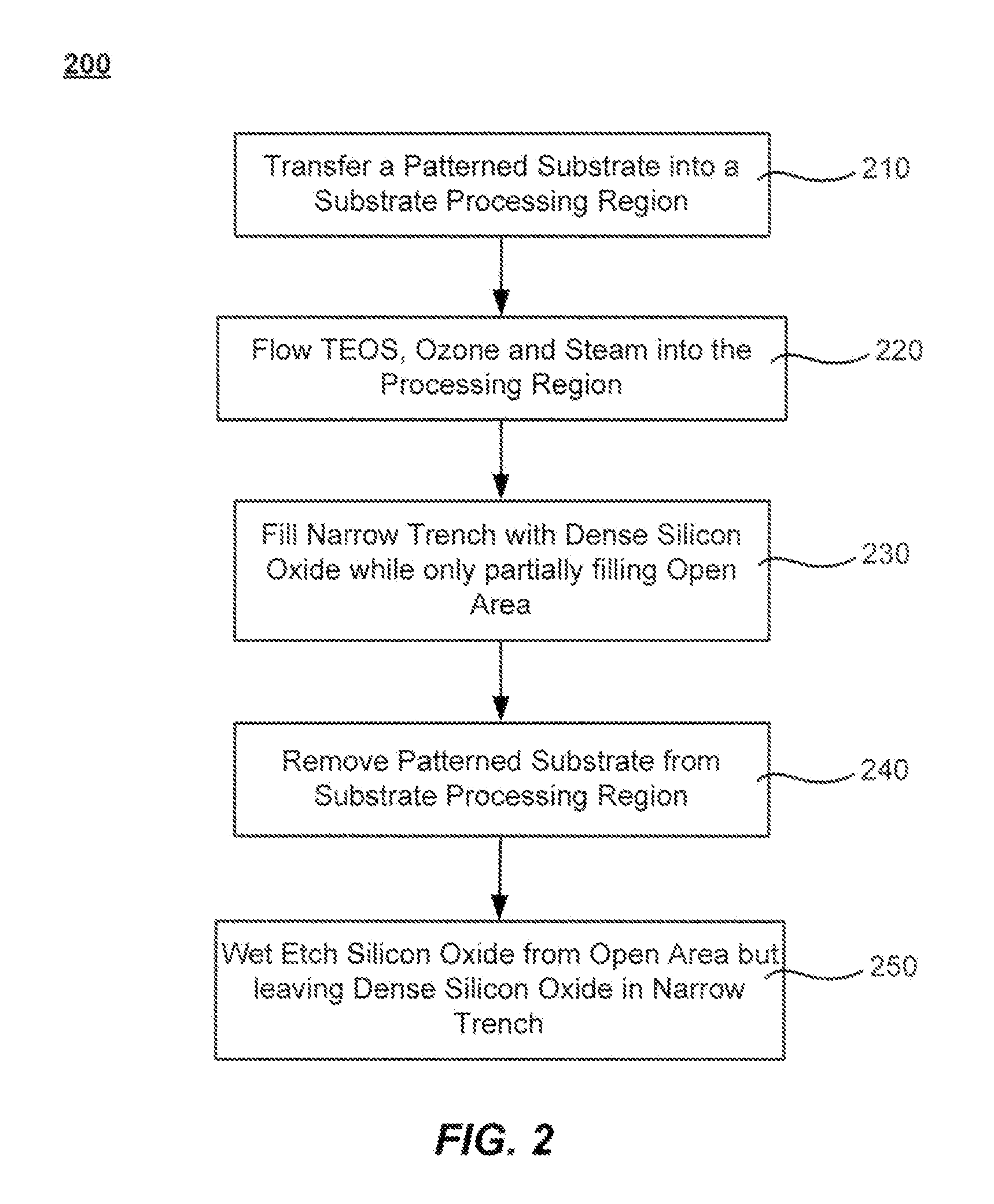

Preferential dielectric gapfill

ActiveUS20110250731A1Fast etchSemiconductor/solid-state device manufacturingSilicon oxideDielectric layer

Aspects of the disclosure pertain to methods of preferentially filling narrow trenches with silicon oxide while not completely filling wider trenches and / or open areas. In embodiments, dielectric layers are deposited by flowing a silicon-containing precursor and ozone into a processing chamber such that a relatively dense first portion of a silicon oxide layer followed by a more porous (and more rapidly etched) second portion of the silicon oxide layer. Narrow trenches are filled with dense material whereas open areas are covered with a layer of dense material and more porous material. Dielectric material in wider trenches may be removed at this point with a wet etch while the dense material in narrow trenches is retained.

Owner:APPLIED MATERIALS INC

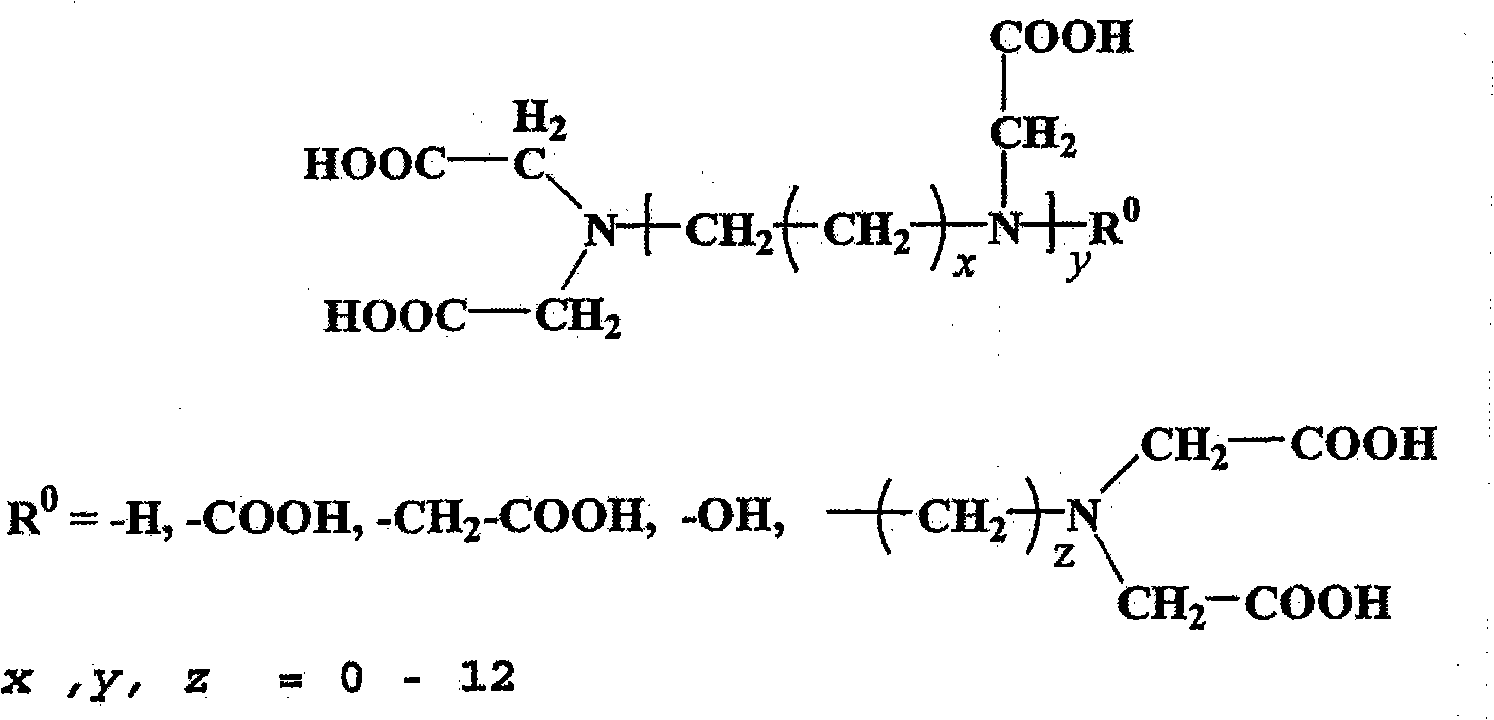

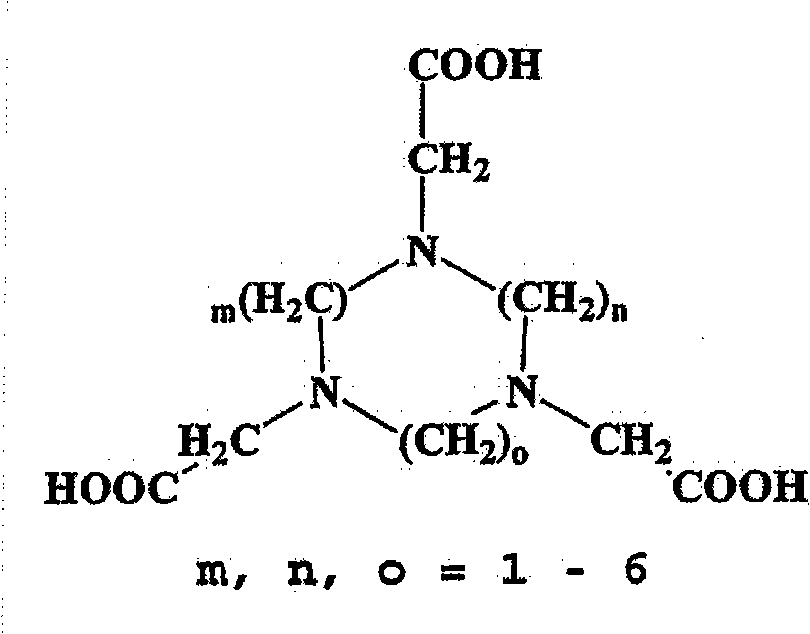

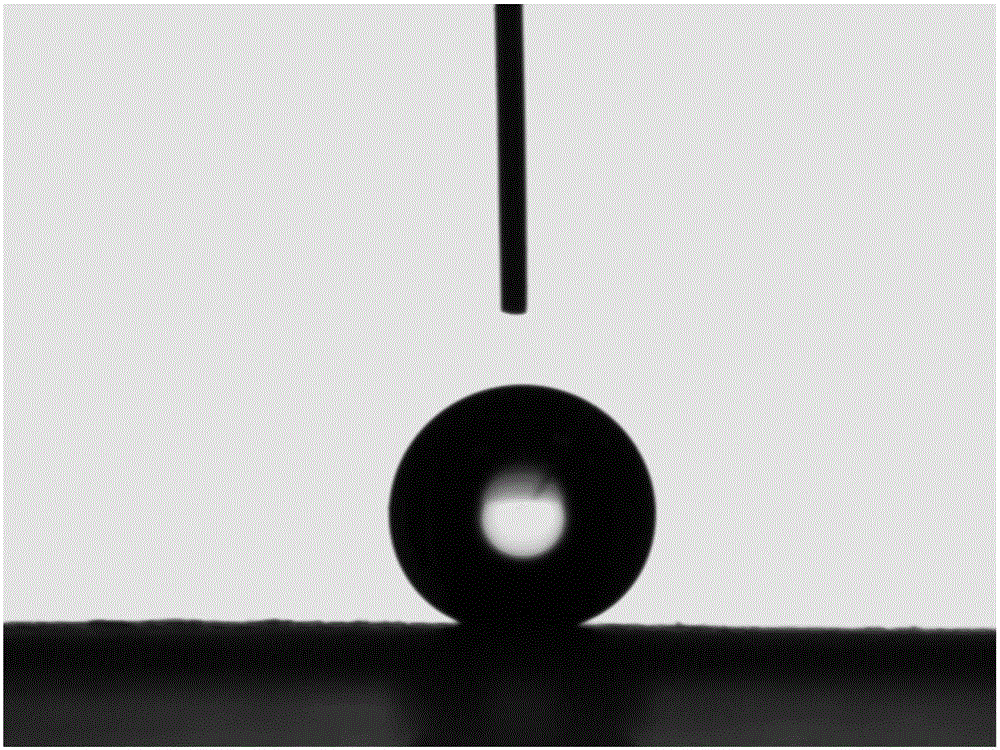

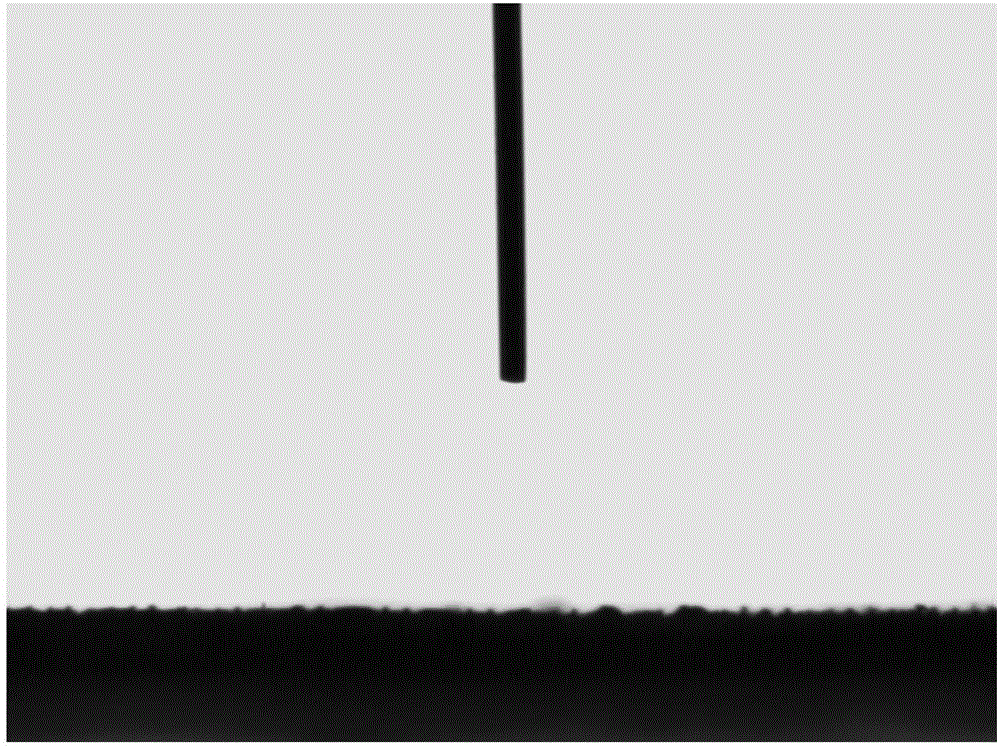

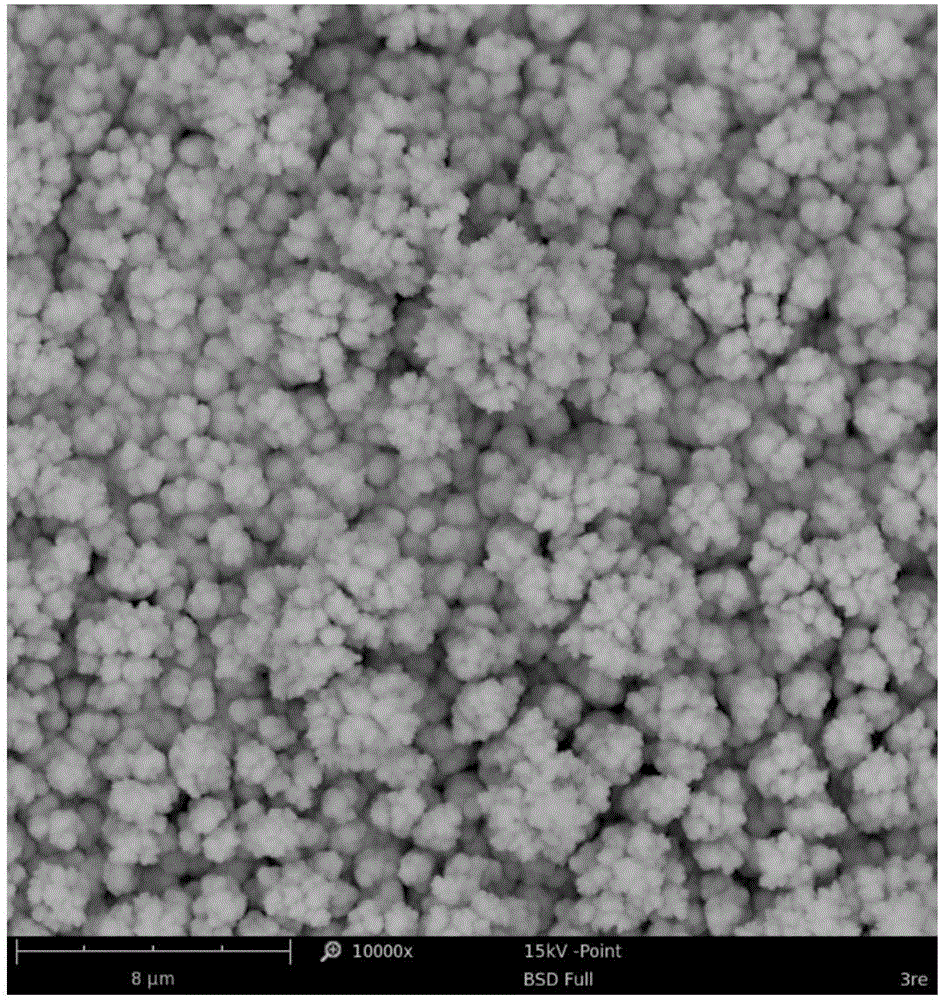

Super-hydrophobic and super-oleophilic copper wire mesh free of low surface energy material modification and preparation method thereof

ActiveCN106823469AFast etchThe process is easy to implementNon-miscible liquid separationCopper wireMetallic materials

The invention belongs to the technical field of metal material surface treatment and discloses a super-hydrophobic and super-oleophilic copper wire mesh free of low surface energy material modification and a preparation method thereof. The preparation method comprises the steps of cleaning and drying the copper wire meshes, and taking two pieces of copper wire meshes as two electrodes of AC separately; carrying out electrodeposition in a deionized water electroplate liquid containing thioacetamide, ethylenediamine tetraacetic acid disodium and copper sulfate pentahydrate; and cleaning the copper meshes subjected to electrodeposition and then carrying out high-temperature drying at 80-200 DEG C to obtain the super-hydrophobic and super-oleophilic copper wire mesh. The two electrodes of the AC can be quickly etched at the same time, and the super-hydrophobic and super-oleophilic copper wire mesh is suitable for large-area production, special equipment does not need to be used, and the treatment process is easy to implement; and the related solution formula does not contain a toxic fluorine-containing or carbon-containing low surface energy material, is free of harm to the environment and a human body, and has good economical and environmental benefits.

Owner:SOUTH CHINA UNIV OF TECH

Chemical method for etching insulating-film for flexible printed circuit, and etching solution

An etching liquid for preparing the insulating film of flexible PCB is prepared from the solution of potassium (or sodium or lithium) hydroxide (5-40%), C2-C6 unitary (or binary or ternery) alcohol or C2-C6 alcoholamine (or dialcoholamine) (10-70%), potassium (or sodium or lithium) carbonate (0-1.5%) and water (25-60%). Its chemical etching process is also disclosed.

Owner:AKM ELECTRONICS INDAL PANYU

Plasma etching process

A method and system are provided for etching a layer to be etched in a plasma etching reactor, including: forming a reactive layer by injection of at least one reactive gas to form a reactive gas plasma, which forms, together with the layer to be etched, a reactive layer which goes into the layer to be etched during etching of said layer to be etched, wherein the reactive layer reaches a steady state thickness upon completion of a determined duration of said injection; said injection being interrupted before said determined duration has elapsed so that, upon completion of the forming of the reactive layer, the thickness of the reactive layer is smaller than said steady state thickness; and removing the reactive layer by injection of at least one inert gas to form an inert gas plasma, which makes it possible to remove only the reactive layer.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES +1

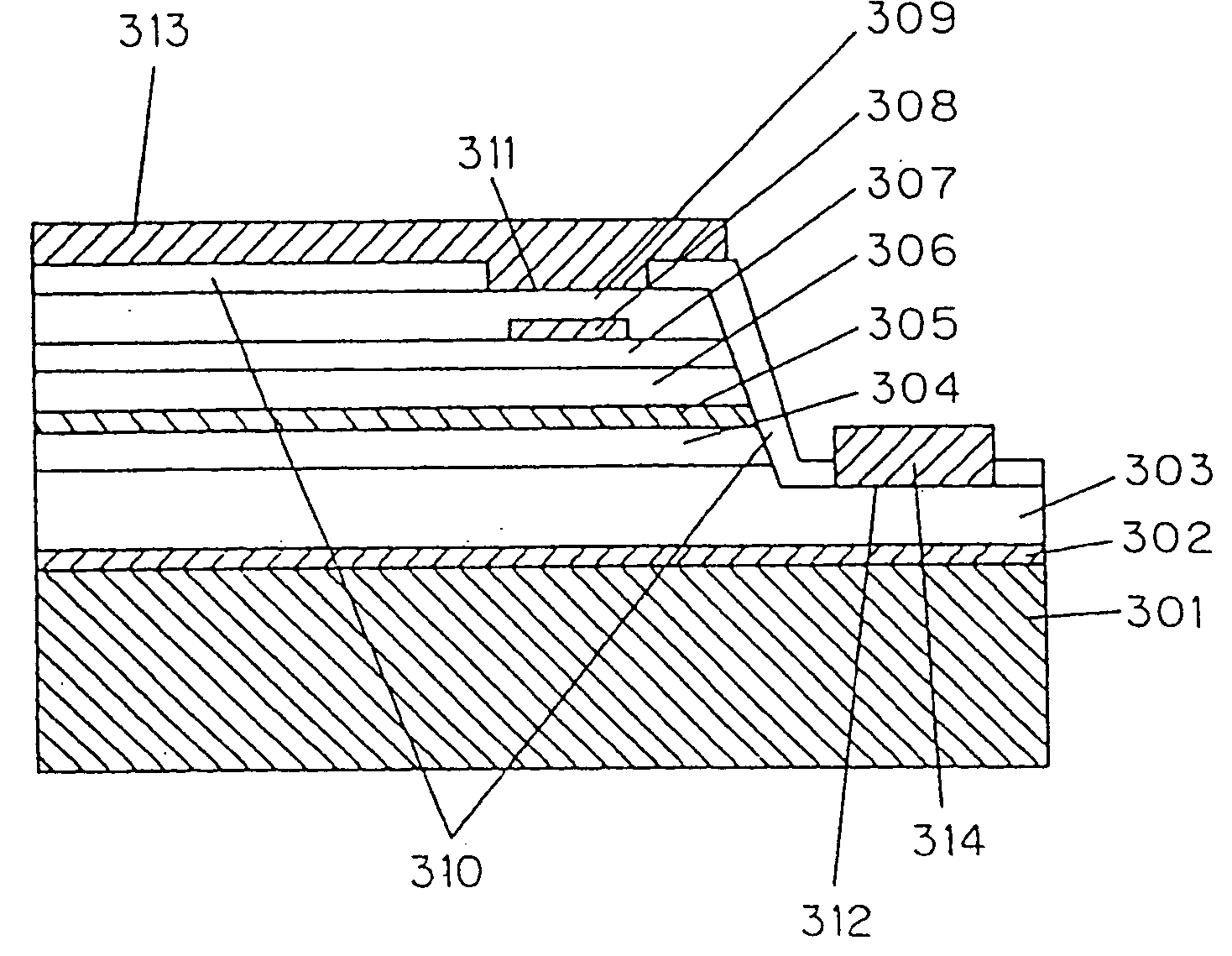

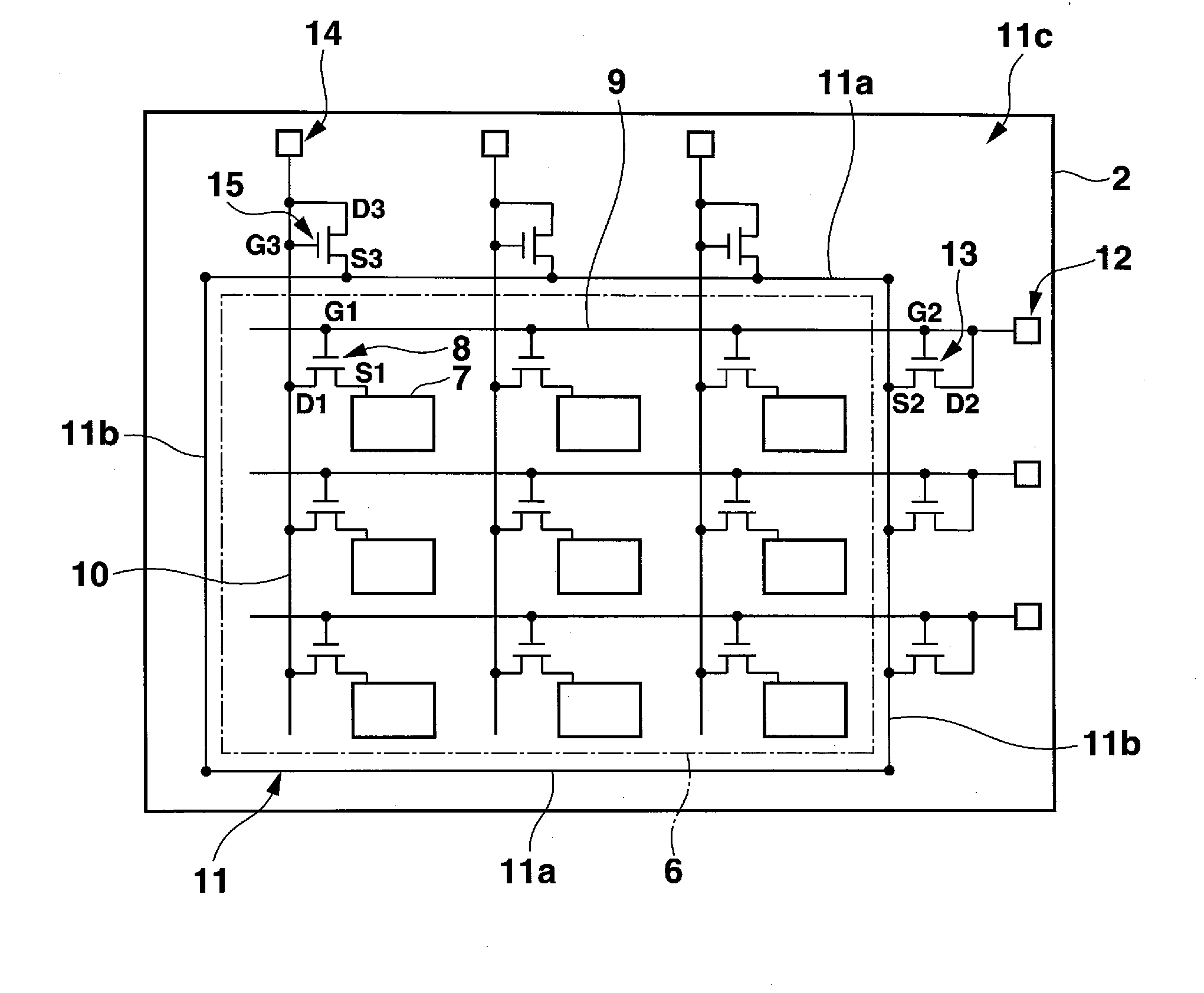

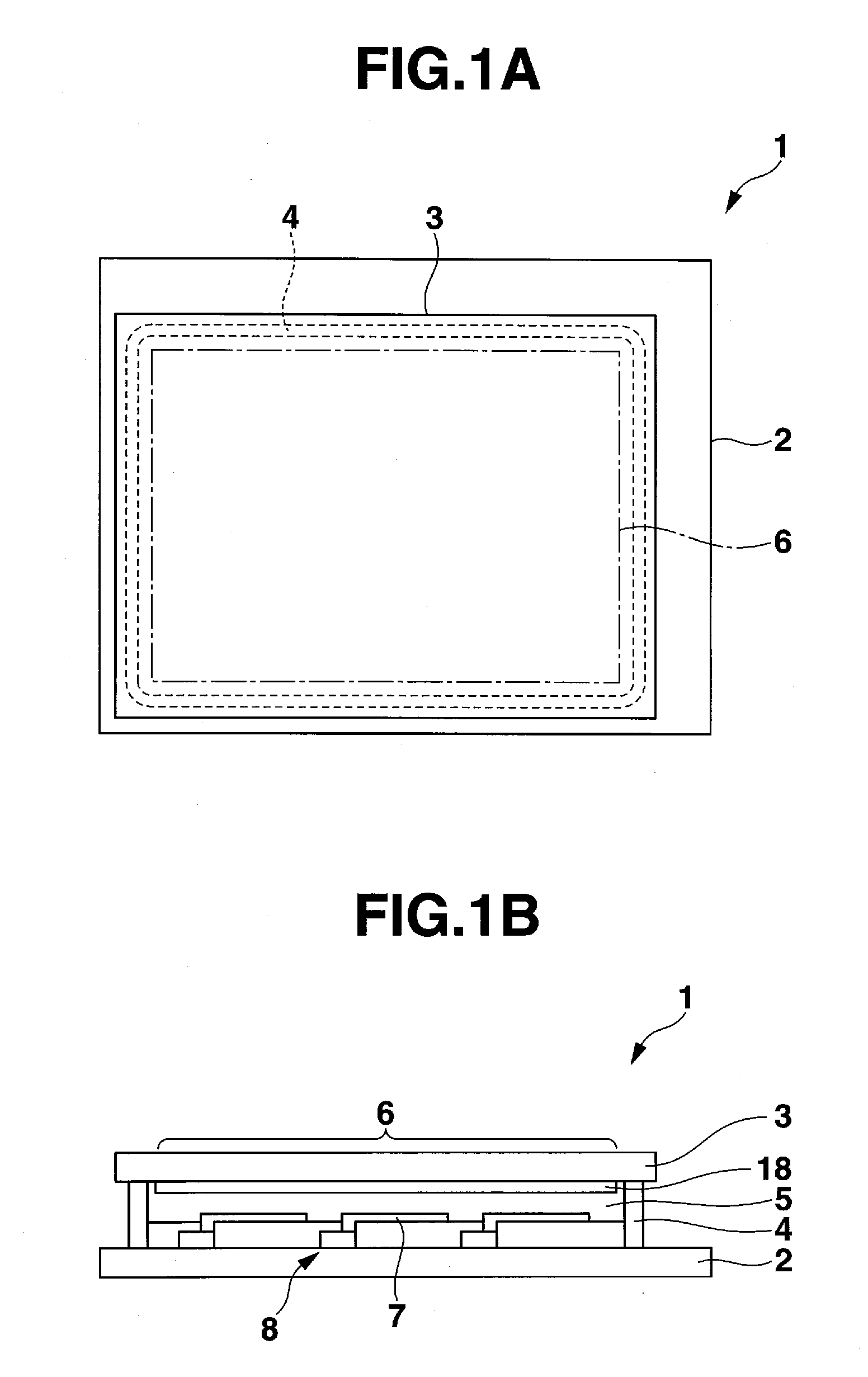

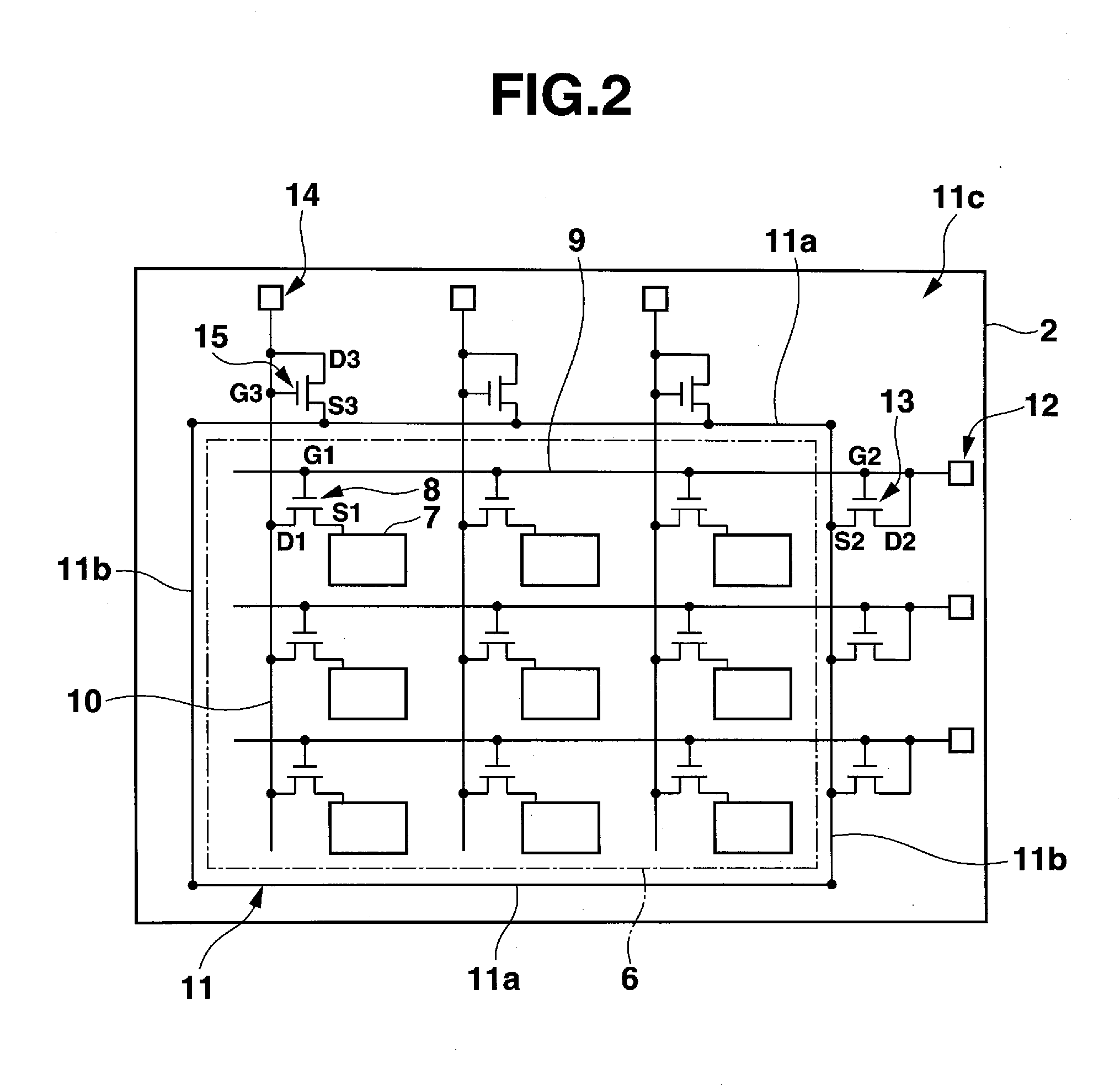

Method for forming multilayer structure, method for manufacturing display panel, and display panel

ActiveUS20100188592A1Fast etchAvoid shapeSolid-state devicesSemiconductor/solid-state device manufacturingMaterials science

A method for forming a multilayer includes a process for forming a first conductive layer on a substrate; a process for forming a first insulating layer on the first conductive layer; a process for forming a second conductive layer on the first insulating layer and patterning the deposited second conductive layer; a process for forming a second insulating layer over the substrate so as to cover the patterned the second conductive layer; a process for forming a third insulating layer on the second insulating layer, wherein an etching speed of the third insulating layer is faster than that of the second insulating layer; and a process for forming contact holes at once that expose at least a part of the first conductive layer to the first insulating layer, the second insulating layer and the third insulating layer.

Owner:ORTUS TECH

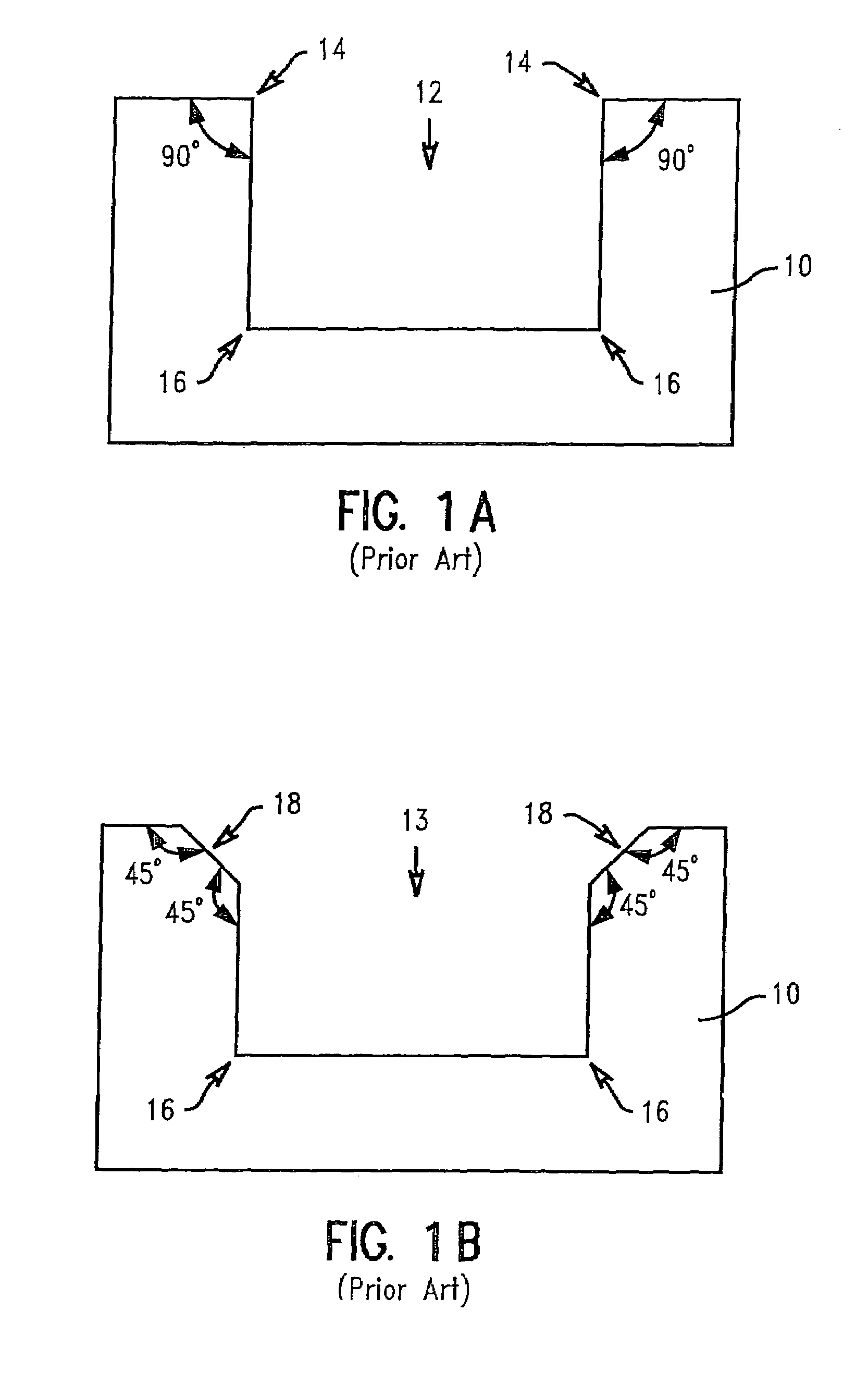

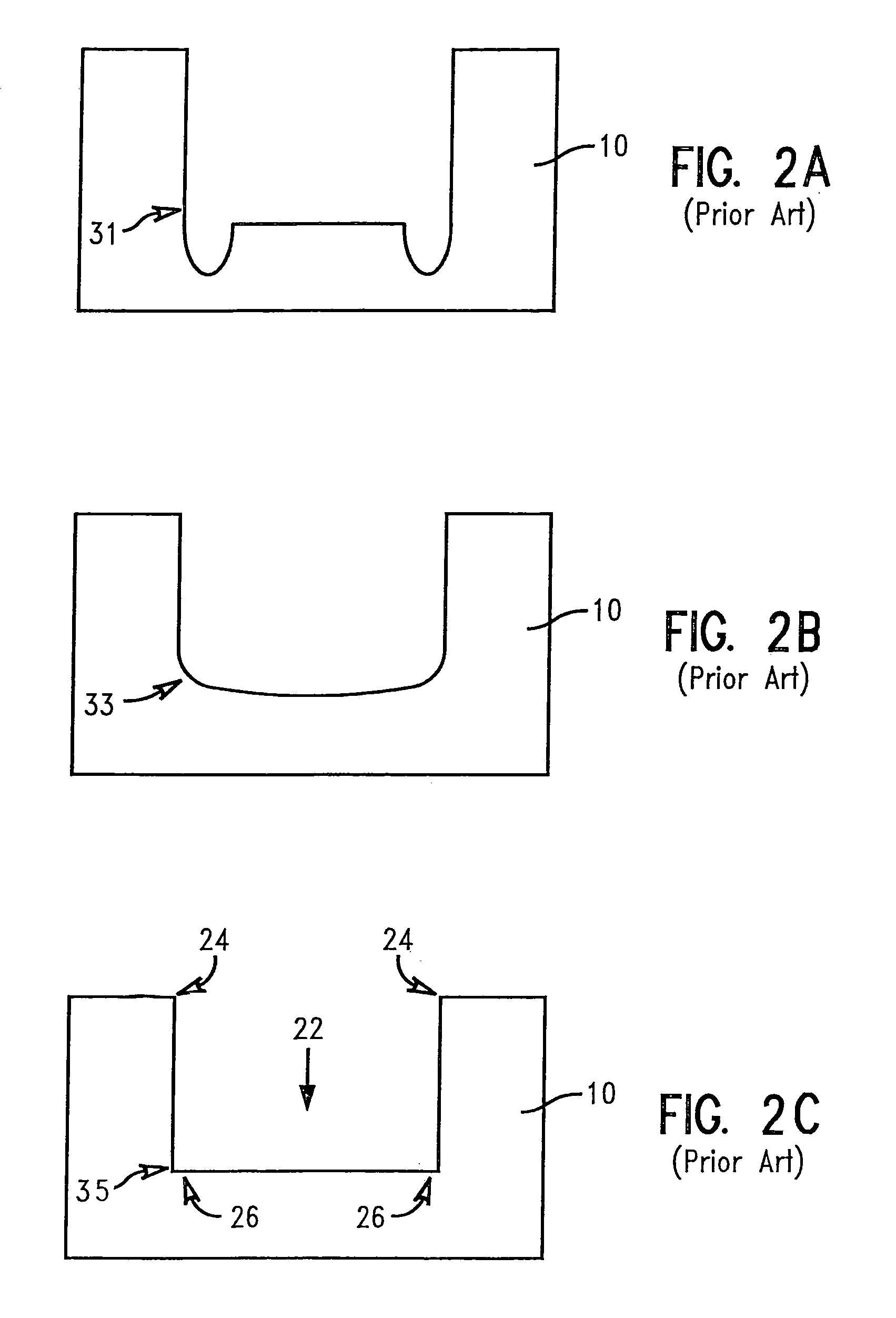

Planar trenches

InactiveUS6063693AEliminate the problemHigh mechanical stressSemiconductor/solid-state device manufacturingSemiconductor materialsNitrate

Method for improving the topography over trench structures in which the provision of extra poly-semiconductor material e.g. polysilicon or nitrate or oxide in the regions of the trench edges and, if necessary, the subsequent oxidation of the extra material prevents the occurrence of regions of high mechanical stress.

Owner:INFINEON TECH AG

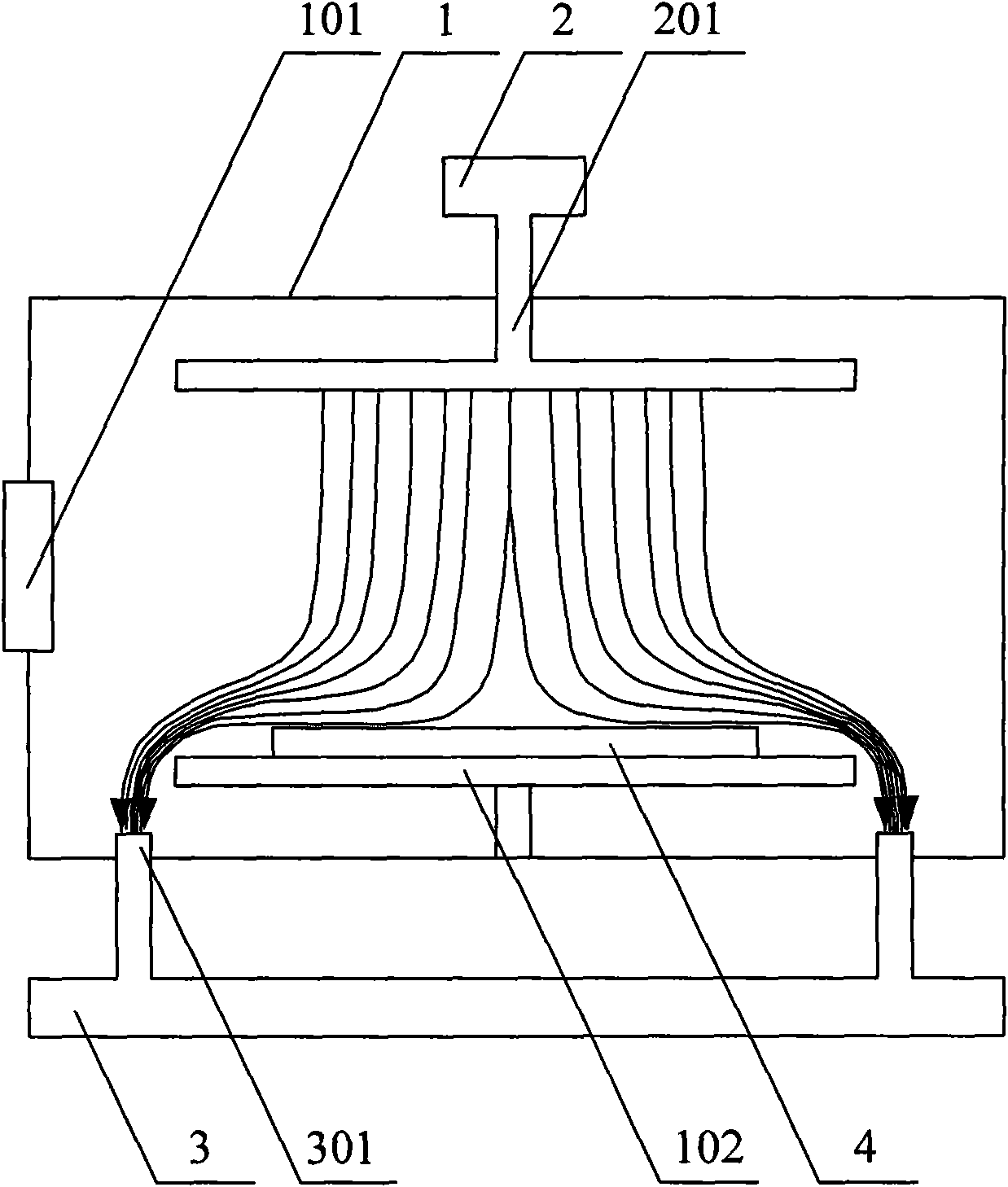

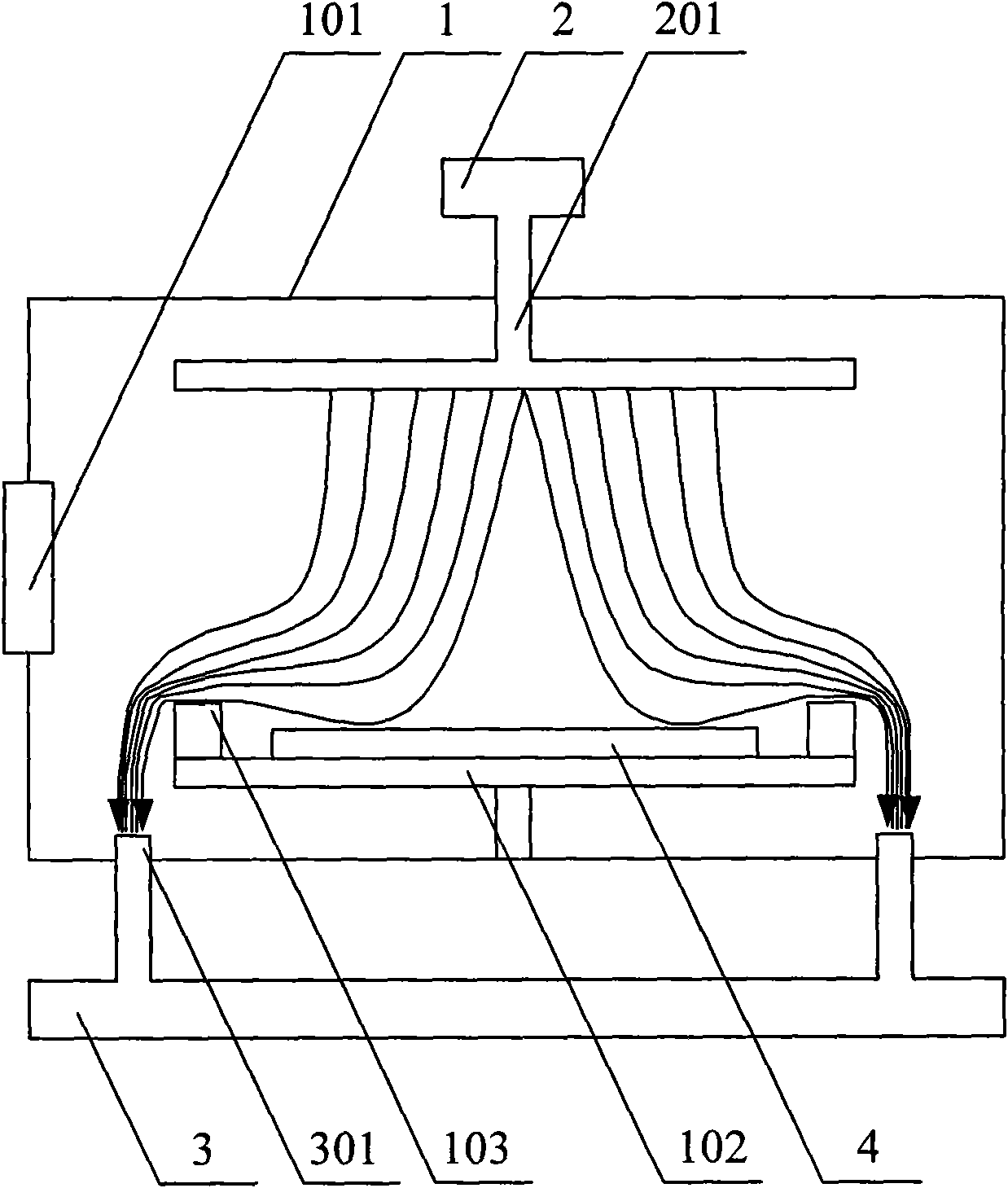

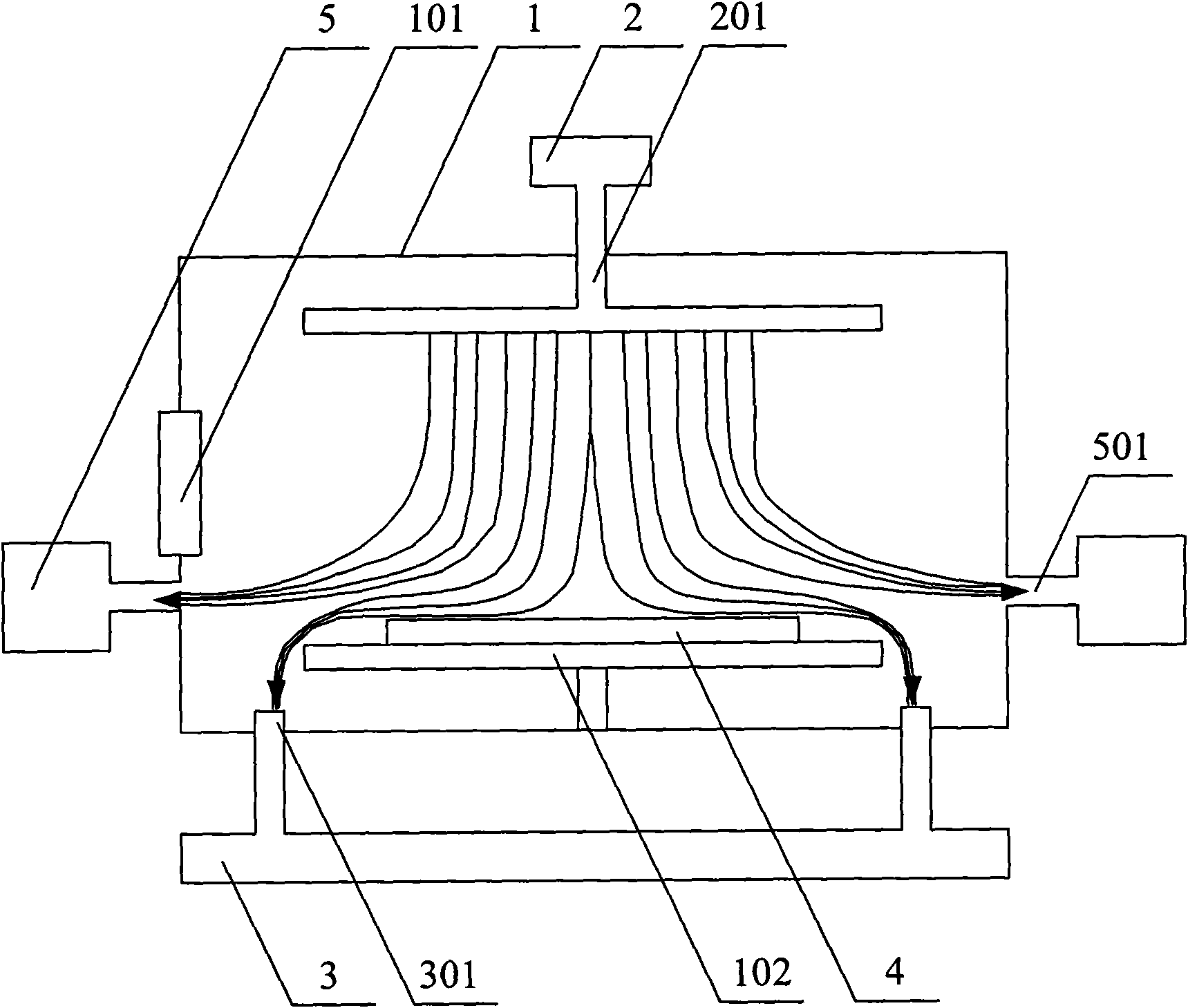

Device for dry etching

ActiveCN101656192AFast etchControl contact densitySemiconductor/solid-state device manufacturingProduct gasContact density

The invention relates to a device for dry etching, which comprises a cavity, a base platform erected at the bottom of the cavity, a gas intake device and a gas extractor. The device also comprises atleast one assistant gas extracting device which is arranged on the lateral surface of the cavity and is used for controlling the contact density of an etching gas and a substrate by pumping the etching gas in the cavity out from the upper part of the base platform. When the device for the dry etching etches the materials of a-Si, SiNx or Mo and the like, the assistant gas extracting device is turned off; when the device etches the materials of Al and the like which are sensitive to the etching gas, the assistant gas extracting device is turned on; besides, the device controls the contact density of the etching gas and the substrate by pumping the etching gas in the cavity out from the upper part of the base platform, thus a gas adjusting seat is not needed to be assembled or disassembled when one device for the dry etching is used for etching various materials, and the production efficiency and the production speed are effectively improved.

Owner:K TRONICS (SUZHOU) TECH CO LTD +1

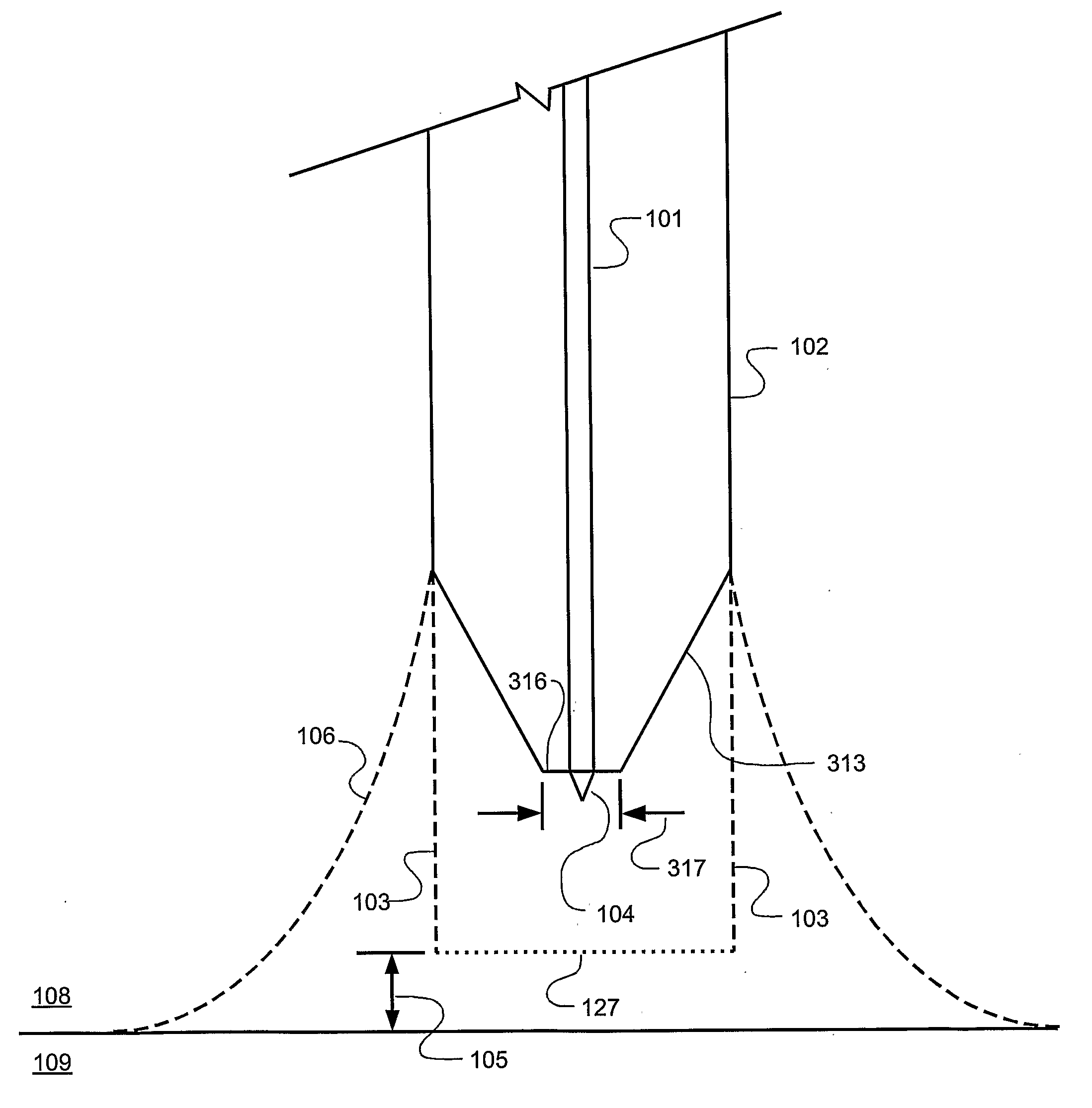

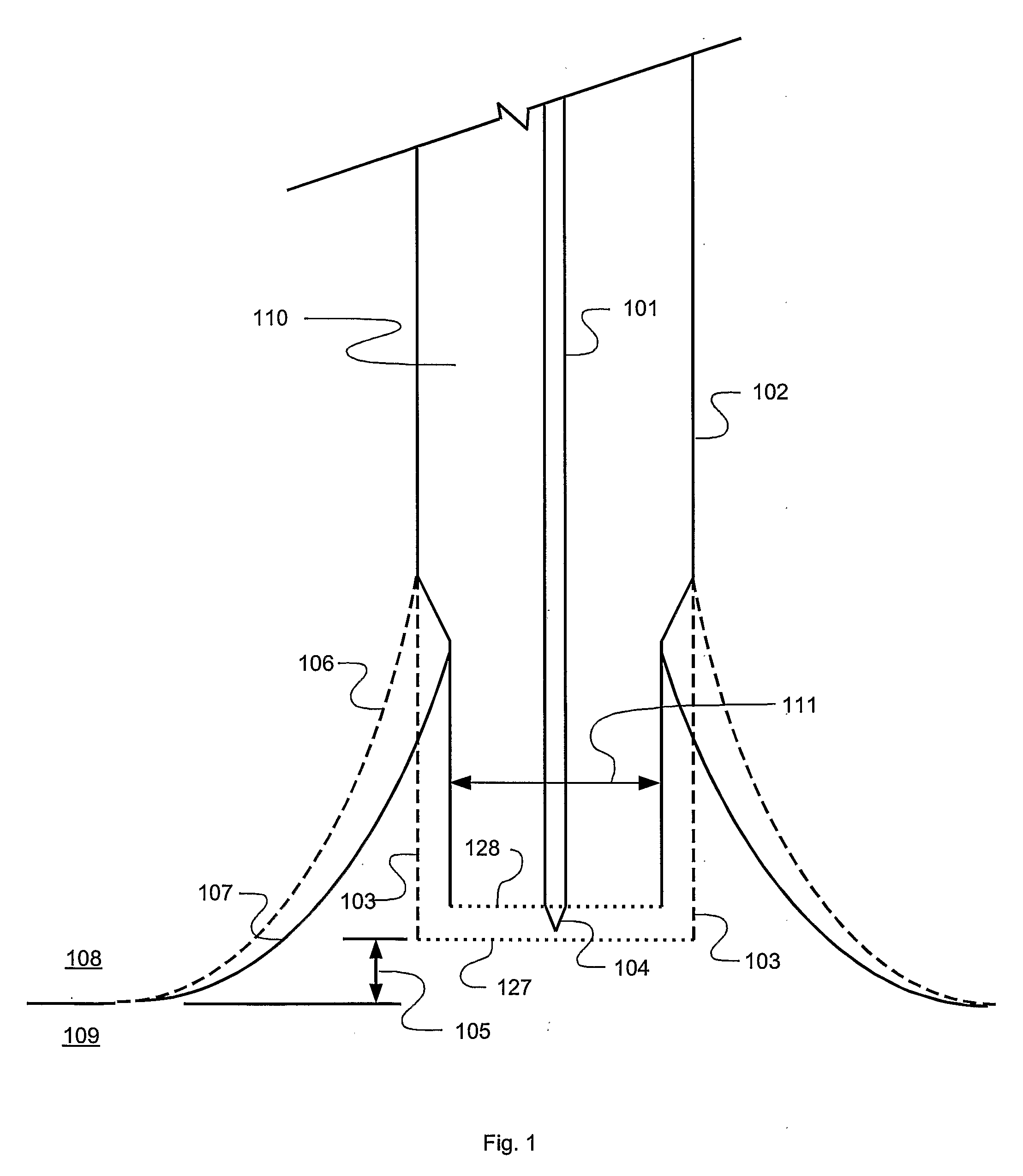

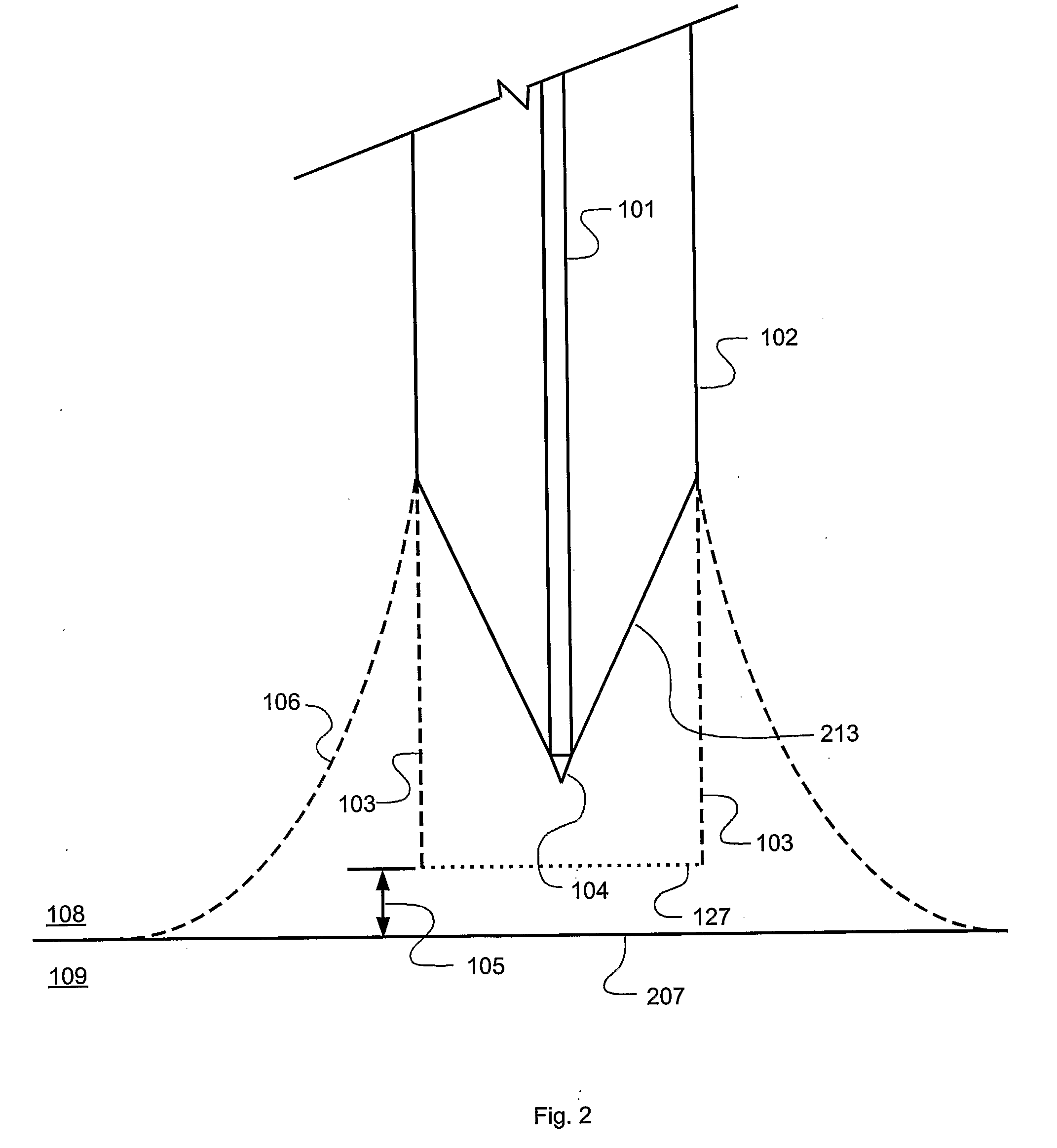

Optical fiber probe tips and methods for fabricating same

InactiveUS20090022456A1Unique optical transmission propertyGood polarization maintenanceOptical fibre with graded refractive index core/claddingDecorative surface effectsOptical fiber probePhysics

Optical fiber probe tips and methods for fabricating the same are presented. One method entails immersing a distal end of an optical fiber having a cladding and a core into an etching solution and simultaneously etching the cladding and the core using the etching solution for tapering the cladding and the core to form a tapered cladding and a tapered core tip. The optical fiber probe tips are suitable for near-field, scanning, optical microscopy (NSOM).

Owner:UNIV OF MARYLAND

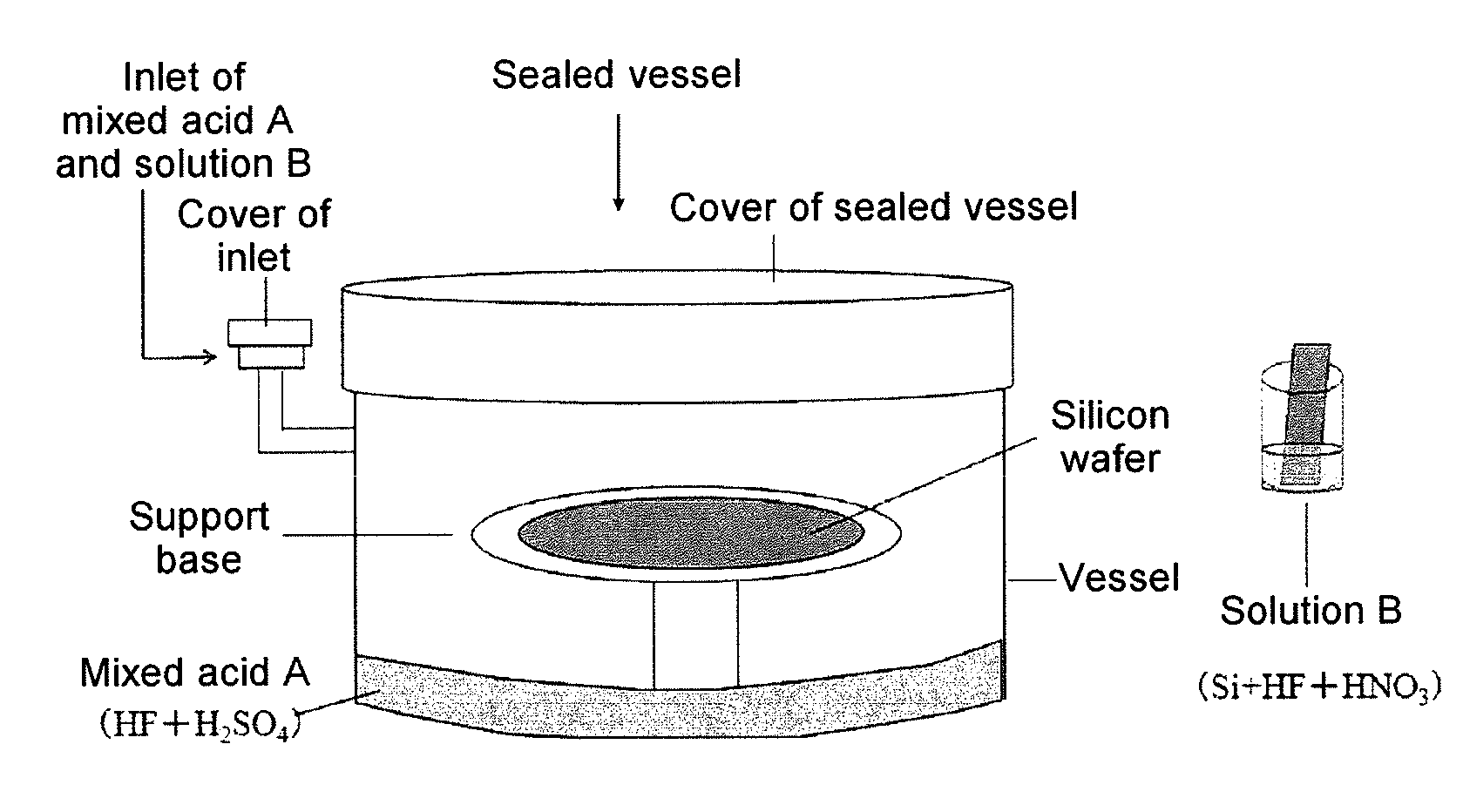

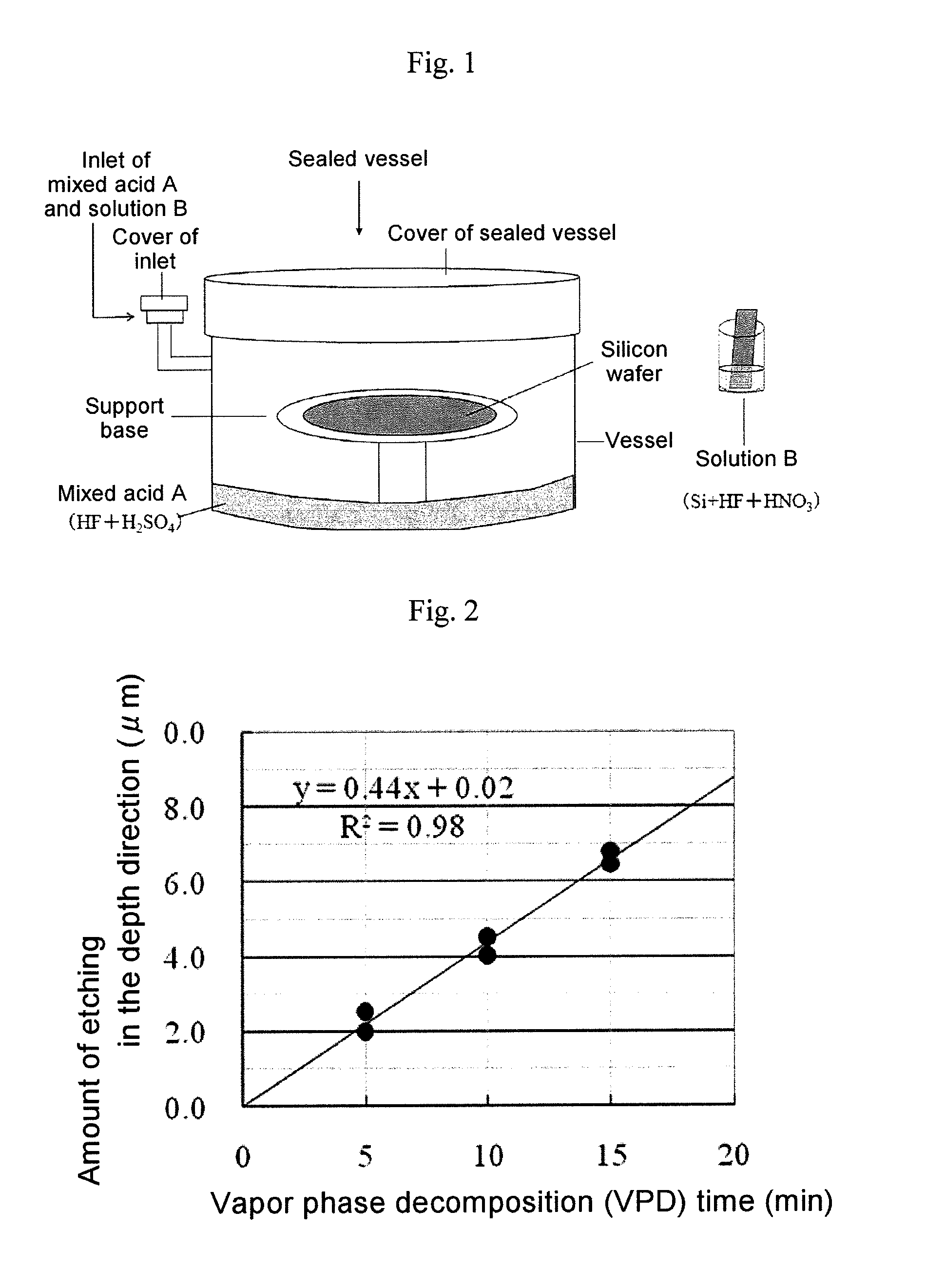

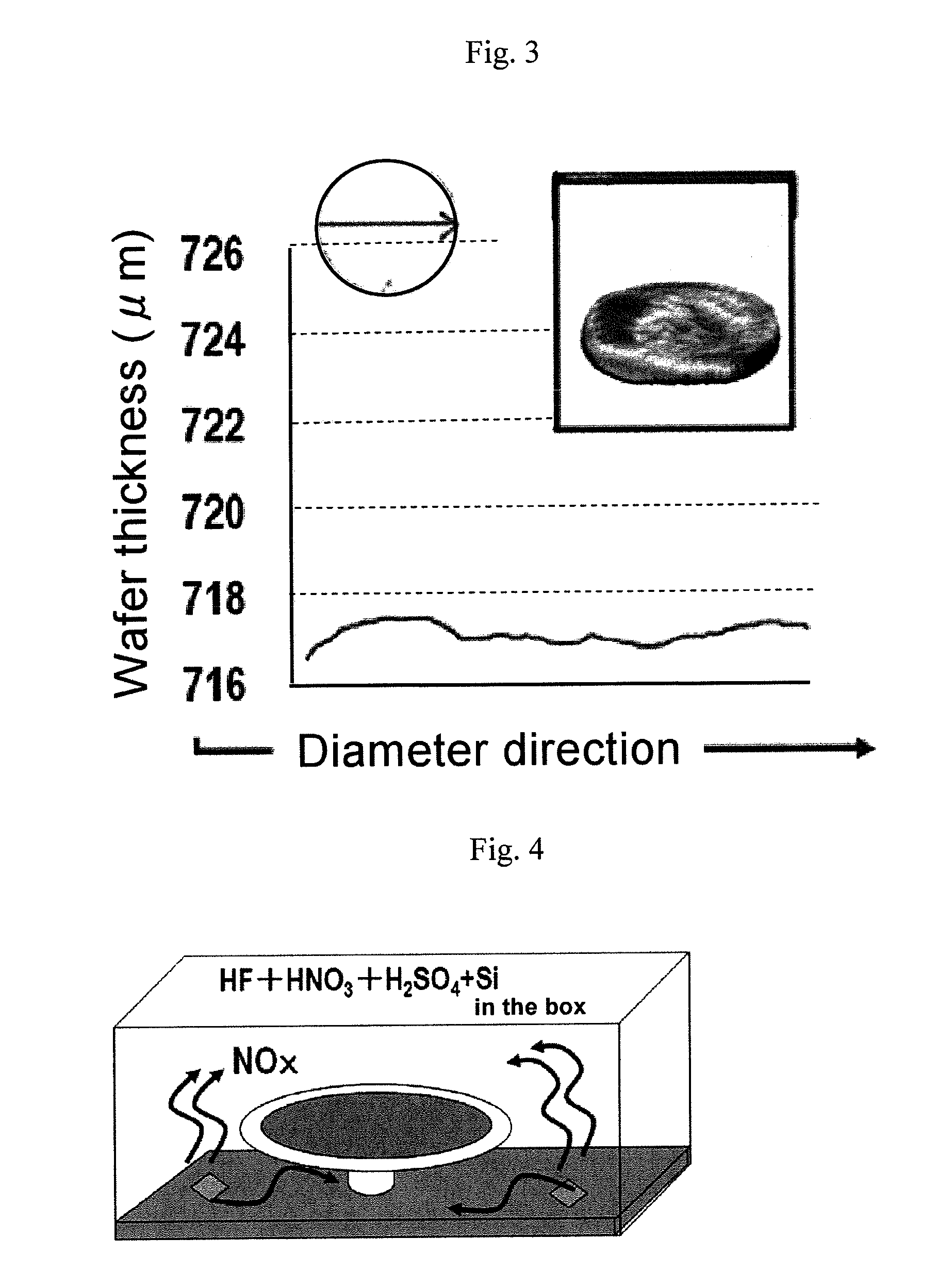

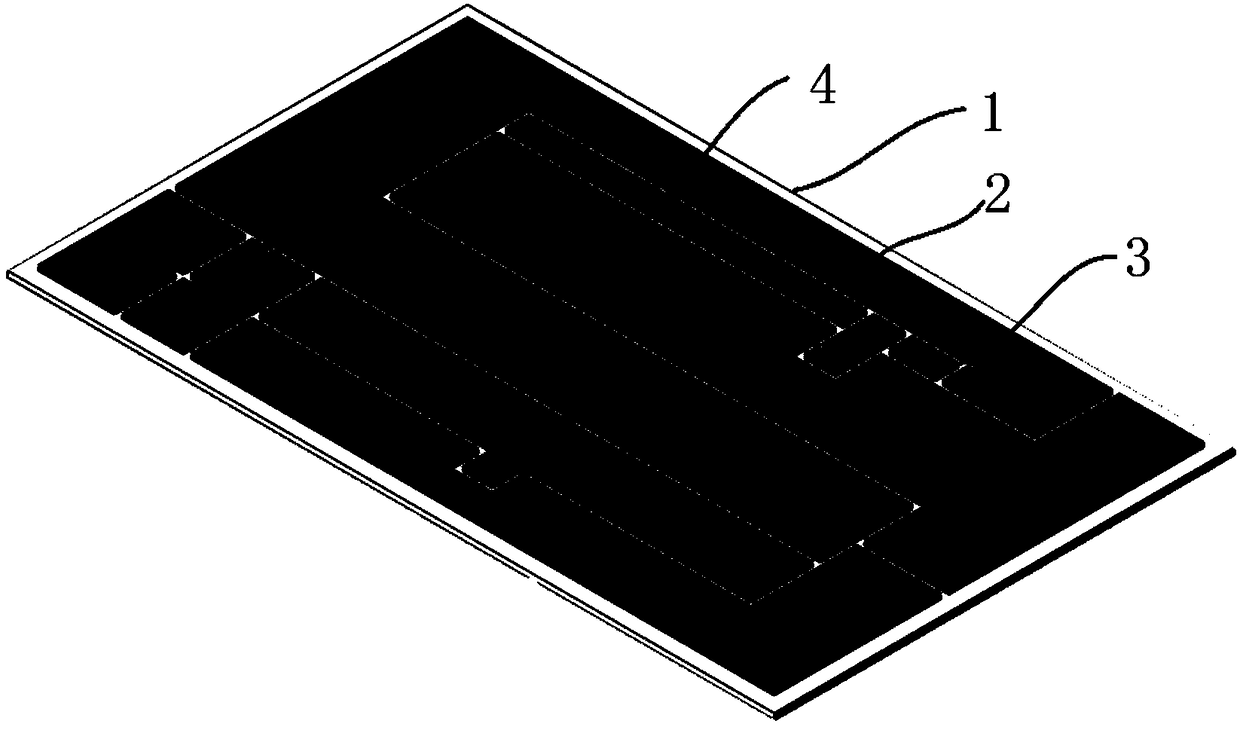

Method of etching surface layer portion of silicon wafer and method of analyzing metal contamination of silicon wafer

ActiveUS20120077290A1Rapidly and uniformly etchRate of reactionSemiconductor/solid-state device testing/measurementPreparing sample for investigationMetal contaminationVapor phase

An aspect of the present invention relates to a method of etching a surface layer portion of a silicon wafer comprising: positioning the silicon wafer within a sealed vessel containing a mixed acid A of hydrofluoric acid and sulfuric acid so that the silicon wafer is not in contact with mixed acid A; introducing a solution B in the form of nitric acid containing nitrogen oxides into the sealed vessel and causing solution B to mix with mixed acid A; and vapor phase decomposing the surface layer portion of the silicon wafer within the sealed vessel within which mixed acid A and solution B have been mixed.

Owner:SUMCO CORP

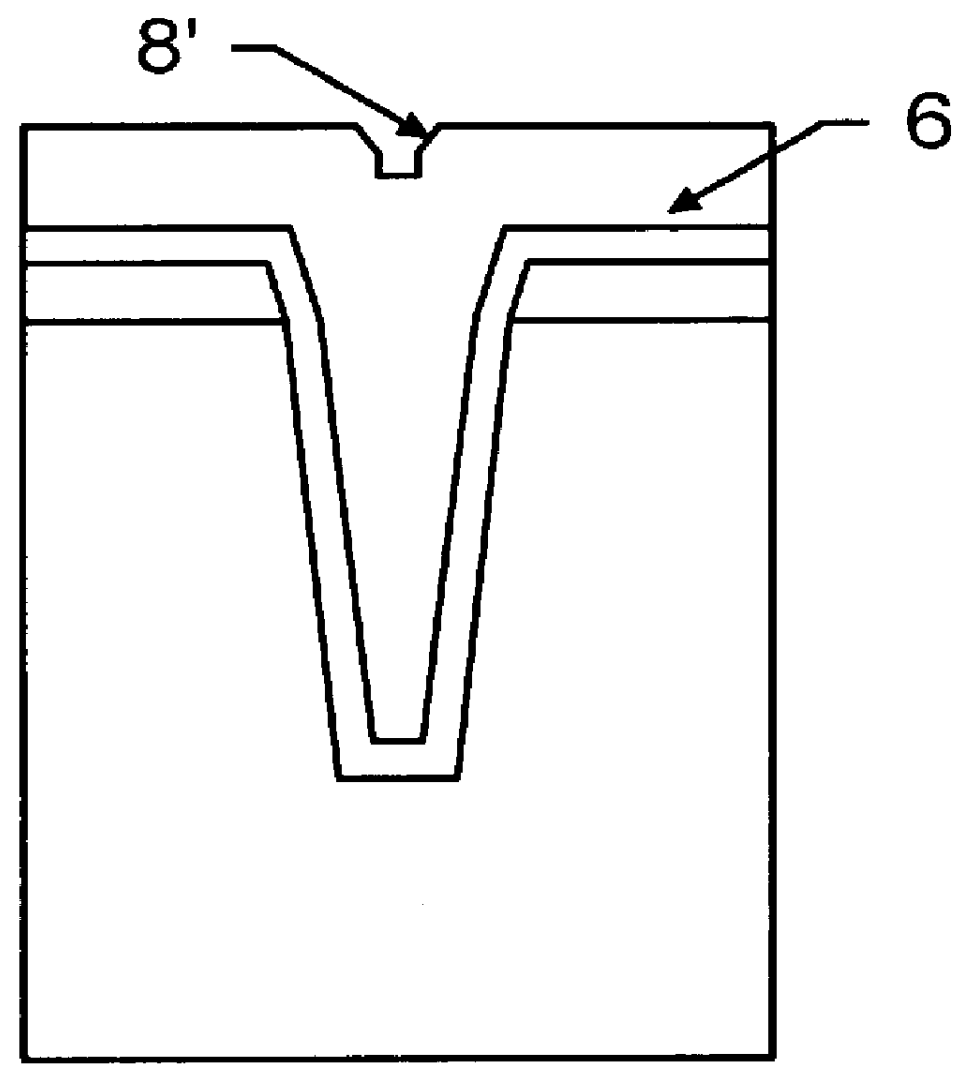

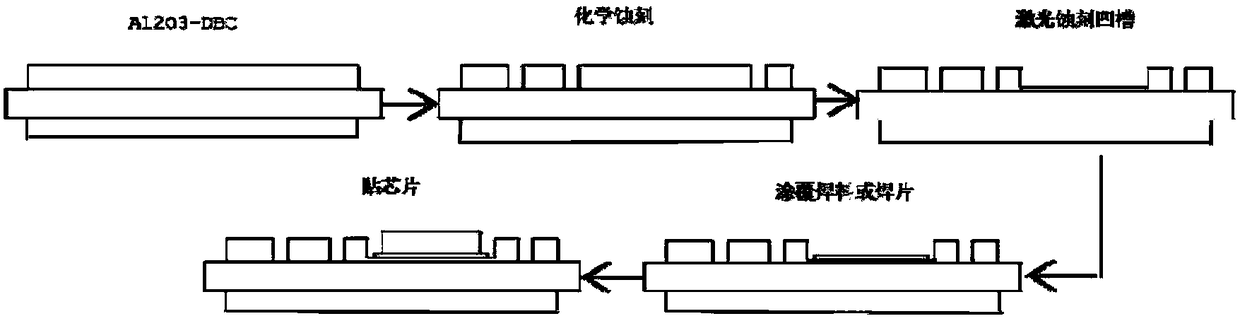

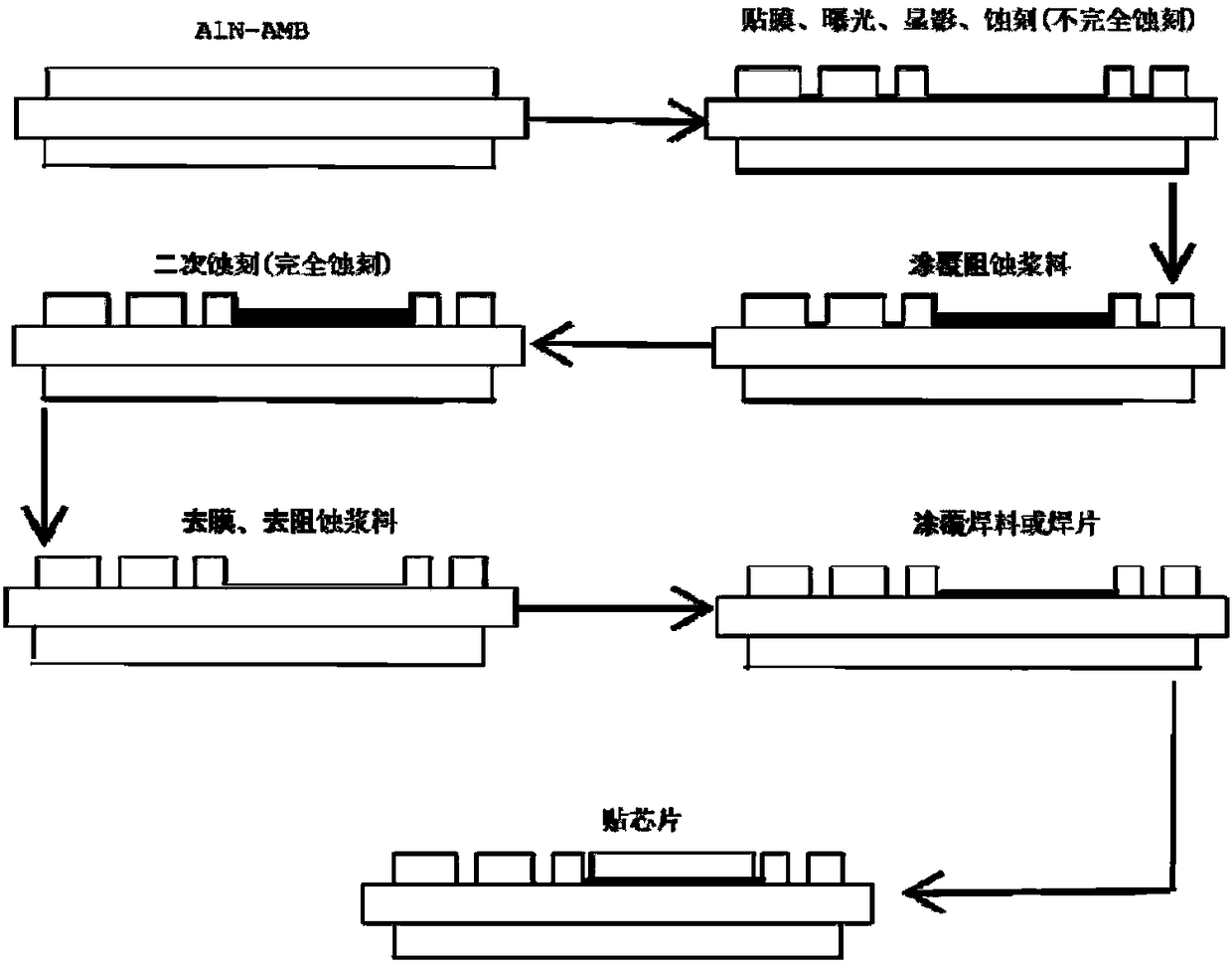

Metalized ceramic substrate, substrate manufacturing method and substrate and chip welding method

PendingCN108615717AFast etchEtching precisionSemiconductor/solid-state device detailsSolid-state devicesThermal expansionInternal stress

The invention discloses a metalized ceramic substrate, a substrate manufacturing method and a substrate and chip welding method, belongs to the field of a semiconductor device, and specify to the problem of failure of a power electronic device caused by a cracking phenomenon between a chip and a metalized layer, and falling off or cracking of the chip due to frequent impact of cold and hot changesof environment temperature on the metalized ceramic substrate in the prior art. The invention provides the metalized ceramic substrate, the substrate manufacturing method and the substrate and chip welding method; the metalized ceramic substrate comprises a ceramic substrate; a metal layer is arranged on one or two surfaces of the ceramic substrate; a circuit is arranged on the metal layer; a chip groove is formed in a metal layer chip mounting position; and the chip is welded on the chip groove of the manufactured metalized ceramic substrate through a brazing technique. By virtue of the method, internal stress caused by mismatch of thermal expansion coefficients between the metal layer and the chip can be lowered as far as possible, and product reliability is improved.

Owner:井敏

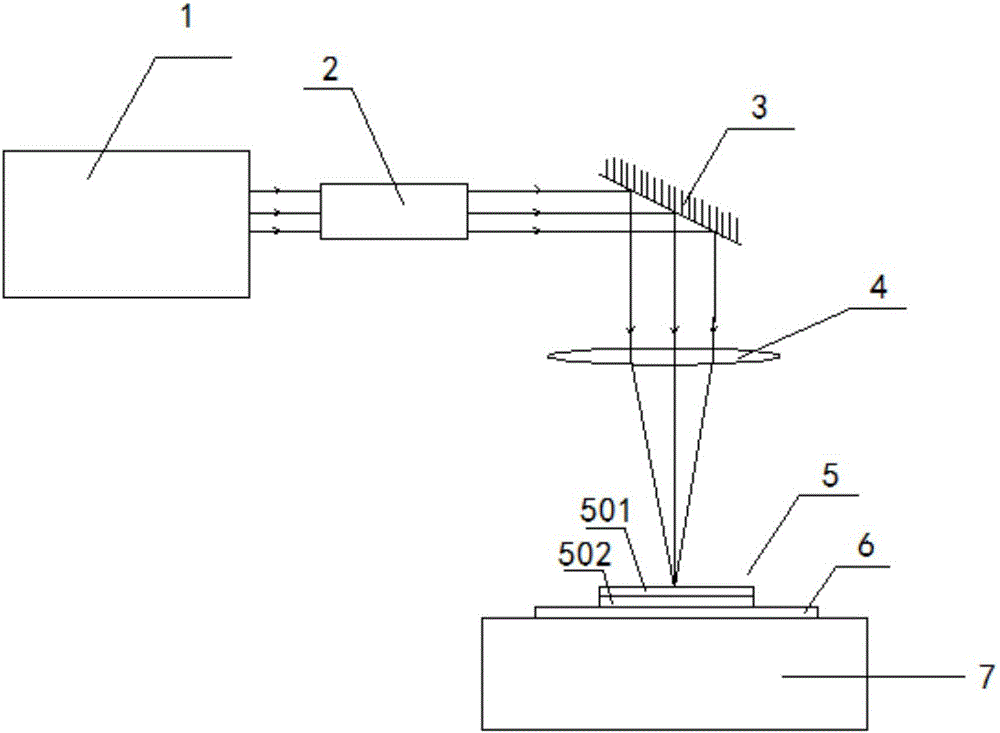

Laser etching method and system for RFID tag antenna

ActiveCN106425108ANeat edgesImprove machining accuracyLaser beam welding apparatusLaser etchingTag antenna

The invention relates to the technical field of laser antenna etching, in particular to a laser etching method for an RFID tag antenna and a system for implementing the method. The system comprises a laser, a beam expanding mirror, a galvanometer, a focusing lens, cooling equipment and a worktable; a tag antenna to be machined is placed on the cooling equipment; a plastic layer at the bottom of the RFID tag antenna to be machined is in close contact with the cooling equipment; the RFID tag antenna to be machined and the cooling equipment are fixed to the worktable together through a clamp; a laser beam which is output by the laser is expanded through the beam expanding mirror, is deflected through the galvanometer, is finally focused through the focusing lens and acts on an aluminium foil plating layer on the upper surface of the tag antenna to be machined. A non-woven fabric water absorbing pad is arranged at the bottom of the RFID tag antenna, so that the machining temperature of the plastic layer is effectively reduced, the plastic layer is prevented from being molten, and a laser etching technology can be applied to the field of RFID tag antennae.

Owner:深圳华工新能源装备有限公司