Method of etching surface layer portion of silicon wafer and method of analyzing metal contamination of silicon wafer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

example 1

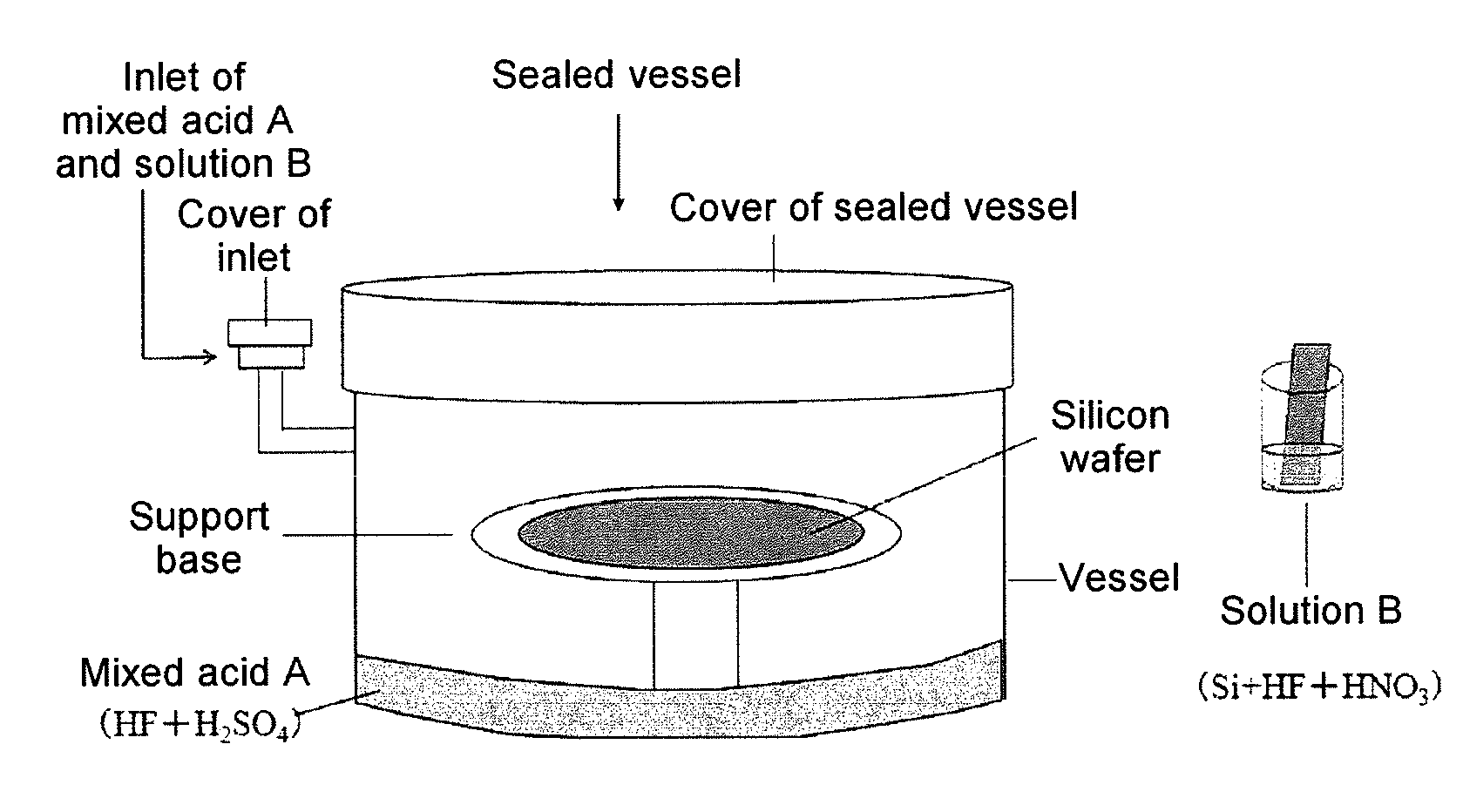

[0063]To the vessel shown in FIG. 1 (30 cm in diameter×15 cm in height, made of polyvinyl chloride) was charged a mixed acid comprising 500 g of hydrofluoric acid (EL grade 50 percent) and 200 g of sulfuric acid (EL grade 98 percent). A silicon wafer 200 mm in diameter with top and bottom surfaces that had been processed to mirror finishes was then positioned on a support base made of PTFE, and the cover was installed to seal the vessel. The vessel was left standing for five minutes to allow the mixed acid to generate HF.

[0064]Separately from the above operation, a 0.3 g piece of silicon (L×W×H: 10 cm×5 cm×0.07 cm) was dissolved by immersion for two minutes in a mixed acid comprising 90 g of nitric acid (EL grade 68 percent) and 10 g of hydrofluoric acid (EL grade 50 percent) in a 250 mL beaker (8 cm in diameter).

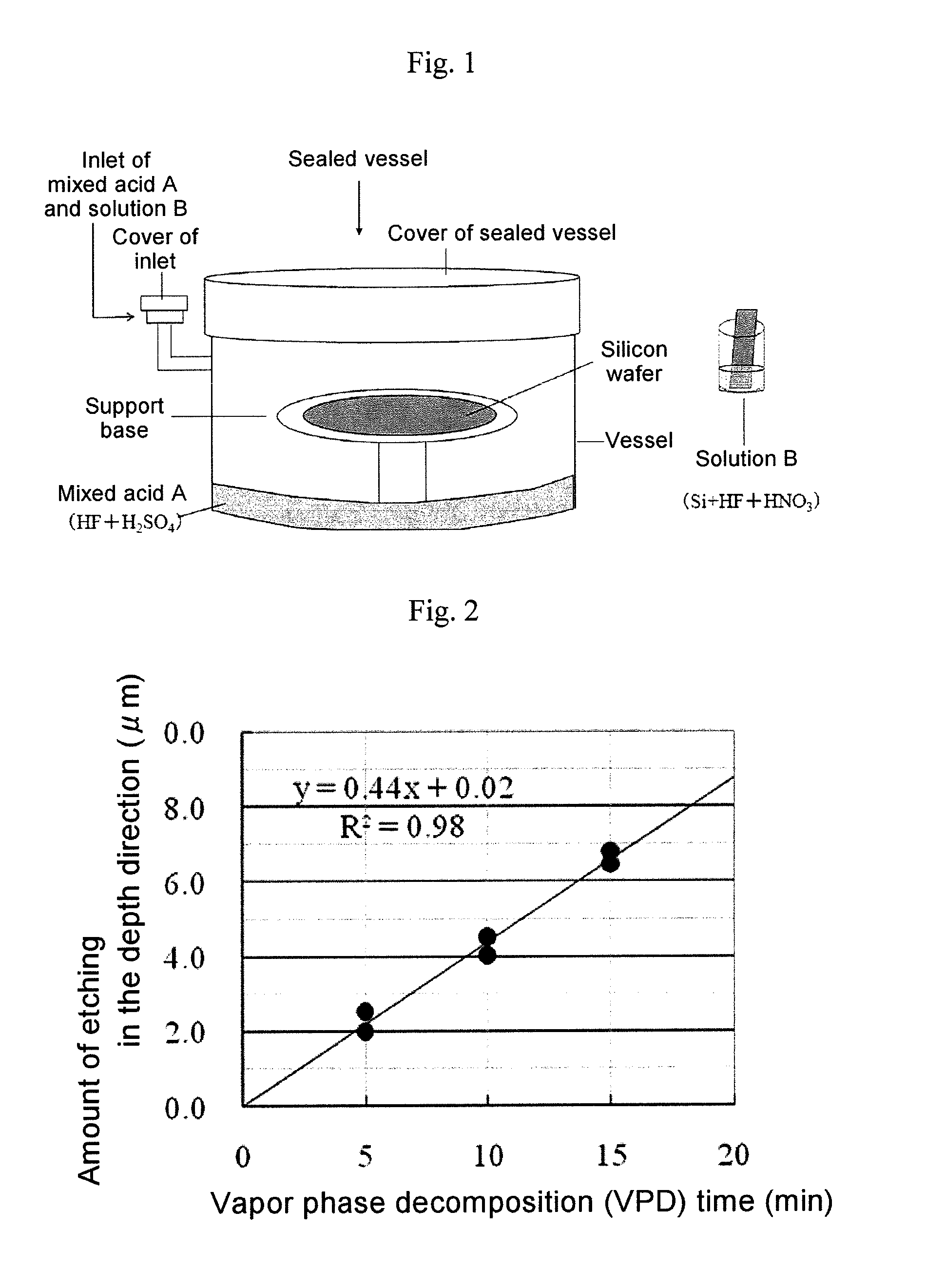

[0065]Next, the solution in the beaker was introduced into the sealed vessel through a tube via an inlet provided in the lateral surface of the vessel. Subsequently, the la...

example 2

[0071]A silicon wafer 200 mm in diameter with surfaces processed to mirror finishes that had been contaminated by spin coating with a quantity of Mo of about 1E+13 atoms / cm2 was annealed for 90 minutes at 950° C. in a nitrogen atmosphere and then cleaned with hydrofluoric acid. Subsequently, it was subjected to five cycles of vapor phase etching by the same method as in Example 1. With the completion of each cycle of vapor phase etching, the cover was removed from the sealed vessel, the silicon wafer was removed, 100 μl of an acidic collection liquid comprising 5 percent hydrofluoric acid / 10 percent hydrochloric acid / 5 percent hydrogen peroxide solution was applied dropwise to the surface of the etched wafer, the liquid was scanned over the entire surface of the wafer, and the metal impurities were collected. The collected solution was mixed with 1,000 μl of ultrapure water, and quantitative evaluation of Mo was conducted by high-sensitivity double-focusing ICP-MS.

[0072]FIG. 7 gives...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More