Gamma-boron synchronous diffusion process mesa structure thyristor chip and manufacturing process thereof

A technology of synchronous diffusion and mesa structure, applied in the direction of thyristor, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of large lateral resistance in short base region, slow turn-on speed, long high temperature diffusion time, etc., to save production costs, The effect of high lateral resistance and short diffusion time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

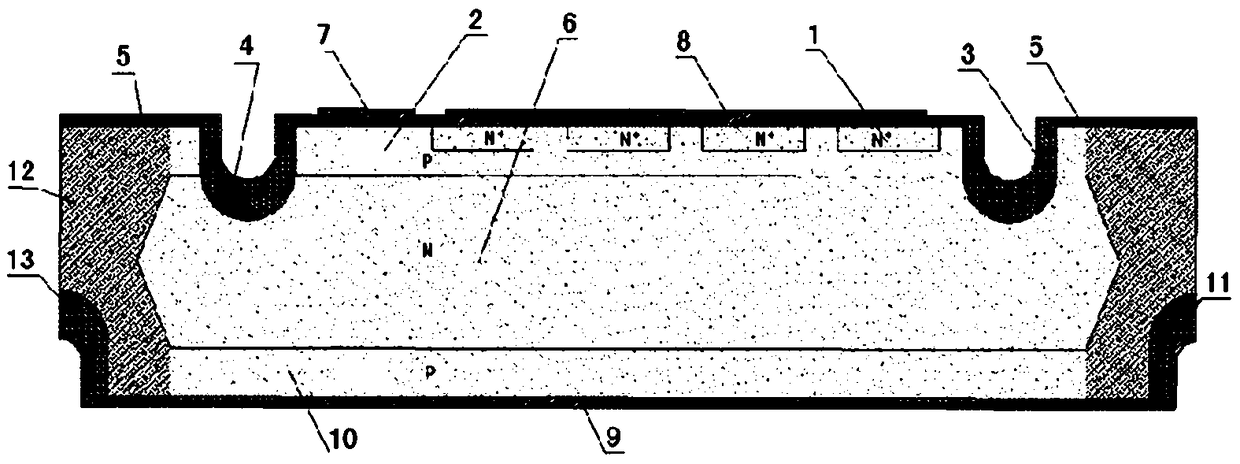

[0027] A gallium boron synchronous diffusion process mesa structure thyristor chip, the chip includes N + Type cathode region 1, front P-type short base region 2, silicon single wafer 6 (silicon single crystal intrinsic region), back P-type region 10, two ends of the chip are provided with isolation diffusion regions 12, and the front surface of the chip is provided with SiO 2 The protective film 5 is provided with a metal electrode 9 on the back surface, and the front P-type short base area 2 on the front of the chip is provided with a front trench 4, and the back side is provided with a back stress balance groove 13 in the communication isolation diffusion area 12, and a back stress balance groove 13 is provided in the front trench. A glass passivation film is provided, a glass film is provided in the back stress balance groove, a gate aluminum electrode 7 and a cathode aluminum electrode 8 are provided between the front grooves 4, and a cathode aluminum electrode 8 is provi...

Embodiment 2

[0039] A gallium boron synchronous diffusion process mesa structure thyristor chip, the chip includes N + Type cathode area 1, front P-type short base area 2, silicon single wafer 6 (silicon single crystal intrinsic area), back P-type area 10, two ends of the chip are provided with isolation diffusion areas 12, and the front surface of the chip is provided with SiO 2 The protective film 5 is provided with a metal electrode 9 on the back surface, and the front P-type short base area 2 on the front of the chip is provided with a front trench 4, and the back is provided with a back stress balance groove 13 in the communication isolation diffusion area 12, and the front trench is provided with a back stress balance groove 13. A glass passivation film is provided, a glass film is provided in the back stress balance groove, a gate aluminum electrode 7 and a cathode aluminum electrode 8 are provided between the front grooves 4, and a cathode aluminum electrode 8 is provided below the...

Embodiment 3

[0051] A gallium boron synchronous diffusion process mesa structure thyristor chip, the chip includes N + Type cathode area 1, front P-type short base area 2, silicon single wafer 6 (silicon single crystal intrinsic area), back P-type area 10, two ends of the chip are provided with isolation diffusion areas 12, and the front surface of the chip is provided with SiO 2 The protective film 5 is provided with a metal electrode 9 on the back surface, and the front P-type short base area 2 on the front of the chip is provided with a front trench 4, and the back is provided with a back stress balance groove 13 in the communication isolation diffusion area 12, and the front trench is provided with a back stress balance groove 13. A glass passivation film is provided, a glass film is provided in the back stress balance groove, a gate aluminum electrode 7 and a cathode aluminum electrode 8 are provided between the front grooves 4, and a cathode aluminum electrode 8 is provided below the...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Resistance | aaaaa | aaaaa |

| Resistance | aaaaa | aaaaa |

| Resistance | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More